前程往事,历历在目 - 佚名

一、基本概念

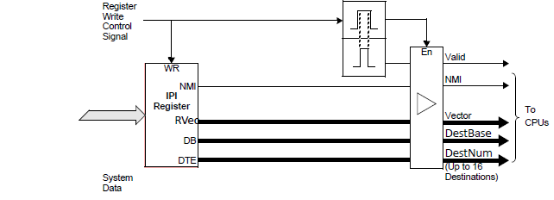

IPI 全称为Inter-Processor Interrupt,即处理中间的中断,需要可编程中断控制器PIC or APIC的支持!

操作流程大概如下:

需要向IPI 控制寄存器中写入需要recv interrupt vector,写入的IDB代表了类似IRT Entry的ID,最多可以广播16个硬件处理线程!DTE可以设置硬件处理线程的掩码,支持NMI!

二、实例描述

1、应用场景描述

以XLP3XX为示例,来对IPI进行简单了解。

XLP3xx支持160个IRT ENTRY,

即160个64 Bit的IRT寄存器!

Pcie 访问地址问bus 0,device 0,function 4 + 0x40000(EFCG_BASE)

支持8个128 Bit 位的ITE 寄存器!

2、和普通中断的的区别是什么?

说到普通中断

首先我们来回顾一下中断类型!

从原理上可以划分为:硬中断和软中断

从类型上可以划分为:可屏蔽中断,不可屏蔽中断,共享中断

这里我们所说的中断一般指的是一个中断线对应一个硬件处理线程,除了共享中断!

所谓共享中断从硬件角度上其实就是一根中断线被复用了,所以可以对应多个硬件处理线程!

然后IRT触发后的信号被多个硬件所使用!也就是说这一点必须需要硬件支持!

上述简单的说了一下基本中断类型!

如需要了解更多关于中断的信息!请查看

而我们的核间中断则是一个硬件线程去中断另外一个硬件线程!

3、优点是什么?

避免CPU线程的浪费,很大限度上将有效的控制CPU硬件线程,发挥SMP多核处理的优势!

4、简单示例

request_irq(TEST_IRQ,handler_test,0,”ipi_test”,NULL);

int ipi_trigger(unsigned int dst)

{

unsigned int reg_value;

unsigned int volatile *pic_base_addr = 0x18040100;

pic_base_addr -= 0x40; //对齐

reg_value = (1 << dst) | (dst / 16 << 16) | (TEST_IRQ << 20);

*(pic_base_addr + 0x4e) |= reg_value;

}

By: Keven - 点滴积累

1779

1779

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?