一、电子设计系统的面积优化与速度优化

1、资源优化:

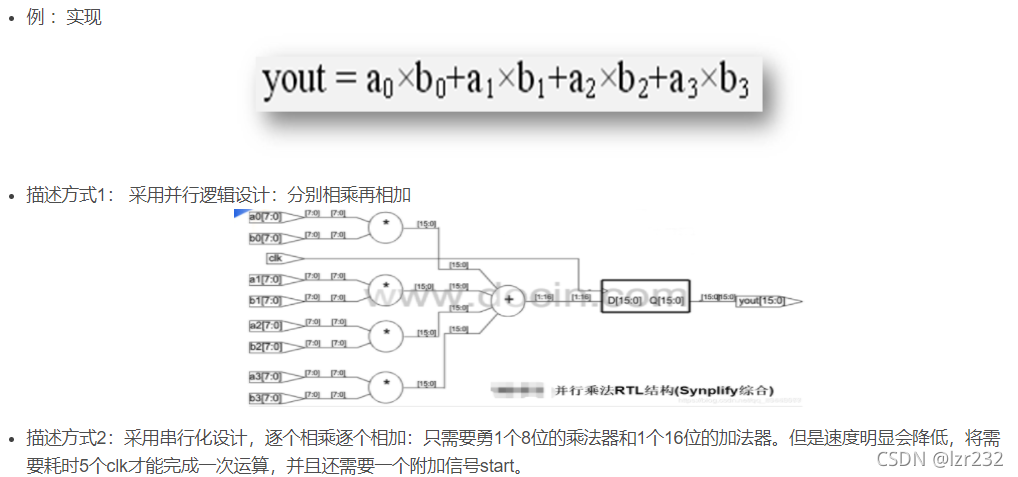

①资源共享:针对数据通路中耗费逻辑资源较多的模块,通过选择、复用的方式共享使用该模块,达到减少资源使用、优化面积的目的;

②逻辑优化:使用优化后的逻辑进行设计,可以明显减少资源的占用;

③串行化:将原来耗用资源巨大、单时钟周期内完成的并行执行的逻辑块分割开,提取出相同的逻辑模块(一般为组合逻辑块),在时间上利用该逻辑模块,用多个时钟周期完成相同的功能,其代价是工作速度被大为降低。

2、速度优化

①流水线设计:复杂组合逻辑之间添加寄存器的方法,是最常用的速度优化技术之一。它能显著地提高设计电路的运行速度上限。

②寄存器配平 (Register Balancing):寄存器配平是使较长路径缩短,较短路径加长,使其达到平衡从而提高工作频率的一种技术。

③关键路径法

关键路径:指设计中从输入到输出经过的延时最长的逻辑路径。优化关键路径是提高设计工作速度的有效方法。

④乒乓操作法

乒乓操作法是FPGA开发中的一种数据缓冲优化设计技术,可视作另一种形式的流水线技术。乒乓操作本质是使用2倍的硬件资源,通过将数据产生时间和数据使用时间重叠,解决一个数据生产效率低于数据使用效率的问题。是一种拿面积换性能的方法。通过“输入数据流选择单元”和“输出数据流选择单元”按节拍、相互配合的切换,将经过缓冲的数据流“无缝”地送到“数据流运算处理模块。

⑤树形结构法

若要实现A+B+C+D。首先实现AB=A+B,CD=C+D,将AB/CD锁存一个时钟周期再相加。树形结构法和上面面积优化提到的串行化是相反的。

本文为CSDN博主「风中少年01」的原创文章,有删减和修订

原文链接:https://blog.csdn.net/qq_26652069/article/details/100634180

1159

1159

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?