单总线概述

- 单总线是美国DALLAS公司推出的外围串行扩展总线技术。与SPI、I²C串行数据通信方式不同,它采用单根信号线传输。 这种协议由一个总线主节点、或多个从节点组成系统,通过根信号线对从芯片进行数据的读取。每一个符合OneWire协议的从芯片都有一个唯一的地址,包括48位的序列号、8位的家族代码和8位的CRC代码。主芯片根据64位寻址对各个芯片进行双向通信,因此其协议对时序的要求较严格,初始化、写bit或读bit都有严格的时序要求,但是位于位之间没有严格要求。

- 单总线的数据传输速率一般为16.3Kbit/s,最大可达142 Kbit/s,通常情况下采用100Kbit/s以下的速率传输数据。主设备I/O口可直接驱动200m范围内的从设备,经过扩展后可达1km范围。

- 这种传输方式信号线上既传输时钟又传输数据,而且数据传输是双向的,具有节省I/O口线、资源结构简单、成本低廉、便于总线扩展和维护等诸多优点。

单总线应用

目前,单总线器件主要有数字温度传感器(如DS18B20)、A/D转换器(如DS2450)、门标、身份识别器(如DS1990A)、单总线控制器(如DS1WM)等。

单总线硬件结构

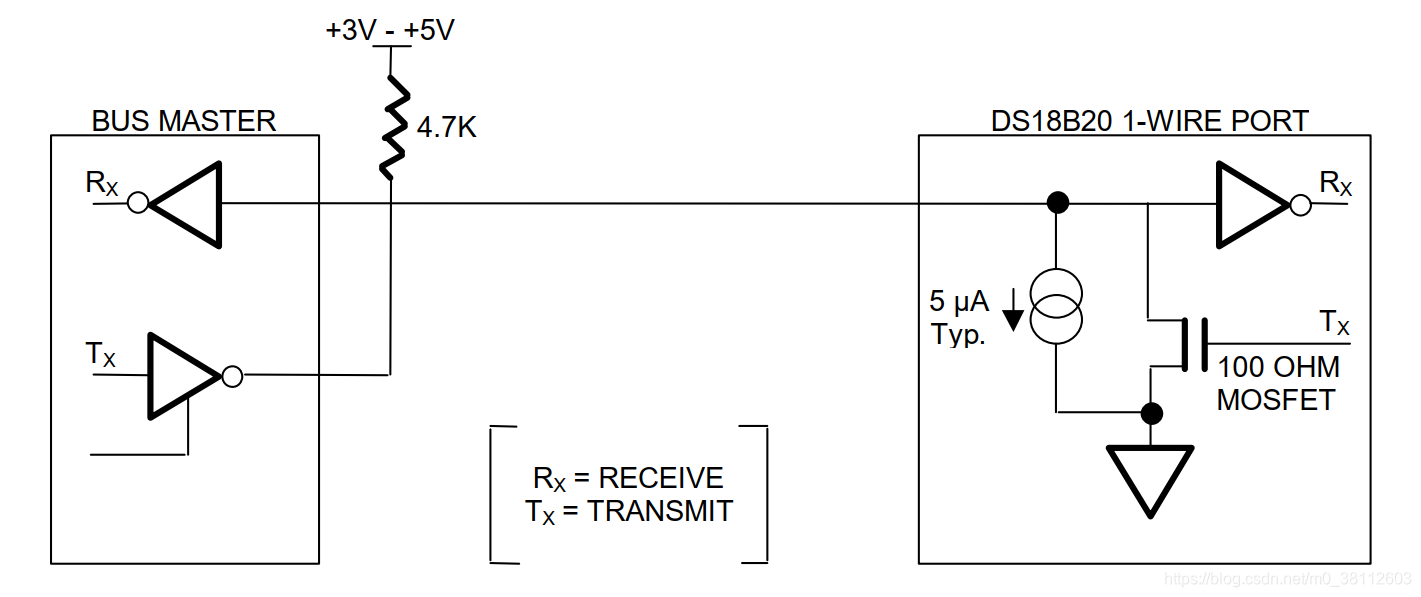

单总线即只有一根数据线:重要的是每一个挂在总线上的器件都能在适当的时间驱动它。每次每一个总线上的器件都必须是漏极开路或三态输出。下面是以DS18B20为例的结构图。

单总线的空闲状态为高电平。无论任何理由需要暂停某一执行过程时,如果还行恢复执行的话,总线必须停留在空闲状态。在恢复器件如果单总线处于高电平,位于位间的恢复时间可以无限长。如果总线停留在低电平超过480us,总线上的所有器件都将被复位。

单总线的空闲状态为高电平。无论任何理由需要暂停某一执行过程时,如果还行恢复执行的话,总线必须停留在空闲状态。在恢复器件如果单总线处于高电平,位于位间的恢复时间可以无限长。如果总线停留在低电平超过480us,总线上的所有器件都将被复位。

单总线通信原理

由于单总线是主从结构,只有主机呼叫从机时,从机才能应答,因此主机访问器件都必须严格遵循单总线命令序列,即初始化、ROM命令和功能命令。如果出现序列混乱,器件将不响应主机(搜索ROM命令、报警搜索命令除外)。单总线通信步骤如下:

- 初始化

- ROM操作命令

- 存储器操作命令

- 执行/数据

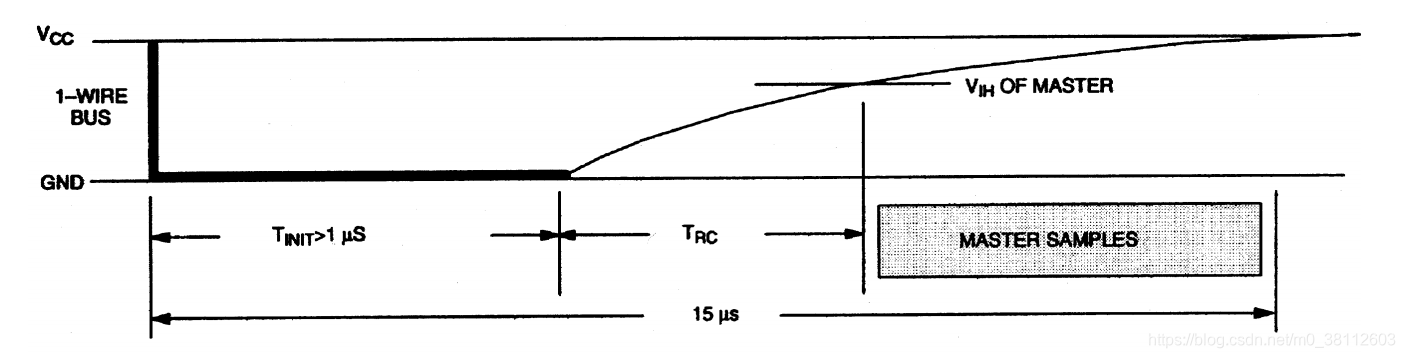

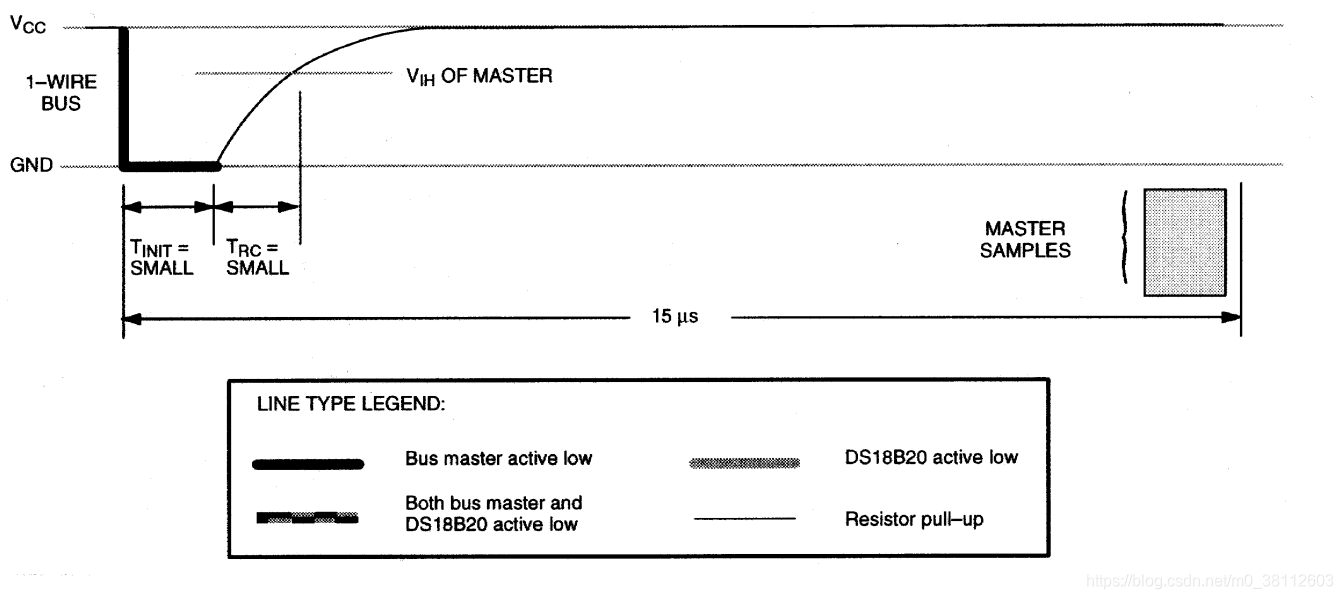

单总线通信时序

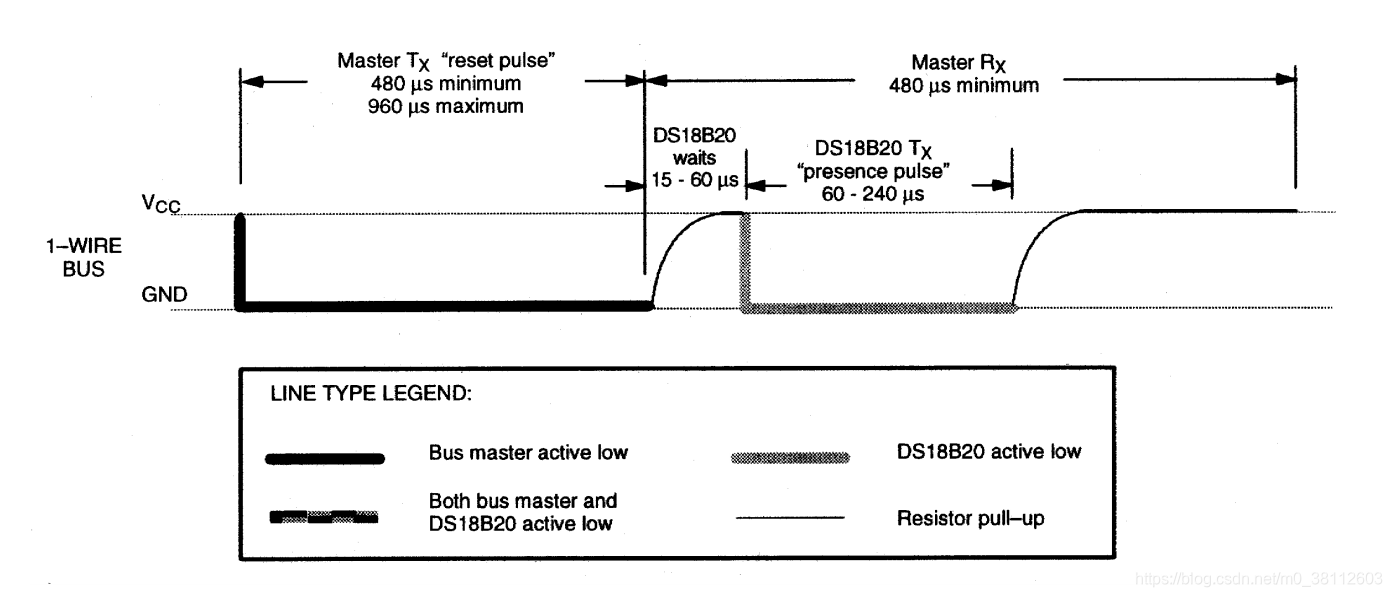

- 初始化

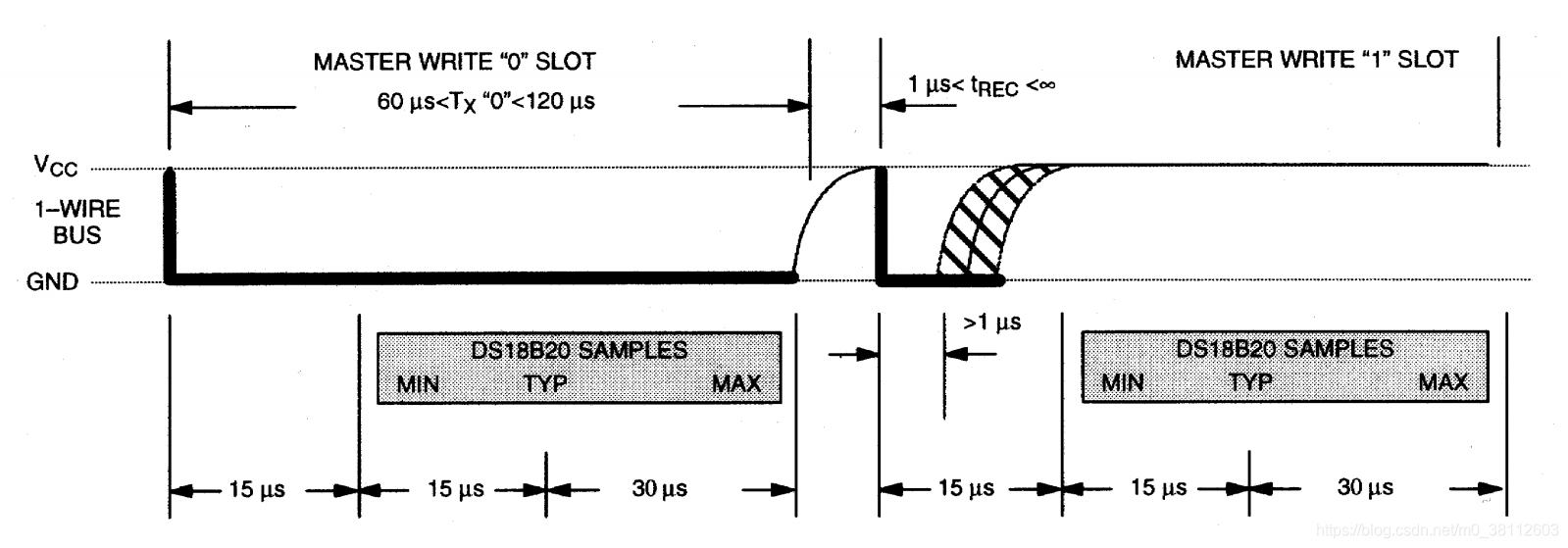

- 写时序图

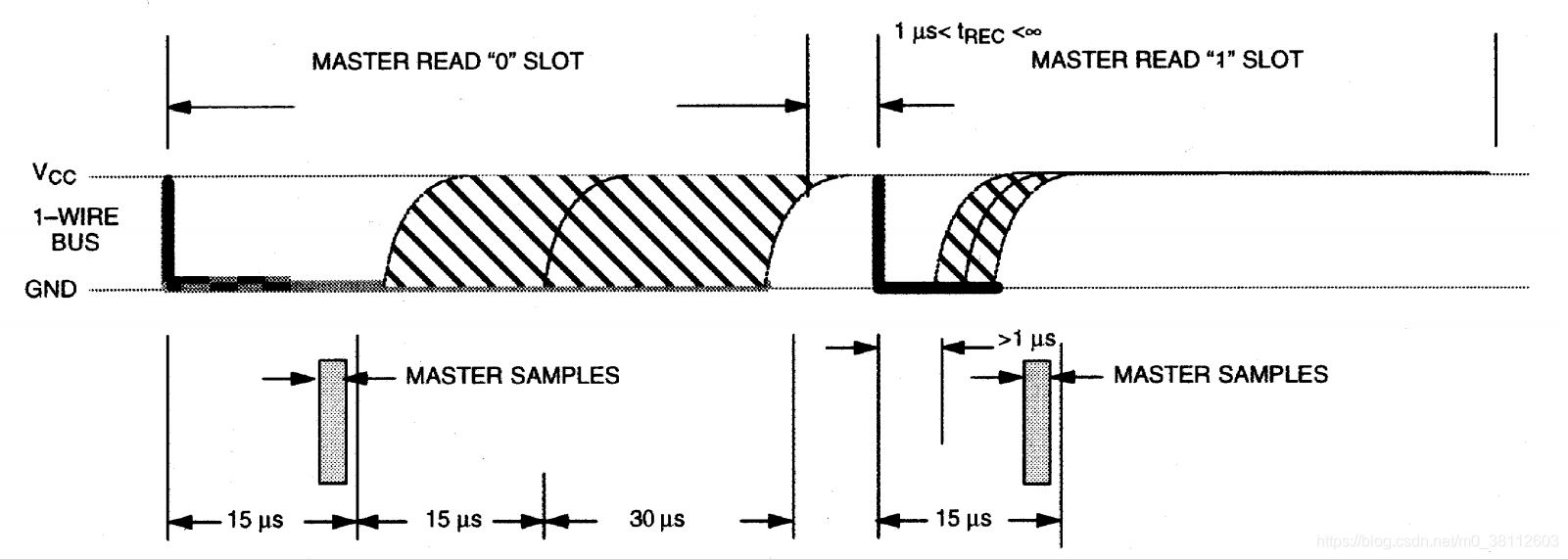

- 读时序图

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?