要求

设计一款基于FPGA的芯片信号发生器,利用Verilog语言实现信号发生器的各个模块单元,实现正弦波、三角波、方波等;

整体步骤如下:

-

需求分析:

- 确定所需的信号类型:正弦波、方波、三角波等。

- 确定信号的频率范围和精度要求。

- 确定输出端口的接口标准和电平要求。

-

选择FPGA:

- 根据需求选择合适的FPGA芯片,考虑到需要的逻辑资源、DSP资源、存储资源等。

-

设计逻辑电路:

- 根据信号类型和频率要求设计适当的数学模型和逻辑电路。对于正弦波,可以采用DDS(直接数字频率合成)技术;对于方波和三角波,可以使用计数器和状态机等实现。

- 实现相应的控制逻辑,包括频率控制、相位控制、幅度控制等。

-

时钟和时序设计:

- 确定FPGA的时钟源,并设计时钟分频电路以生成所需的输出频率。

- 设计合适的时序电路,保证信号输出的稳定性和准确性。

-

模拟输出电路(可选):

- 如果需要模拟输出,设计模拟输出电路,将FPGA输出的数字信号转换为模拟信号。可以使用DAC芯片进行数字模拟转换。

-

编程实现:

- 使用硬件描述语言(如Verilog或VHDL)编写逻辑电路描述代码。

- 编写相应的约束文件以指定时序约束和引脚映射等。

- 进行综合、布局布线和生成比特流文件。

-

验证和调试:

- 使用仿真工具进行功能仿真,验证设计的正确性。

- 将比特流文件下载到目标FPGA芯片中,进行硬件验证。

- 调试和优化设计,确保满足性能和功能需求。

-

系统集成:

- 将信号发生器模块集成到目标系统中,与其他模块进行接口对接和调试。

- 验证整个系统的功能和性能。

-

生产和部署:

- 根据需求进行量产,生产所需数量的芯片。

- 部署到目标设备中,进行实际应用。

在设计过程中,需要考虑到时钟分辨率、数字信号与模拟信号的转换精度、功耗等因素,并根据实际应用场景进行合理的权衡和优化。

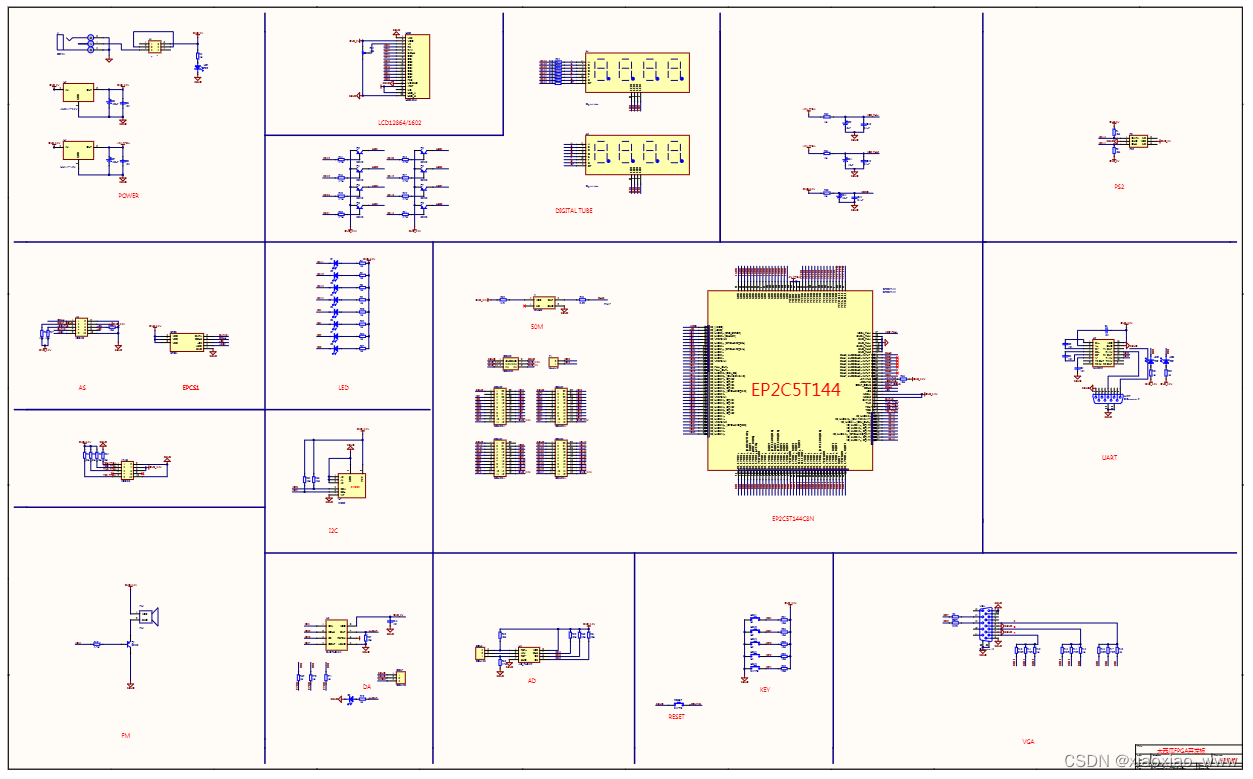

FPGA板原理图

FPGA板的原理图主要包括以下几个主要部分:

-

FPGA芯片:原理图应包含FPGA芯片及其相应的引脚连接。这些连接通常包括时钟输入、I/O端口、配置存储器等。确保正确连接FPGA与其他电路元件,如时钟源、外部存储器等。

-

时钟电路:包括时钟发生器、时钟分频器等,用于为FPGA提供时钟信号。时钟电路的设计需要考虑到时钟频率、稳定性、相位噪声等因素。

-

电源管理电路:负责为FPGA及其周边电路提供稳定的电源。这包括电源滤波电路、稳压电路、电源管理芯片等。

-

外部存储器接口:如果需要外部存储器来存储FPGA的配置文件或数据,原理图中应包含相应的存储器接口电路,如SPI Flash、SDRAM等。

-

通信接口:如果FPGA需要与其他设备进行通信,如UART、SPI、I2C等,原理图中应包含相应的通信接口电路。

-

输入/输出接口:用于连接外部设备和传感器的输入/输出接口,如GPIO、模拟输入、数字输入等。

-

调试接口:原理图中可能包含用于调试和测试的接口,如JTAG接口。

-

外部器件:除了FPGA芯片外,原理图还应包含连接到FPGA的外部器件,如LED、按钮、开关等。

-

电源指示灯和其他指示灯:用于指示系统状态的LED指示灯。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5423

5423

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?