核心模块

基于FPGA的序列检测器通常需要几个核心模块来实现其功能。这些模块可以根据具体的设计需求和检测算法的复杂程度而变化,但是以下是一些通常需要的模块:

(1)输入模块:负责接收外部数据流并将其送入FPGA内部。这可以是串行输入模块(如接收串行数据流的串行收发器)或并行输入模块(如外部并行接口)。

(2)序列匹配逻辑:这是检测器的核心模块,负责匹配输入数据流中的序列模式。这通常涉及状态机、比较器和逻辑电路来实现。根据应用需求,这个模块可能需要支持不同长度和类型的序列。

(3)计数器模块:用于跟踪输入数据流中序列的出现次数或其他统计信息。这对于某些应用来说是必要的,例如统计序列在输入流中的频率或在一段时间内的平均速率等。

(4)输出模块:负责向外部报告检测到的序列模式,可能通过LED、UART、SPI、I2C或其他通信接口向外部设备发送信息。

(5)时钟管理模块:负责生成或接收FPGA内部时钟信号,并确保所有模块都在正确的时序下运行。

(6)配置和控制模块:用于配置序列检测器的参数和控制其行为。这可能包括设置序列模式、调整匹配算法参数以及启用/禁用检测器等功能。

(7)时序和约束模块:用于定义FPGA设计中的时序约束,以确保设计在目标时钟频率下正确运行,并且满足性能要求。

(8)状态机控制器:用于管理序列检测器的状态机,以确保正确的序列匹配和状态转换。

这些模块可以根据特定的设计需求进行组合和调整。我们可能还需要考虑添加其他功能模块,如错误检测和纠正、数据缓冲、中断控制等,以满足特定的应用需求。

序列产生模块

序列产生模块是基于FPGA的序列检测器中的一个重要组成部分,它负责生成要检测的序列模式。以下是实现序列产生模块的一般步骤:

-

确定序列模式:首先,确定您想要检测的序列模式。这可能是一个固定的位模式、字节序列、或者更复杂的序列模式。

-

设计产生逻辑:设计一种逻辑电路来生成所需的序列模式。这可能包括使用计数器、状态机或其他逻辑电路来生成模式中的每个位。

-

实现产生逻辑:使用硬件描述语言(Verilog或VHDL)编写代码,描述产生序列模式所需的逻辑。这将涉及到将序列模式转换为硬件逻辑的过程。

-

时序控制:确保产生的序列模式的时序满足要求。这可能涉及到时钟分频、延迟控制等技术,以确保生成的序列模式与输入数据流同步。

-

仿真验证:使用仿真工具验证产生模块的功能,确保它按照预期工作。这有助于发现和解决设计中的问题,同时减少在实际硬件上调试的时间。

-

优化与改进:根据仿真结果进行优化和改进,确保产生模块的性能和正确性。

-

集成到序列检测器中:将产生模块集成到序列检测器的整体设计中,以生成要检测的序列模式,并将其输入到序列匹配逻辑中进行检测。

红色框内为序列产生的代码,产生的序列为“11100101”

序列检测模块

序列检测模块是基于FPGA的序列检测器中的核心部分,负责在输入数据流中检测特定的序列模式。下面是一个实现序列检测模块的一般步骤:

-

确定检测序列:首先,确定想要在输入数据流中检测的序列模式。这可能是一个固定的位模式、字节序列,或者更复杂的序列模式。

-

设计匹配逻辑:设计一种逻辑电路来在输入数据流中匹配所需的序列模式。通常采用状态机或滑动窗口比较等技术来实现。

-

实现匹配逻辑:使用硬件描述语言(Verilog或VHDL)编写代码,描述检测序列的匹配逻辑。这可能涉及到状态机的设计、比较器的实现等。

-

时序控制:确保匹配逻辑的时序满足要求。这可能涉及时钟同步、数据同步等技术,以确保检测模块能够正确地处理输入数据流。

-

匹配条件处理:确定匹配条件,并在检测到序列模式时生成相应的输出信号。这可能包括生成中断、标志位或其他控制信号。

-

仿真验证:使用仿真工具验证检测模块的功能,确保它按照预期工作。通过仿真可以发现和解决设计中的问题,提高设计的可靠性和性能。

-

优化与改进:根据仿真结果进行优化和改进,确保检测模块的性能和正确性。可能需要调整匹配逻辑以提高匹配速度或减少资源消耗。

-

集成到整体设计中:将检测模块集成到序列检测器的整体设计中,与其他模块(如输入模块、输出模块等)进行连接和协调。

-

验证和调试:在实际硬件上验证和调试序列检测器的功能,确保它能够在实际环境中正确工作。

(1)为一个一个位的检测。

(2)为对检测正确的序列进行计数,计算正确的序列,然后用于显示在数码。

输出正确结果,1111 为正确,0000 为错误。

数码显示模块

数码显示模块是基于FPGA的电子系统中的常见组件,用于将数字信息以数码形式显示出来。这种显示通常用于显示数字、字母、符号等信息,如在数字钟、计数器、仪表等应用中。以下是实现数码显示模块的一般步骤:

-

选择数码显示器:选择适合您应用需求的数码显示器,这可能包括七段数码管、数码管阵列、LED显示器等。根据需要选择合适的显示器类型和尺寸。

-

设计驱动逻辑:设计一种逻辑电路来驱动选定的数码显示器,以根据输入的数字信息显示相应的内容。这通常涉及到将数字转换为适合数码显示器的格式,并控制显示器的开启和关闭。

-

实现驱动逻辑:使用硬件描述语言(Verilog或VHDL)编写代码,描述驱动数码显示器的逻辑。这可能包括生成数码显示器所需的控制信号、时序控制等。

-

数码编码器:如果您的输入数据不是直接适合于数码显示器的格式(如BCD码、ASCII码等),则可能需要设计一个数码编码器来将输入数据转换为数码显示器可接受的格式。

-

时序控制:确保驱动逻辑的时序满足数码显示器的要求。这可能涉及到时钟同步、时钟分频、数据同步等技术,以确保显示器的稳定显示。

-

仿真验证:使用仿真工具验证驱动逻辑的功能,确保它能够正确地将输入的数字信息显示在数码显示器上。

-

优化与改进:根据仿真结果进行优化和改进,确保驱动逻辑的性能和正确性。可能需要调整时序控制以提高显示效果或减少资源消耗。

-

集成到整体设计中:将数码显示模块集成到整体FPGA设计中,与其他模块进行连接和协调,以实现完整的电子系统功能。

-

验证和调试:在实际硬件上验证和调试数码显示模块的功能,确保它能够在实际应用中正确地显示数字信息。

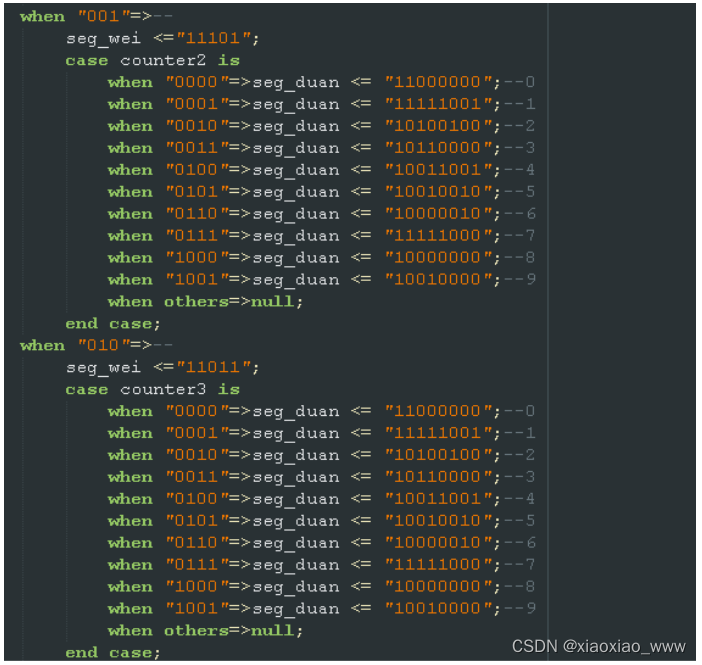

数码管的位扫描信号的产生代码

为三位数码管的显示,显示检测正确的序列数

顶层设计模块

顶层设计模块是基于FPGA的数字系统中的核心组件,它负责整合各个功能模块,定义系统的总体结构和功能。下面是顶层设计模块的一般内容和功能:

-

模块接口定义:定义系统的输入和输出接口,以及与外部系统或设备的接口。这包括确定数据输入输出的格式、时钟接口、控制信号等。

-

功能模块实例化:将系统中的各个功能模块实例化并连接起来。这包括将序列检测模块、数码显示模块、接口模块等按照设计需求加以连接。

-

时钟管理:定义系统的时钟结构,包括主时钟的来源和分配,以及各个模块的时钟域划分。确保时钟的稳定和同步是设计中的重要部分。

-

状态机设计:如果系统需要具备状态机控制的功能,设计状态机的状态转移逻辑,并定义状态变化时的操作和控制信号。

-

数据通路设计:定义数据在系统内部的传输路径和处理流程。这可能包括数据的调度、处理、缓存、转换等操作。

-

配置和控制逻辑:设计配置和控制系统各个模块的逻辑。这可能包括状态的切换、模块使能和禁用、参数配置等。

-

异常处理:设计系统对于异常情况的处理逻辑,包括错误检测、错误处理、恢复机制等。

-

时序分析和约束:进行时序分析,并定义时序约束以确保系统在目标时钟频率下能够正确运行。

-

仿真验证:通过仿真工具验证顶层设计的功能和性能。这有助于发现和解决设计中的问题,并确保设计的正确性和可靠性。

-

综合与实现:使用FPGA厂商提供的综合工具将顶层设计综合成可在目标FPGA上实现的逻辑,并生成比特流文件。

-

测试与调试:将生成的比特流文件加载到FPGA上,并通过实际硬件测试验证设计的功能和性能。在测试过程中可能需要进行一些调试,以确保系统的正确运行。

-

文档和部署:撰写设计文档,记录系统的总体结构、功能和性能特征,并部署设计到目标系统中。

用于连接以上三个模块的信号,然后输出到引脚上。

技术难点

-

高速数据处理:在高速数据流中实时检测序列模式需要高效的数据处理能力。设计必须考虑到FPGA资源的限制,同时保证足够的处理速度来满足应用需求。

-

状态机设计:序列检测器通常涉及状态机的设计和实现。这要求设计者能够准确地定义状态转移逻辑,并确保状态机能够正确地响应输入数据的变化。

-

匹配算法优化:设计一个高效的匹配算法来检测输入数据流中的序列模式是一个挑战。这需要综合考虑匹配算法的复杂度、资源消耗以及匹配速度等因素。

-

时序分析和时序约束:在高速数据流中进行序列检测要求严格的时序控制。设计者需要进行时序分析,并定义合适的时序约束,以确保设计在目标时钟频率下能够正确运行。

-

资源优化:FPGA资源有限,因此需要对设计进行资源优化,尽可能地减少资源消耗,同时保证设计的功能和性能。

-

输入数据流同步:确保输入数据流和系统时钟的同步是一个关键问题。设计者需要考虑输入数据的时序特性,采取合适的同步技术,以确保数据的准确性和稳定性。

-

抖动和噪声处理:在实际应用中,输入数据流可能会受到抖动和噪声的影响,这可能会导致误检测或漏检测。设计者需要采取合适的技术来处理抖动和噪声,提高系统的鲁棒性和可靠性。

-

动态重配置:一些应用可能需要动态地改变序列模式或检测参数。设计一个能够支持动态重配置的序列检测器是一个挑战,需要考虑到设计的灵活性和性能损耗之间的平衡。

1128

1128

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?