- 专业术语:

(1)125MSps:表示的ADC的采样速率(conversion rate)表示一秒钟采集到的点数最大是125M;

(2)对于AD9653来说:输入被采样的模拟信号的时钟范围为20M~1000MHz;

(3)AD9653采用LVDS接口输出需要采集到的模拟信号的数字量;

(4)DCO:ADC的数据采集时钟;在高电平进行采样;

(5)FCO:ADC的帧同步时钟,为了同步每次采集到的数据帧(8bit每帧);

(6)采样时钟:采样时钟的时钟最大为125M;

(7)SPI端时钟信号最大为50M;

(8)ADC的前端输入电路:将需要采集的信号经过巴伦转换成差分信号输入到ADC采集模块,其中的巴伦主要是为了降低级联的噪声系数;

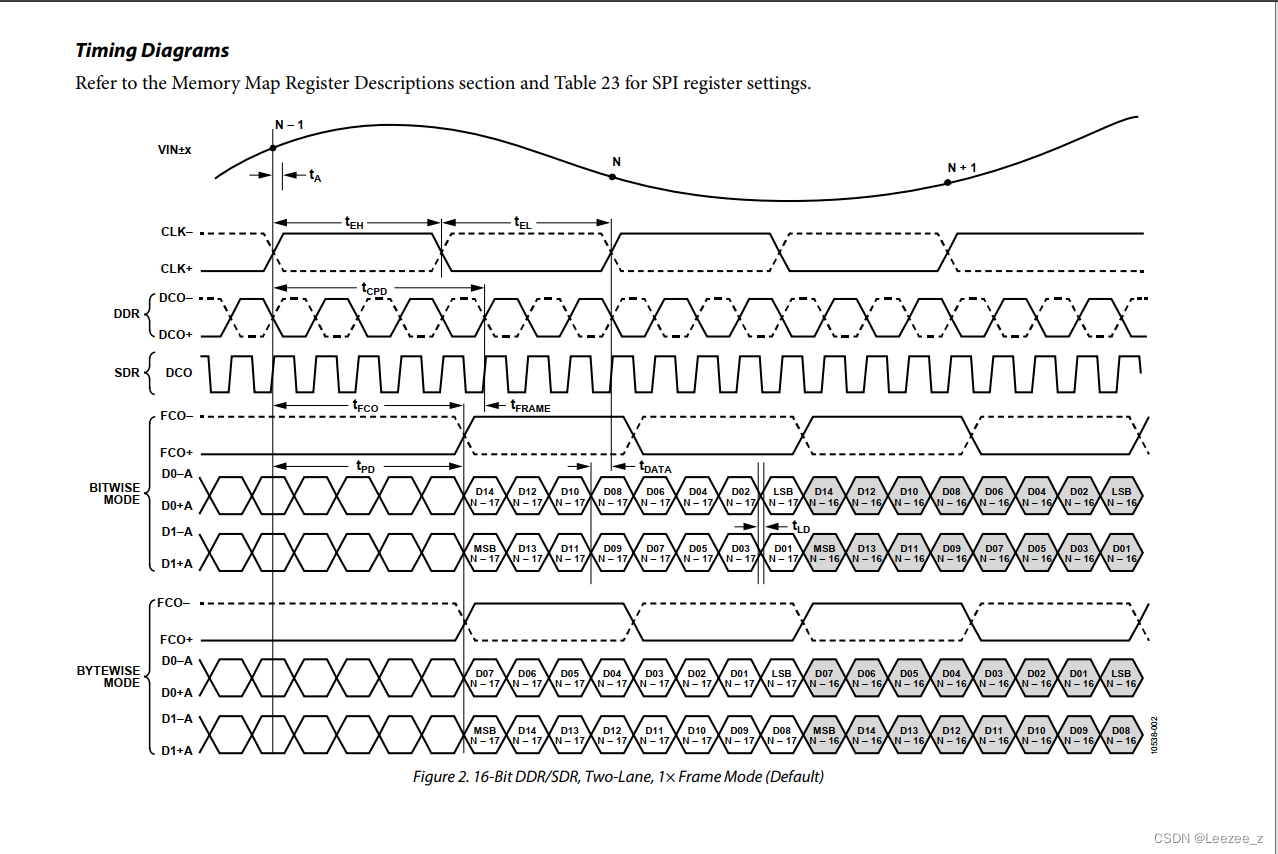

(9)按照下面时序图来分析,如果CLK(ADC的采样时钟:外部供给)的输入时钟信号为50M,在DDR模式下,对应的DCO的数据采集时钟为4*50=200M,帧同步输出时钟为50M;

(10)SERDES: SerDes是Serializer/Deserializer的缩写,即串行器和解串器,顾名思义是一种将并行数据转换成串行数据发送,将接收的串行数据转换成并行数据的”器件“。对于FPGA工程师来说“串并转换”再熟悉过不过了,只不过SerDes是一种需要数模硬件实现的,用于高速传输的“高级”串并转换器件。至于接口从最初从串口到并口,再回归到串口的历史发展,可以阅读相关的文献,借此可以了解一下系统同步、源同步的技术瓶颈。在未来高带宽、低成本的应用领域会越来越广泛。

高速接口SerDes为实现芯片间信号的有线传输,需要完成数字到模拟的转化,经过通道传输后,再将模拟信号转回数字信号。并保证传输过程保持比较低的误码率。

(11)AD9653采样过程: AD9653四路模拟信号进行数模转换,再分别将对应通道得到的16bit数据转换成2对串行差分信号(例如A通道的2对差分信号D0+A/D0-A,D1+A/D1-A),采用源同步的方式连同数据采集时钟(DCO+/-)和帧同步时钟(FCO+/-)一起传输给FPGA,在FPGA内部按照要求使用内置的SERDES收发器完成高速解串、数据对齐后得到采样的16bit并行数据进行后续的数据处理。但是按照时序图可以看出FCO+/-,DCO+/-,D0+/-,D1+/-之间存在固定的相位关系,解决办法是在硬件设计上保证各个信号的走线等长,这样对应的相位关系即可保证时钟所处相位的最佳采样点,但是由于时钟DCO作为串行数据、帧时钟的SERDES收发器的采样时钟,FPGA内部的走线延时将导致到达各个SERDES收发器相位与串行数据、帧时钟之间的相位关系发生变化,此时通过位时钟DCO对串行数据直接采样将会产生误码。为了解决这个问题,首先通过位时钟自适应调整模块调节位时钟的延迟,使得连接至各个ISERDES采样时钟的相位与输入的DCO+/-相互一致,此刻采样点处于串行数据位和帧时钟的中心采样点,为最佳的采样位置 。

(12)源语设计模块(vivado中源语打开:VIvado–Tools–Language Templates:点击搜索框搜索相应的源语)

(1)IBUFDS:差分输入缓冲器,将输入的低压差分信号转换成单端信号;

(2)OBUFDS:差分输出缓冲器,将输入的单端信号转换成低压差分信号;

(3)IDELAYE3:IDELAYE3是FPGA(现场可编程门阵列)设备中的一种延迟元件。它是专门设计来调整输入信号的定时,以满足数字系统中特定的定时要求。IDELAYE3可用于调整时钟信号或数据信号的相位,允许对数字电路的不同部分进行精确的同步。它通常用于高速通信系统,如以太网或PCI Express,其中,准确的定时对适当的数据传输至关重要。IDELAYE3块是XilinxFPGAs家族的一部分,并被用于他们的许多产品中。

(4)FPGA的I/O资源:7系列的FPGA中,BANK分为HR(High-range)BANK和HP(High-performance) BANK。

HP BANK只能支持小于等于1.8V电平标准的I/O信号,

HR BANK则支持小于等于3.3V电平标准的I/O信号。

HP BANK专为高速I/O信号设计,支持DCI(数控阻抗),

HR BANK则适合更大众化的所有I/O信号设计。

下表列出了HP BANK 和HR BANK的特性。

无论是HR或者HP BNANK,每个BANK都包含50个I/O管脚,每个I/O管脚都可配置成输入、输出。每个BANK的首尾管脚只能作为单端I/O,其余48个I/O则可配置成24对差分I/O。

(5)以VAR_LOAD模式下对于延时的输入配置;

(6)ISERDESE和OSERDESE:

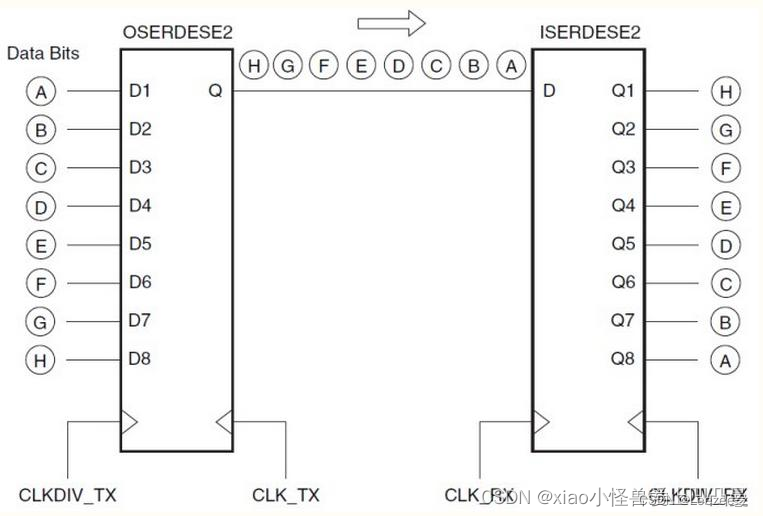

由上述可以看出:ISERDESE 为 Xilinx FPGA 中专用的解串器,主要用于数字传输中的串行转并行, 先到的比特为为高位。 OSERDESE2 为并行转串器,主要用于数字传输中的并行转串行,先到的比特为为高位。但是传输的时候需要将传输的bit按照原位解串或者并转串,这样传输的数据就会出现接收到的数据和发送的数据位的排序不一致,为了解决这个问题,有个专门的控制信号来调整高低位的排列顺序:Bitslip信号。

AD9653调试

于 2023-03-31 11:52:31 首次发布

1566

1566

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?