文章目录

DEMO1:在不下载bit stream的情况下,通过PS端把bit stream从DDR中加载到PL端。

一、vivado工程

示例:pandas 是基于NumPy 的一种工具,该工具是为了解决数据分析任务而创建的。

根据对应板卡的型号创建好空白工程

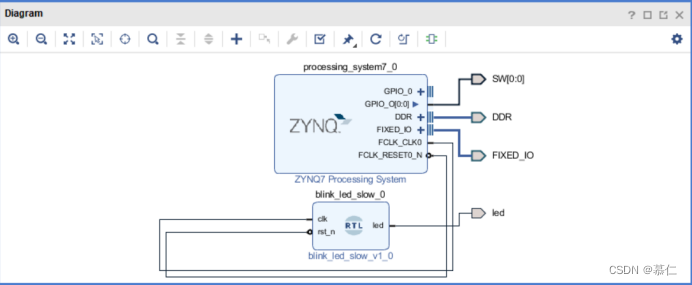

为了降低工程难度并能清楚看到实验效果,该工程只需要一个zynq的最小系统(ZYNQ+DDR+SD+UART)和一个LED闪烁模块

在这里插入图片描述

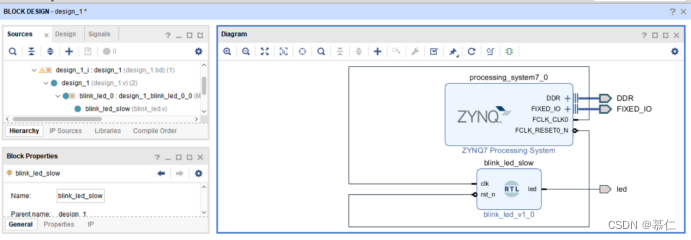

- 创建block design 添加zynq,根据板卡配置好DDR,SD和UART

- 使能一个PL端时钟和复位

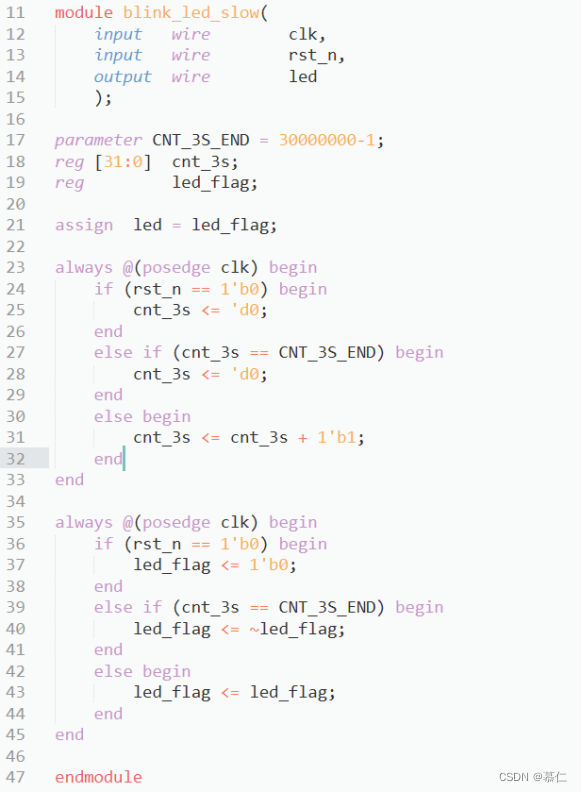

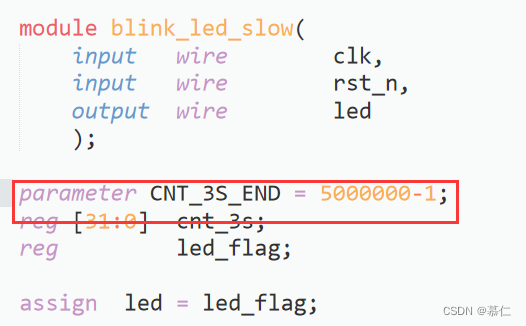

- 编写LED闪烁模块,这里写了一个3S一次LED慢闪烁模块(为了和后面的快闪烁区分)

- 将LED模块添加到bolck design 并与zynq相连

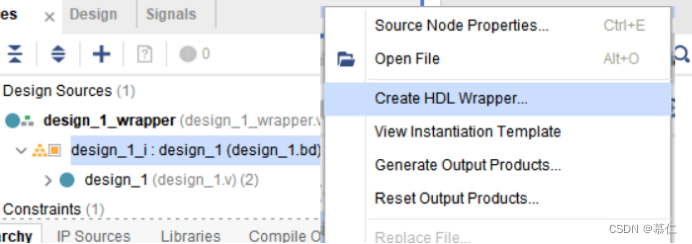

- 点击creat hdl wrapper

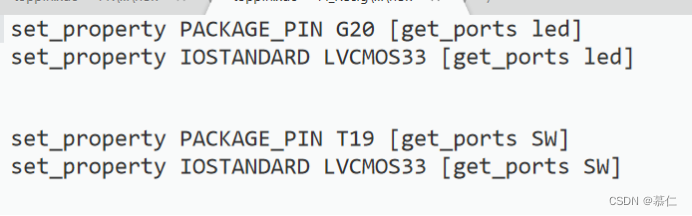

- LED是PL端的资源,创建约束文件,为其添加管脚约束

- 生成Bitstream后点击file -> Export -> Export Handware注意在Export Handware 界面勾选 Include Bitstream。

- 启动SDK,进入软件设计。点击file –> launch SDK

二、SDK工程

1.创建公错错错

- 菜单栏 File -> New -> Application Project,创建一个SDK应用工程。

- 按照提示设置工程名,注意不要直接finish,点击Next 在弹出界面选择 空工程, Empty Application

- 创建后SDK会创建一个name应用工程以及name_bsp的板级支持包(BSP)工程,且会自动编译生成name.elf文件

- 最后在name工程下的src文件夹添加相应的源文件和头文件进行下载验证即可

2.PS重构PL

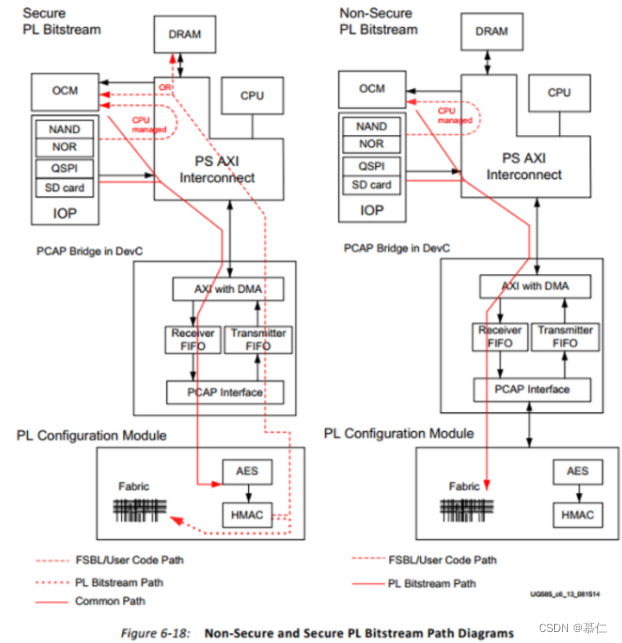

所谓重配置,即在当前硬件比特运行期间,有一份新的比特通过网络、串口等等其他方式传输到平台,平台将其存储在Falsh、DDR等外部存储介质中,随后将硬件在不断电的情况下配置成新的比特流。

对bitstream可以大致分为以下几种情况:

- Vivado下载:Program and debug –> Open Hardware Manager -> open target -> auto connect -> program device 在弹出界面选择bit文件下载即可

- 固定启动,来自外部存储设备,将比特流固化到存储介质,并选择相应的启动方式。

- 动态配置,即上述所说的不断电更新。数据来源一般是下图中的DRAM。

- 在搭建好硬件及软件环境后,要实现PS重配置PL我们需要2个条件,其一是两份不同表现的PL实现的Bin文件,其二是软件部分DEVC 的正确配置使用。

3.bin文件

加载需要的文件不支持.bit文件,需要将.bit 文件转换成.bin 文件

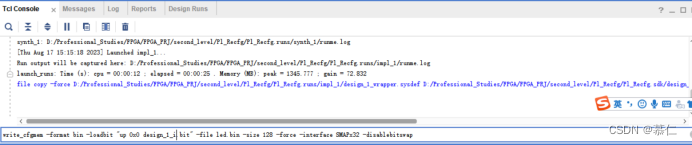

在生成bit stream 时直接生成的.bin 文件不能配置成功,需要用tcl 语言将.bit 文件转换成.bin文件:

write_cfgmem -format bin -loadbit "up 0x0 比特文件名.bit" -file 生成bin文件名.bin -size 128 -force -interface SMAPx32 -disablebitswap

-

在 tcl console 中输入命令:

-

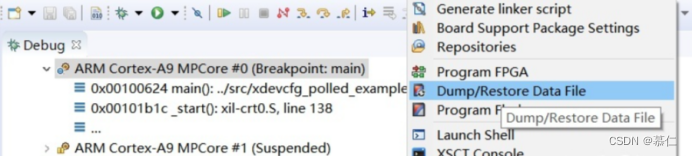

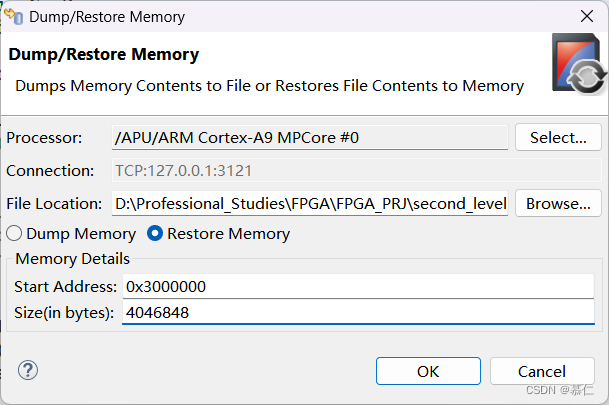

点击xilinx->Dump/Restore Date File

-

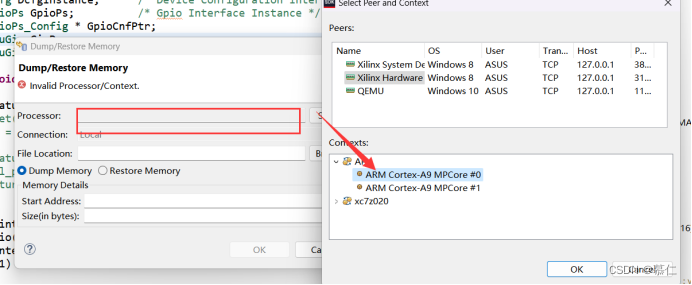

第一个框是选择对应的硬件设备(需要和板卡相连接)

-

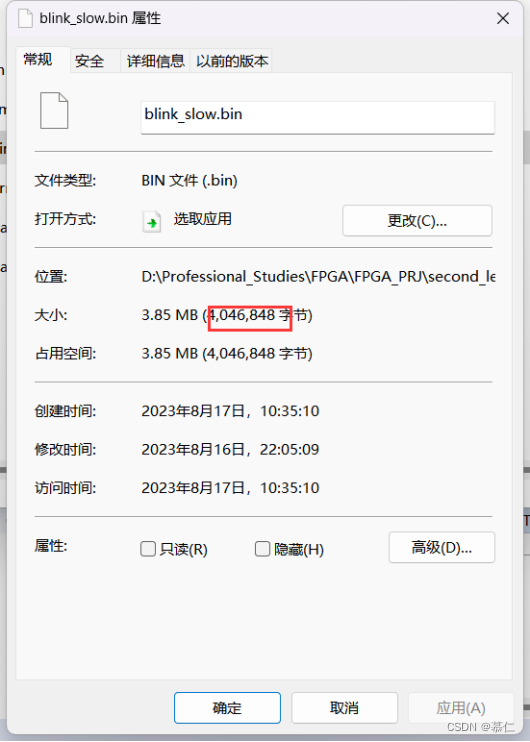

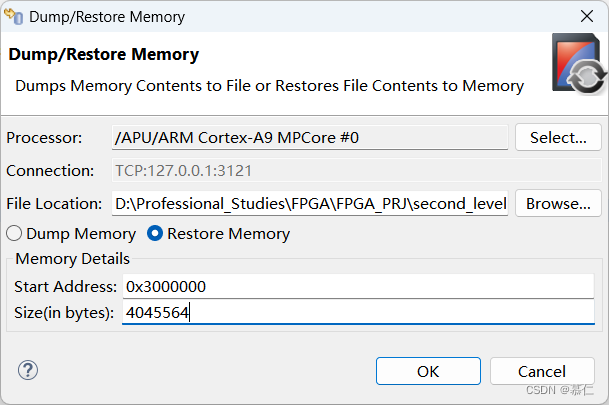

载入准备好的bin 文件,选择一个DDR起始地址,这里填入0x3000000(其他地址也行,但不能大于0x4000000),如果不是很清楚就填0x300000,size填入bin文件的字节长度,

-

bin文件的字节长度直接在文件的属性查看即可

4.代码

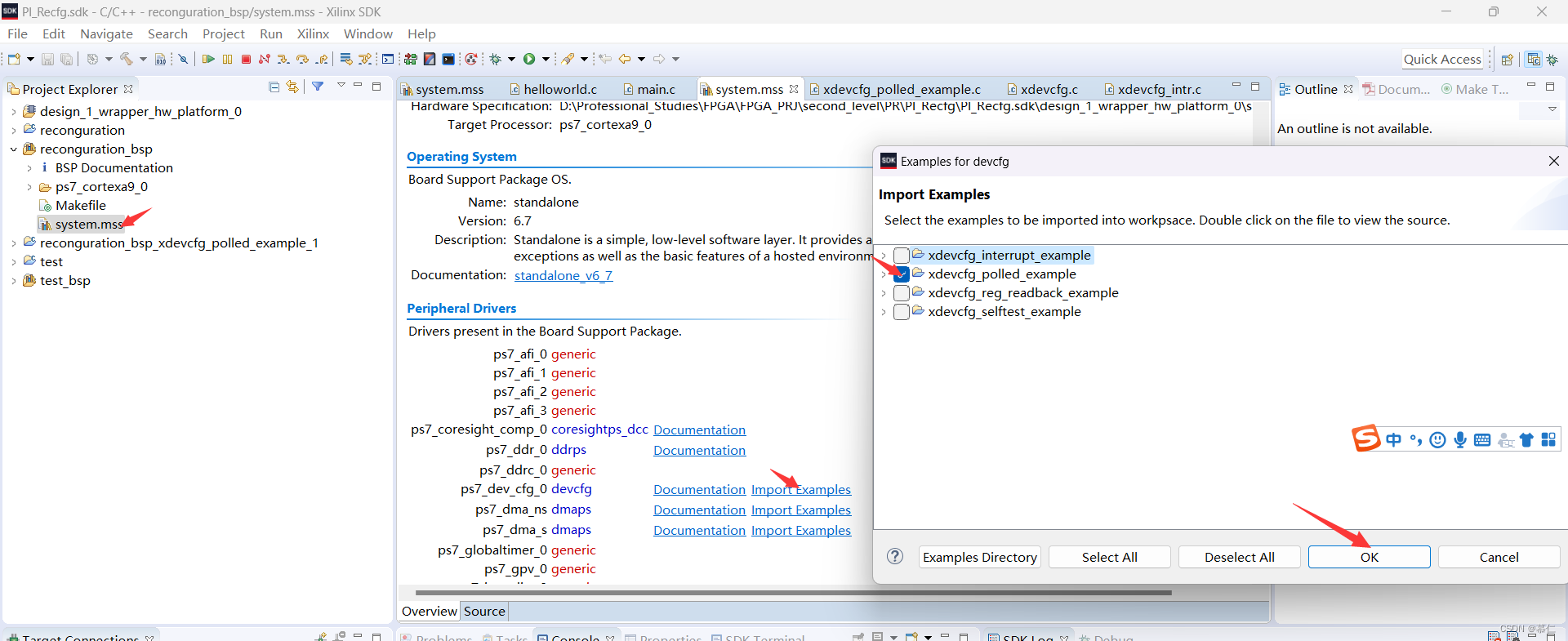

- 导入官方例程

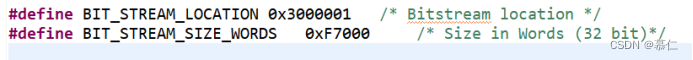

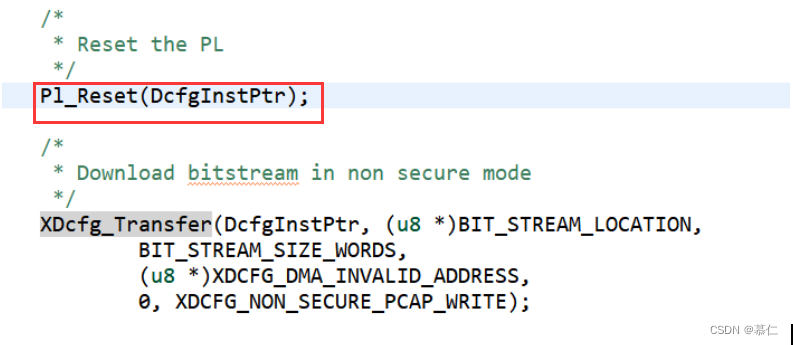

- 对于函数中的两个关键宏定义,BIT_STREAM_LOCATION为读取DDR的其实地址读取时从DDR地址0x3000001开始读取,这是因为最低 2bit == 2’b01 用来表示此时为最后一次 DMA 传输。BIT_STREAM_SIZE_WORD 的大小为bin文件字节数/4(其实只要大于这个值就行)

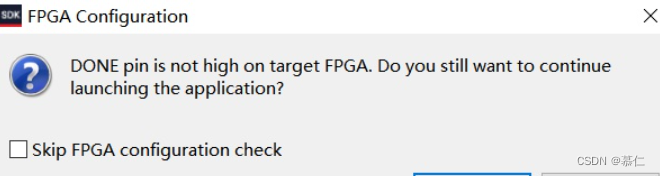

- 我们的程序运行时,此时 PL 部分还没有比特流,我们下载软件时就会提醒我们,此时硬件还未就绪(Done 信号未置起)

-

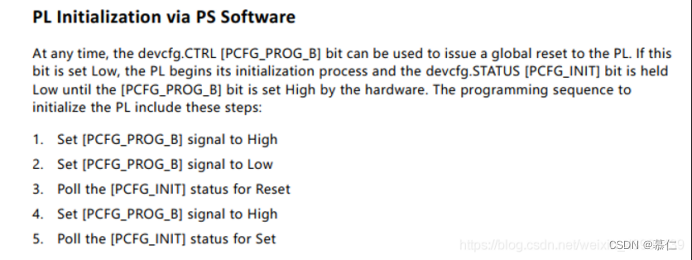

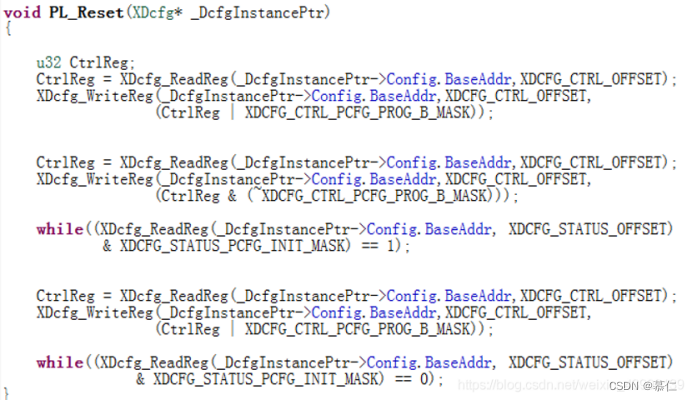

在配置硬件之前需要先复位硬件

-

PL_Reset函数需要在 XDC_Transfer()函数前调用,在加载前先对PL复位:

-

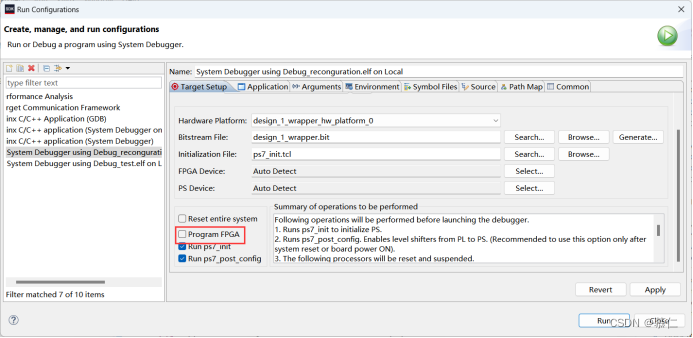

下载elf程序,注意不勾选program FPGA.

-

下载完成后,可以看到在没有program fpga的情况下,led开始闪烁,表明已经从DDR中加载了bin 文件。

DEMO2:通过按键切换加载两个不同的bit stream

-

为了引入按键,使能一位EMIO

-

加上管脚约束:

-

生成bit stream,并按照之前的方法转换为bin文件 ,命名为blink_slow.bin

-

修改led模块的参数,使得闪烁更快

-

生成bit stream,并按照之前的方法转换为bin文件 ,命名为blink_fast.bin

-

打开SDK,加入按键控制程序

-

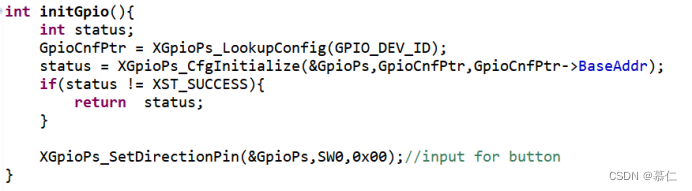

使能GPIO

-

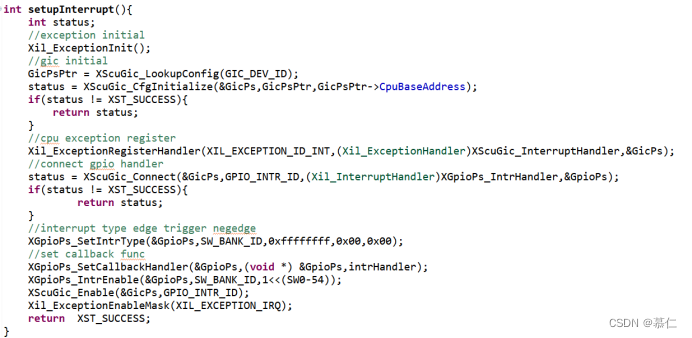

设置中断

-

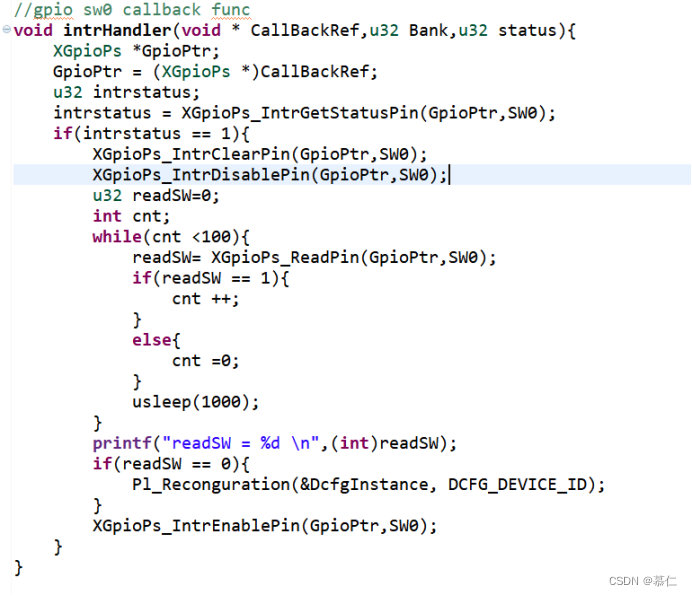

编写中断回调函数

-

将blink_fast.bin Restore Memory到DDR

-

下载程序,勾选program FPGA,可以看到led以比较慢的频率闪烁,按下按键,led以比较快的频率闪烁,PL重构成功!

-

例程代码:https://download.csdn.net/download/m0_46525532/88231877 spm=1001.2014.3001.5501

4823

4823

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?