VHDL中信号与变量的区别及赋值的讨论(对某位大佬的补充)

一 信号与变量的区别

变量声明使用variable,赋值符号位:=

而信号声明用signal,赋值符号为<=

2、有效域不同

1、变量只能用在进程函数体,子程序内部

2、信号不能再进程中声明,信号用在结构体、实体、程序包。

敏感信号表中只能为信号,不能为变量。

3、应用场合不同

在一个进程中,变量即使赋值,信号在进程结束后赋值。

(1)loop语句中,若在一个循环体内需要多次对某一个数据操作,则必须用变量,因为对信号赋值进行多次赋值只在最后一次才会有效。

(2)数组的索引(index)只能用变量。如果使用信号则编译会报错。

在并行语句中:

(1)进程外部不能为同一信号多次赋值

architecture one of fz is

begin

s<=a;

y<=s+1;

s<=a+b;

end architecture one;

并行语句中多次赋值会产生冲突:

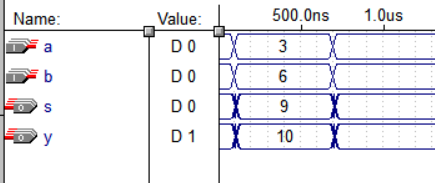

如果a或b发生变化,则执行语句s<=a+b;因为a或b变化,影响使得s变化,则执行语句y<=s+1。因为这两条语句是并行的。仿真结果如图1所示。y<=s+1; s<=a+b;这两句的先后顺序不影响结果。这一点也能体现并行语句的特点。

在进程语句中:

1、进程内部信号的普通赋值

这里所说的进程内部信号的普通赋值,是指信号赋值不需要通过时钟边沿来驱动。由于进程中的语句都是顺序语句,所以进程中的普通信号赋值都是顺序执行的,但有一点需要注意,就是如果在一个进程中多次为一个信号赋值时,只有最后一个值会起作用。什么意思呢?也就是说在进程内部多次为一个信号赋值时,只有最后一次赋值会起作用;如果还将此信号赋给其他信号,一律都按此信号的最后一次所赋的值赋给其它信号,而为此信号多次赋值的语句的位置可以任意(在顺序一定的前提下),对结果没有任何影响。

例3:

architecture one of fz is

begin

process(a,b,s)

begin

s<=a;

s<=a+b;

y<=s+1;

end process

end architecture one;

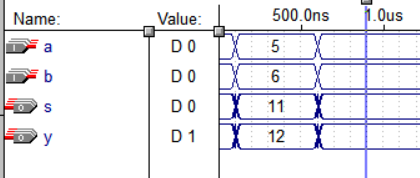

在例3的程序中,如果a或b发生变化(由高到低或由无到有),则执行此进程;对s的最后一次赋值语句为s<=a+b,所以将a+b的值赋给s;而y<=s+1这句赋值语句中s的值取得便是对s最后一次所赋的值a+b,而y<=s+1这句语句的位置对结果没有影响。仿真结果如图2所示:

例4:

architecture one of fz is

begin

process(a,b,s)

begin

s<=a+b;

s<=a;

y<=s+1;

end process

end architecture one;

在例4的程序中,如果a或b发生变化,则执行此进程;对s的最后一次赋值语句为s<=a,所以将a的值赋给s(s始终保持与a一致);而y<=s+1这句赋值语句中s的值取得便是对s最后一次所赋的值a,而y<=s+1这句语句的位置对结果没有影响。仿真结果如图3所示:

编译器直接忽略b信号

编译器直接忽略b信号

在例3和例4中,y<=s+1放在三句赋值语句的什么位置上对结果没有影响。

2、进程内部信号的时钟边沿赋值

这里所说的进程内部信号的时钟赋值,是指信号赋值需要通过时钟边沿的驱动。由于时钟边沿触发的特殊性,即在时钟边沿发生时,对各个信号采样,然后将时钟边沿这一时刻各个信号的取值赋给所要赋值的对象,也就是将时钟到来前未发生变化的各个信号的取值赋给所要赋值的对象(换句话说就是指,当进程执行结束之后进程挂起时,数据发生带入)。但这些信号的赋值仍是顺序执行的(因为在if语句中),所以有一点仍需要注意,就是如果在一个进程中通过时钟边沿触发多次为同一个信号赋值时,只有最后一个值会起作用。什么意思呢?也就是说在进程内部多次为同一个信号赋值时,只有最后一次赋值会起作用;如果还将此信号赋给其他信号,一律都按此信号的最后一次所赋的值赋给其它信号,而为此信号多次赋值的语句的位置可以任意,对结果没有任何影响。

例5:

process(clk)

begin

if clk='1'and clk'event then

s<=a+b;

s<=a;

y<=s+1;

end if;

end process;

在例5的程序中,如果clk发生变化,则执行此进程,如果clk出现上升沿,则执行if语句中的几句赋值语句;对s的最后一次赋值语句为s<=a,所以将a的值赋给s;而y<=s+1这句赋值语句中s的值取得便是对s最后一次所赋的值a,而y<=s+1这句语句的位置对结果没有影响;各个赋值语句右侧的信号的取值为时钟上升沿那一刻的采样值,所以与例3例4不同,y<=s+1这句赋值语句所执行的是时钟采样那一时刻的s还没有发生变化时(未赋值变成新的a时)的取值加1后再赋给y。仿真结果如图4所示。

总之y是对前一次上升沿的赋值。编译器直接把b忽略掉了。在时钟上升沿的时候s=a。但在这个上升沿的时候s还没有发生改变,所以y=s+1中的s对应的是时钟上升沿之前的值。

例6:

process(clk)

begin

if clk='1'and clk'event then

s<=a;

s<=a+b;

y<=s+1;

end if;

end process;

end architecture one;

在例6的程序中,如果clk发生变化,则执行此进程,如果clk出现上升沿,则执行if语句中的几句赋值语句;对s的最后一次赋值语句为s<=a+b,所以将a+b的值赋给s;而y<=s+1这句赋值语句中s的值取得便是对s最后一次所赋的值a+b;各个赋值语句右侧的信号的取值为时钟上升沿那一刻的采样值,

所以与例3例4不同,y<=s+1这句赋值语句所执行的是时钟采样那一时刻的s还没有发生变化时(未赋值变成新的a+b时)的取值加1后再赋给y。

在上两例中,y<=s+1;放在三句赋值语句的什么位置上对结果没有影响;if语句换成wait until clk='1’结果也一样。

4403

4403

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?