采用Verilog HDL设计4bits输入的全加器,设计文件如下所示:

//4位全加器

//Author:学习FPGA的电气小兴兴

//Time:2023-11-08

module addr4

(

input wire [3:0] ina ,

input wire [3:0] inb ,

input wire cin ,

output wire [3:0] sum ,

output wire cout

);

//main code

assign {cout,sum}=ina+inb+cin;

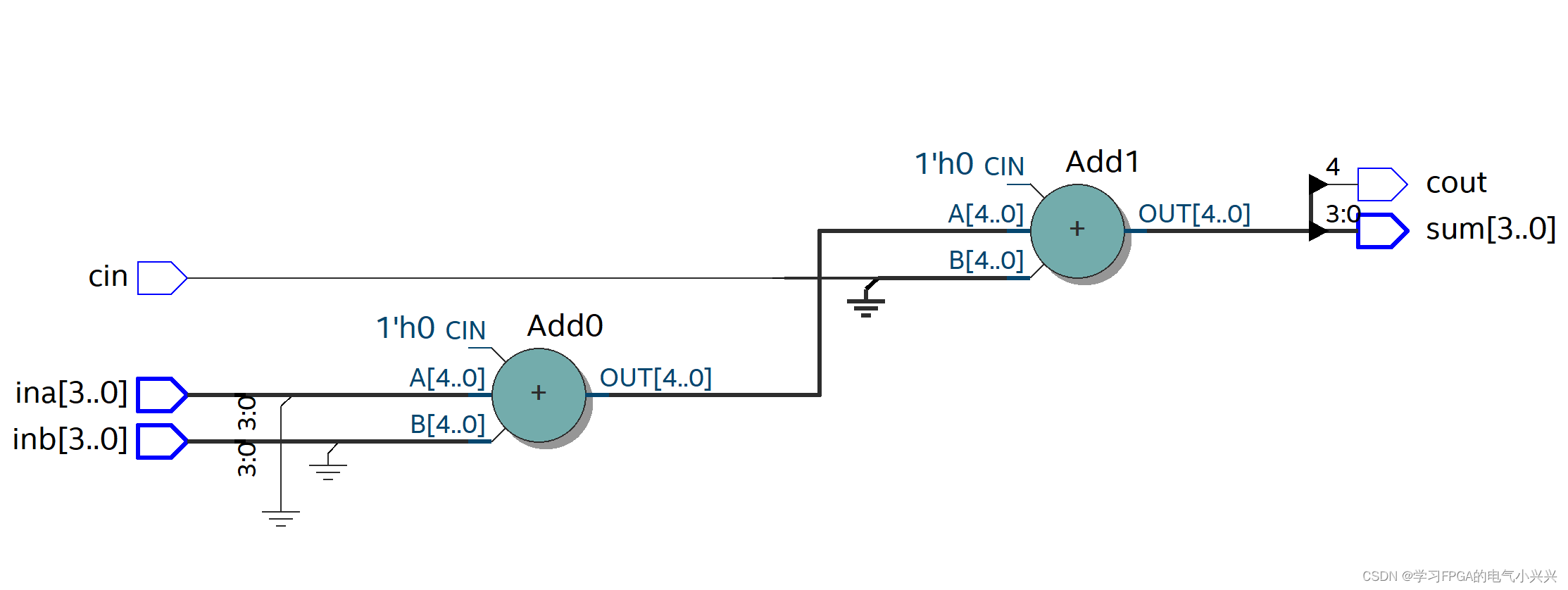

endmodule 采用Quartus综合后的电路如下图所示。 编写Testbench,验证设计文件逻辑功能的正确性,如下所示。

编写Testbench,验证设计文件逻辑功能的正确性,如下所示。

//4位全加器仿真程序

//Author:学习FPGA的电气小兴兴

//Time:2023-11-8

`timescale 1ns/1ns

//`include "addr4.v"

module addr4_tb ;//测试模块的名称

reg [3:0] ina ;//测试输入信号定义为reg型

reg [3:0] inb ;

reg cin ;

wire [3:0] sum ;//测试输出信号定义为wire型

wire cout ;

integer i,j;

//调用测试对象

addr4 addr4_inst(.ina(ina),.inb(inb),.cin(cin),.sum(sum),.cout(cout));

always #5 cin = ~cin ;//设定cin的取值

initial begin

ina=0;inb=0;cin=0;

for(i=1;i<16;i=i+1)

#10 ina=i;//设定a的取值

end

initial begin

for(j=1;j<16;j=j+1)

#10 inb=j ;//设定b的取值

end

initial begin //定义结果显示格式

$monitor($time,,,"%d+%d+%b={%b,%d}",ina,inb,cin,cout,sum);

#200 $stop;

end

endmodule

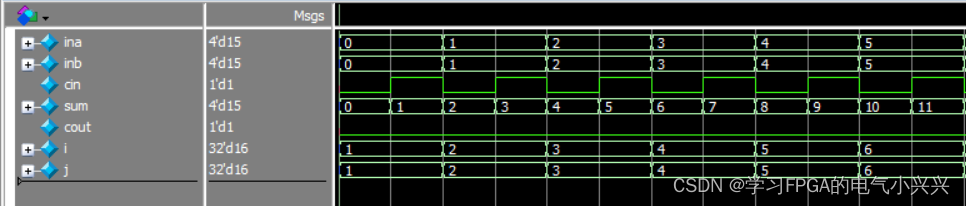

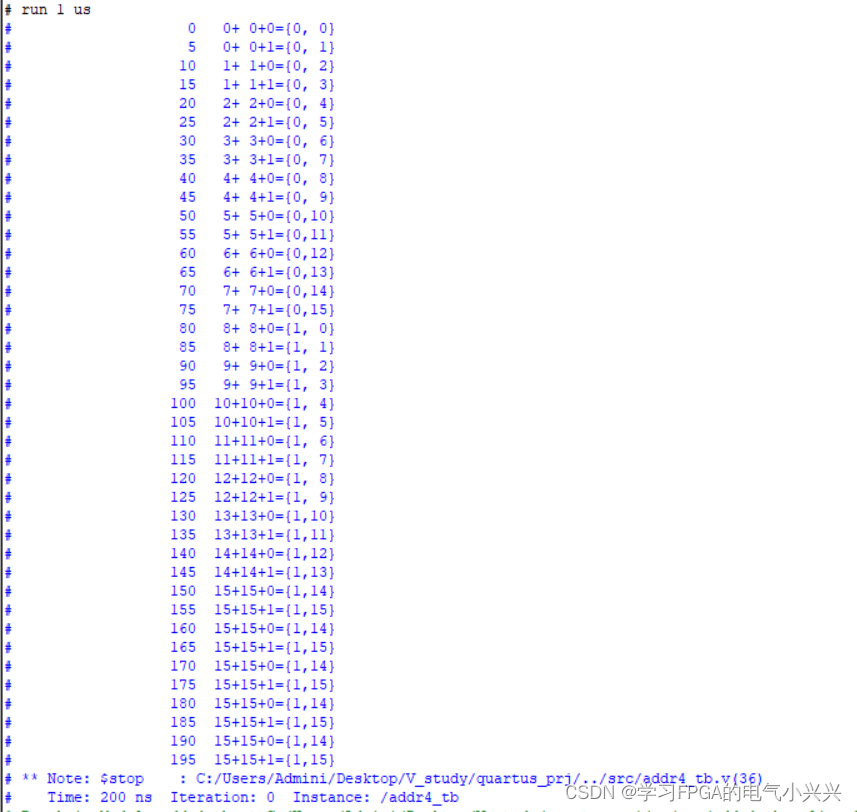

采用Questa进行波形仿真,仿真波形和打印结果如下图,逻辑功能完全正确,验证成功。

文章描述了一位作者使用VerilogHDL设计了一个4位输入的全加器,提供了设计文件和Quartus综合后的电路图。接着,作者编写了Testbench进行功能验证,结果显示逻辑功能正确。最后,通过Questa进行波形仿真并验证了设计的正确性。

文章描述了一位作者使用VerilogHDL设计了一个4位输入的全加器,提供了设计文件和Quartus综合后的电路图。接着,作者编写了Testbench进行功能验证,结果显示逻辑功能正确。最后,通过Questa进行波形仿真并验证了设计的正确性。

1205

1205

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?