一、DDS基本原理

DDS(Direct Digital Synthesizer)即数字合成器,是一种新型的频率合成技术,具有相对带宽大,频率转换时间短、分辨率高和相位连续性好等优点。较容易实现频率、相位以及幅度的数控调制,广泛应用于通信领域。

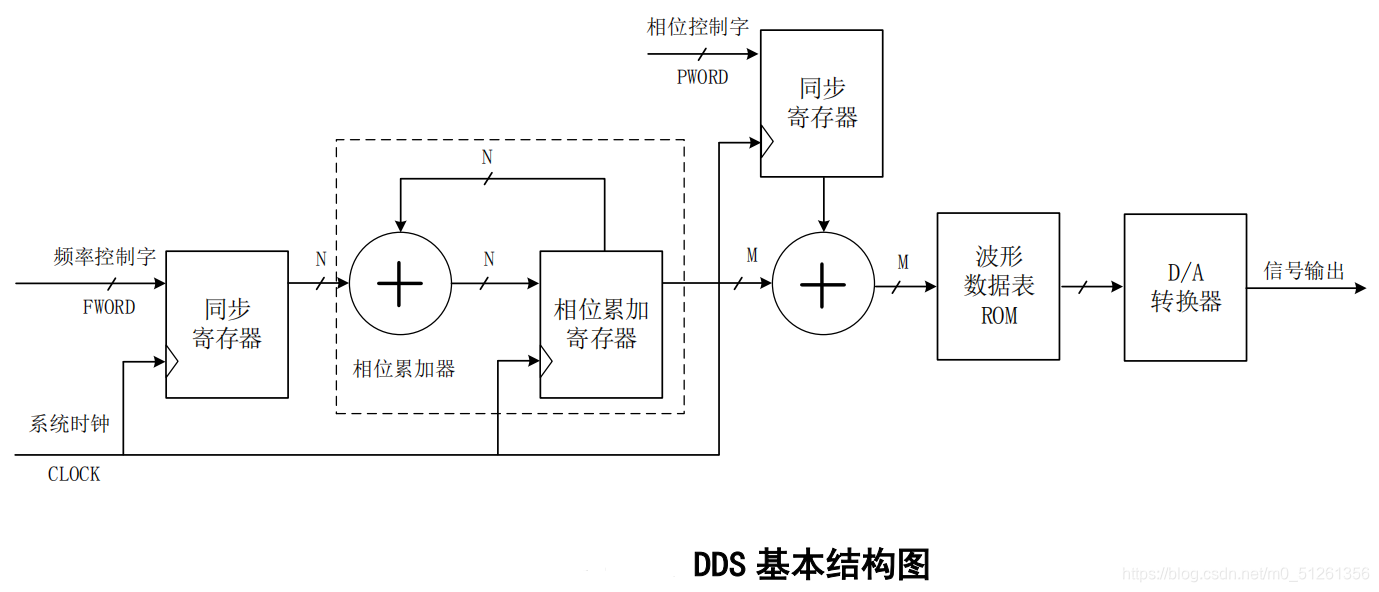

DDS 的基本结构图如图所示:

由图可以看出,DDS主要由相位累加器、相位调制器、波形数据表以及 D/A 转换器构成。

其中相位累加器由 N 位加法器与 N 位寄存器构成。每个时钟周期的时钟上升沿,加法器就将频率控制字与累加寄存器输出的相位数据相加,相加的结果又反馈至累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。即在每一个时钟脉冲输入时,相位累加器便把频率控制字累加一次。

相位累加器输出的数据就是合成信号的相位。相位累加器的溢出频率,就是DDS输出的信号频率。相位累加器输出的数据,作为波形存储器的相位采样地址,这样就可以把存储在波形存储器里的波形采样值经查表找出,完成相位到幅度的转换。波形存储器的输出数据送到D/A转换器,由D/A转换器将数字信号转换成模拟信号输出。

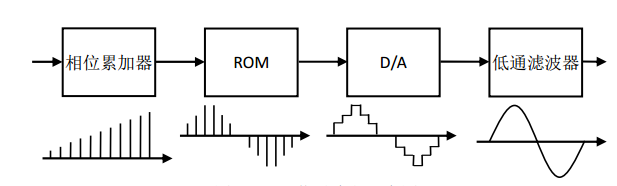

DDS 信号流程示意图如图所示:

这里相位累加器位数为N位(N的取值范围实际应用中一般为24~32),相当于把正弦信号在相位上的精度定义为N位,所以其分辨率为1/2N。

若DDS的时钟频率为Fclk,频率控制字fword为1,则输出频率为Fout=Fclk/2N,这个频率相当于“基频”。若fword为B,则输出频率为Fout= B×Fclk/2N。

从上式分析可得,当系统输入时钟频率Fclk不变时,输出信号频率由频率控制字B所决定,由上式可得:B=2N×Fout/Fclk。其中B为频率字且只能取整数。为了合理控制ROM的容量,此处选取ROM查询的地址时,可以采用截断式,即只取32位累加器的高M位。这里相位寄存器输出的位数一般取10~16 位。

一个完整周期的正弦信号的波形总共有 33 个采样点,其中第 1 点和第

33 点的值相同,第 33 点为下一个周期的起始点,因此,实际一个周期为 32 个采样点

本文详细介绍了DDS的基本原理,包括相位累加器、波形数据表和D/A转换器的工作机制,并通过FPGA实现DDS的仿真与调试过程,阐述了如何通过改变频率控制字来调整输出信号的频率和相位。

本文详细介绍了DDS的基本原理,包括相位累加器、波形数据表和D/A转换器的工作机制,并通过FPGA实现DDS的仿真与调试过程,阐述了如何通过改变频率控制字来调整输出信号的频率和相位。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

932

932

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?