一、概要

仿真是FPGA开发过程中必不可少的一步,就像C语言开发过程中“编译、运行”一样。由于Verilog语言是对于电路结构的描述,因此需要EDA平台对代码进行分析综合后才能进行仿真。这里以一段“二选一数据选择器”的代码为例,介绍testbench(测试平台)的写法和使用Quartus II与Modelsim Altera进行联合仿真的步骤。

二、Quartus II简单开发过程

1.创建工程

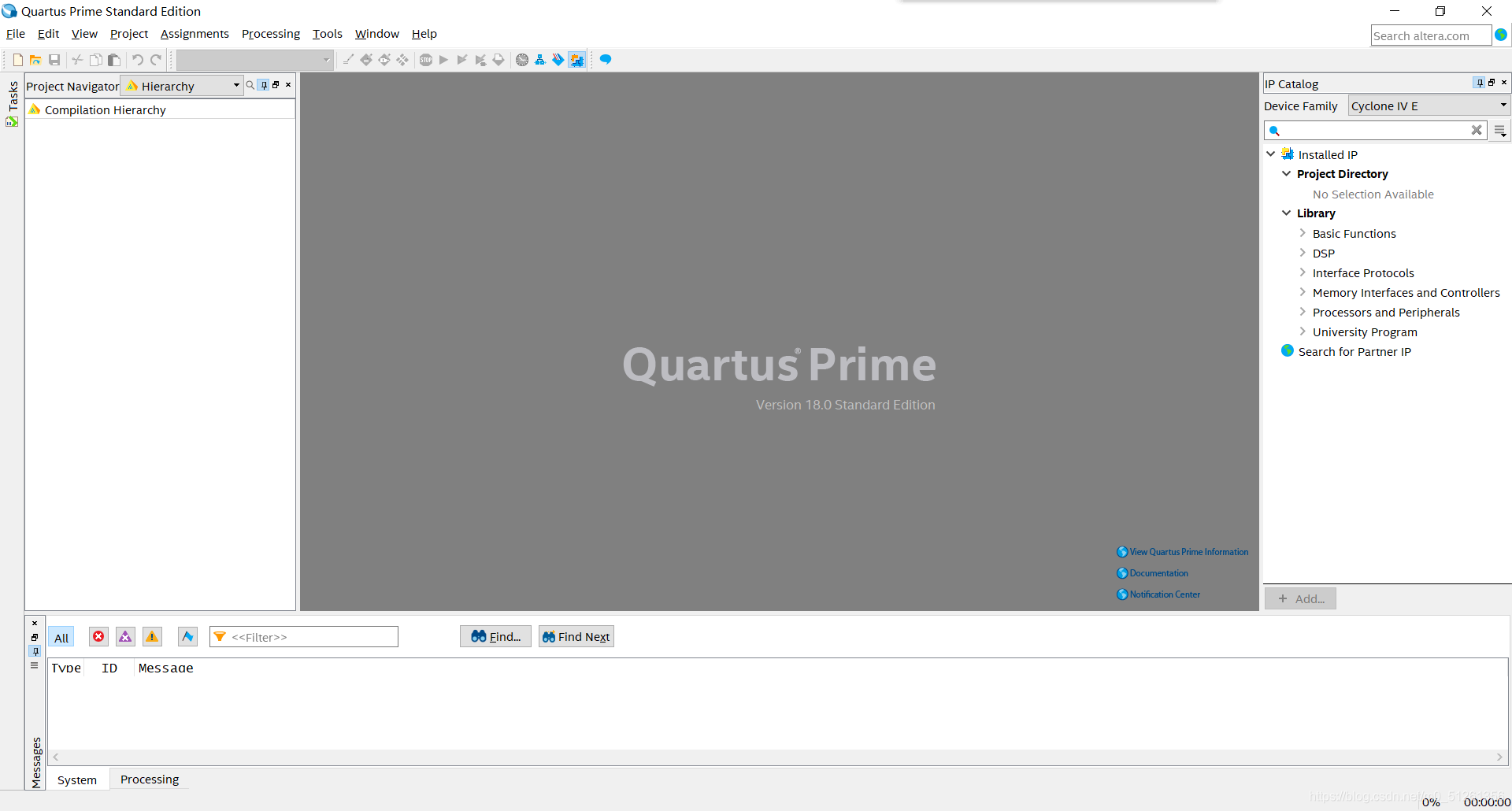

单击桌面Quartus II图标,打开软件进入如下界面

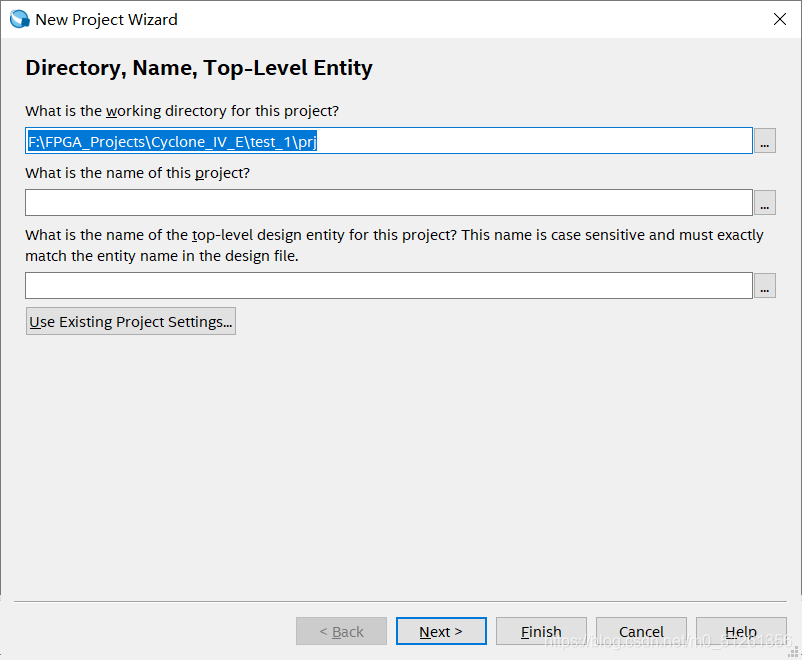

点击左上角**“File-New Project Wizard”**,进入工程创建向导。在下图界面可以设置工程路径以及工程名称。(建议不要放在软件安装目录下)

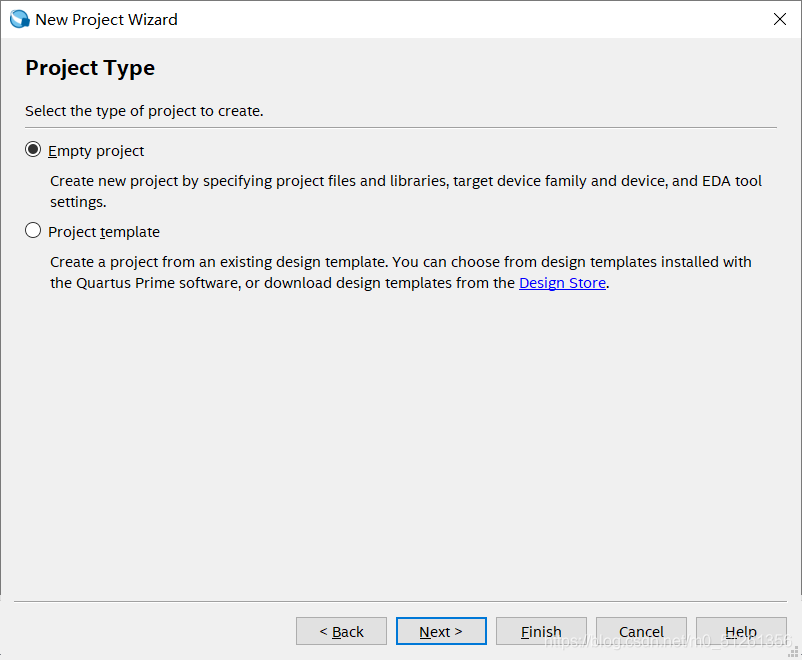

单击Next,出现以下界面:

选择建立一个空工程,进入下一个界面:

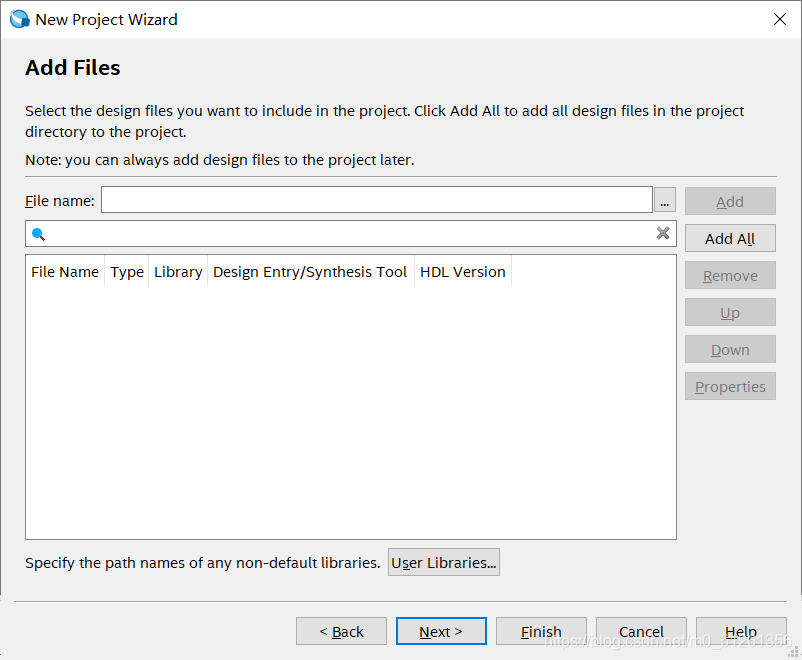

这个页面用于添加已有的文件,如果是第一次写,可以跳过,如果已经有写好的代码,可以点击添加。再单击Next,进入下一个界面:

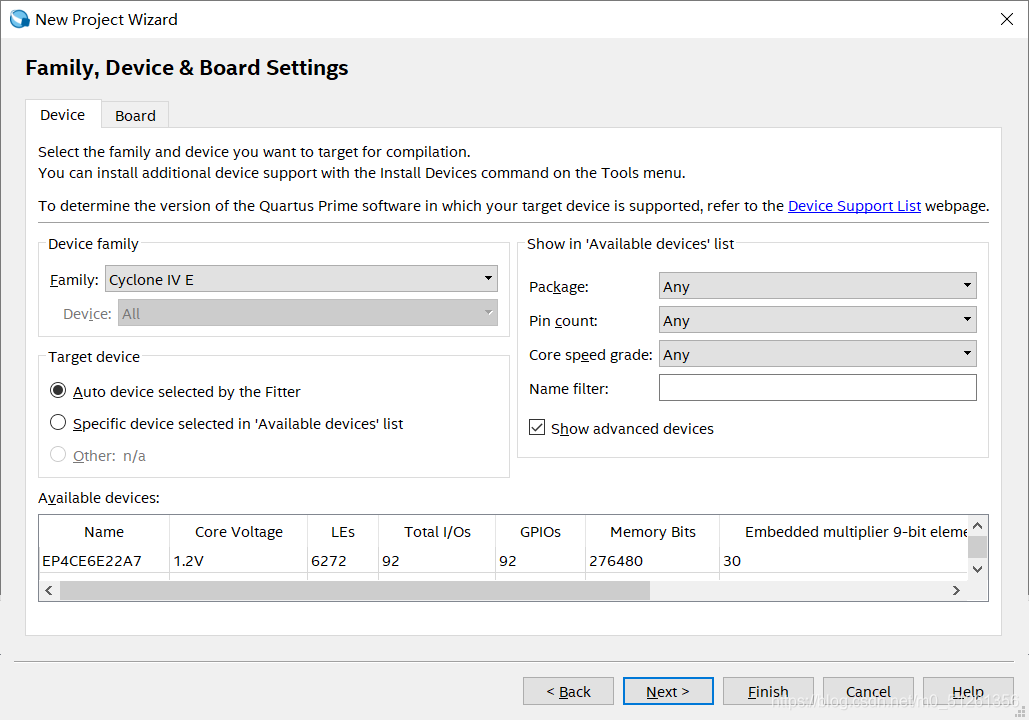

在这个界面选择自己使用的芯片型号,前提是安装对应的器件库。单击Next进入下一个界面:

在工具设置中,仿真工具选择Modelsim-Altera,其余不用更改,单击Next进入下一个界面

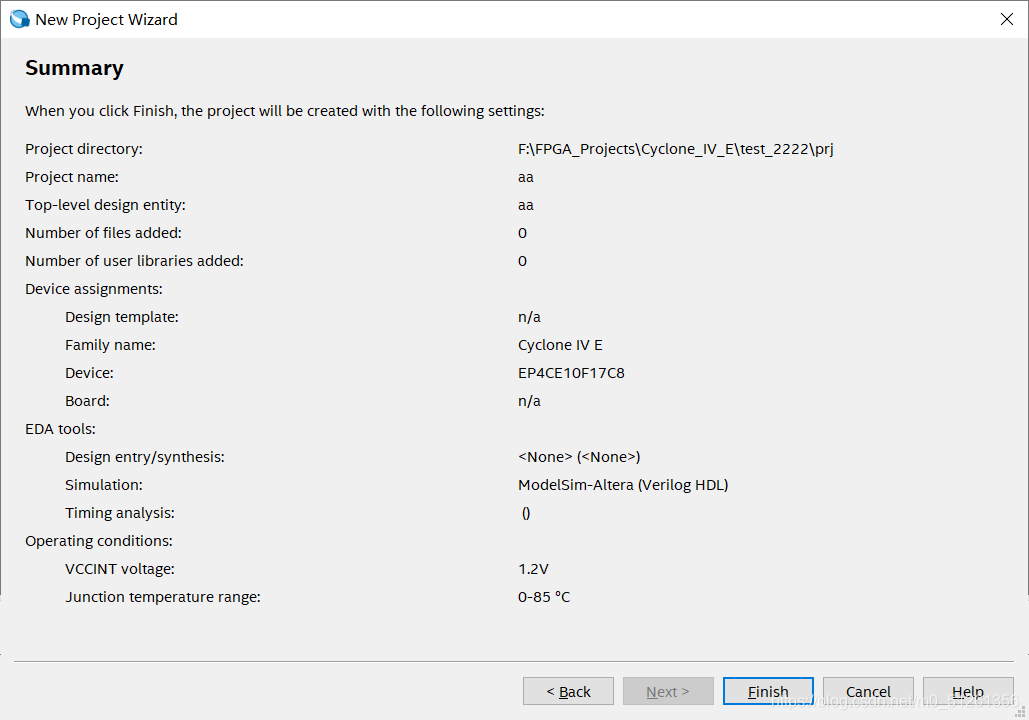

如上图是工程所有的相关设置,单击Finish即可完成工程的创立。

2.编写设计文件

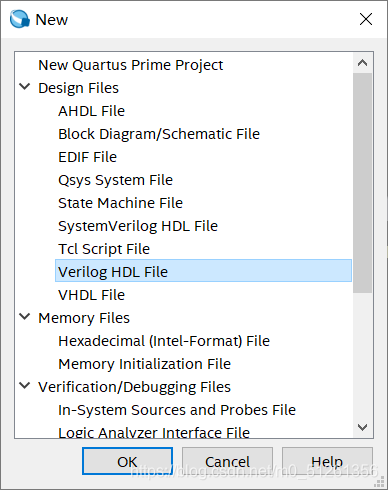

单击New图标

或者Ctrl+N

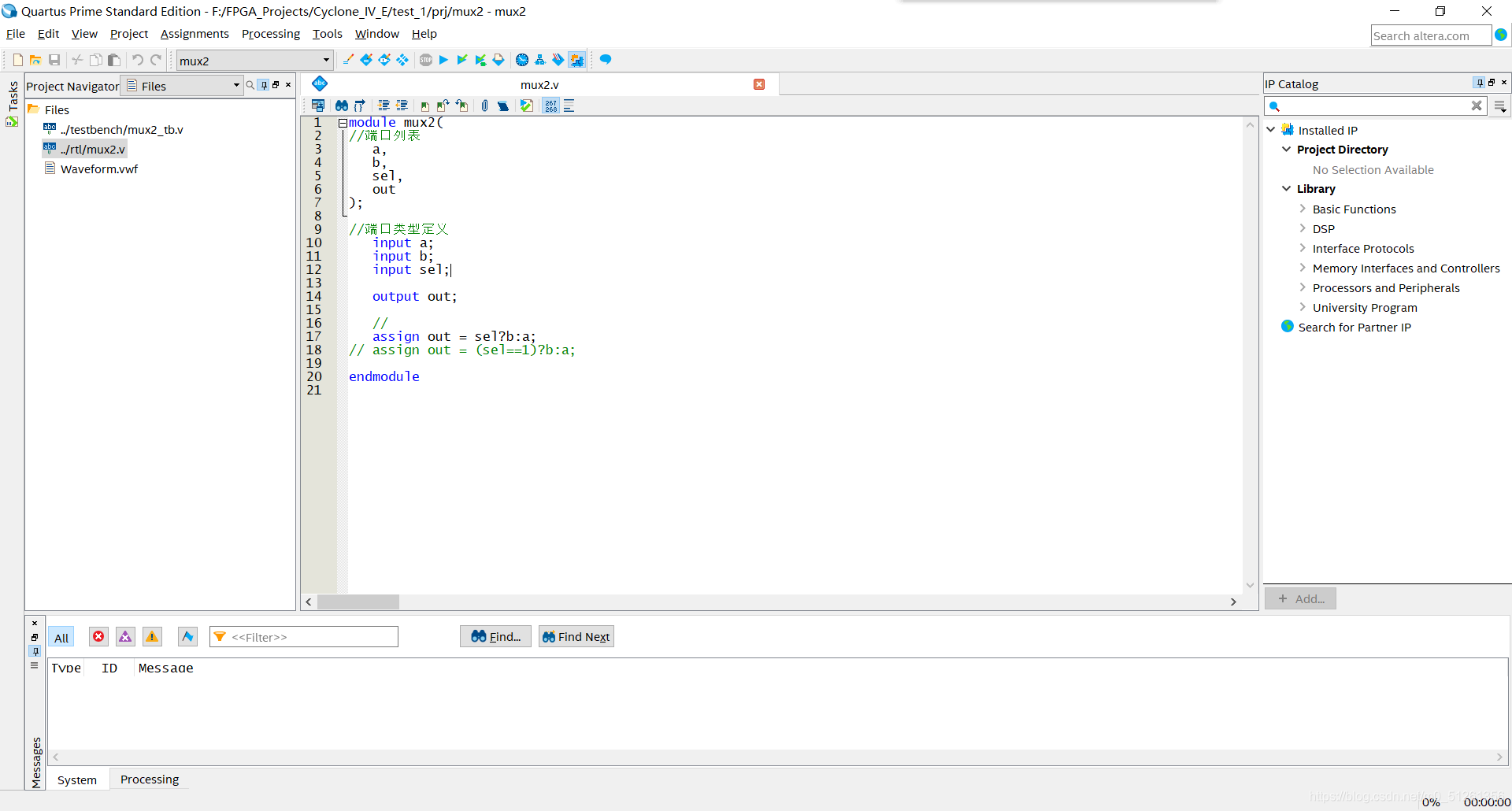

选择Verilog HDL File,会出现空白文本编辑界面,编辑好自己的代码后按Ctrl+S保存,如图

二选一数据选择器代码。

module mux2(

//端口列表

a,

b,

sel,

out

);

//端口类型定义

input a;

input b;

input sel;

output out;

//

assign out = sel?b:a;

// assign out = (sel==1)?b:a;

endmodule

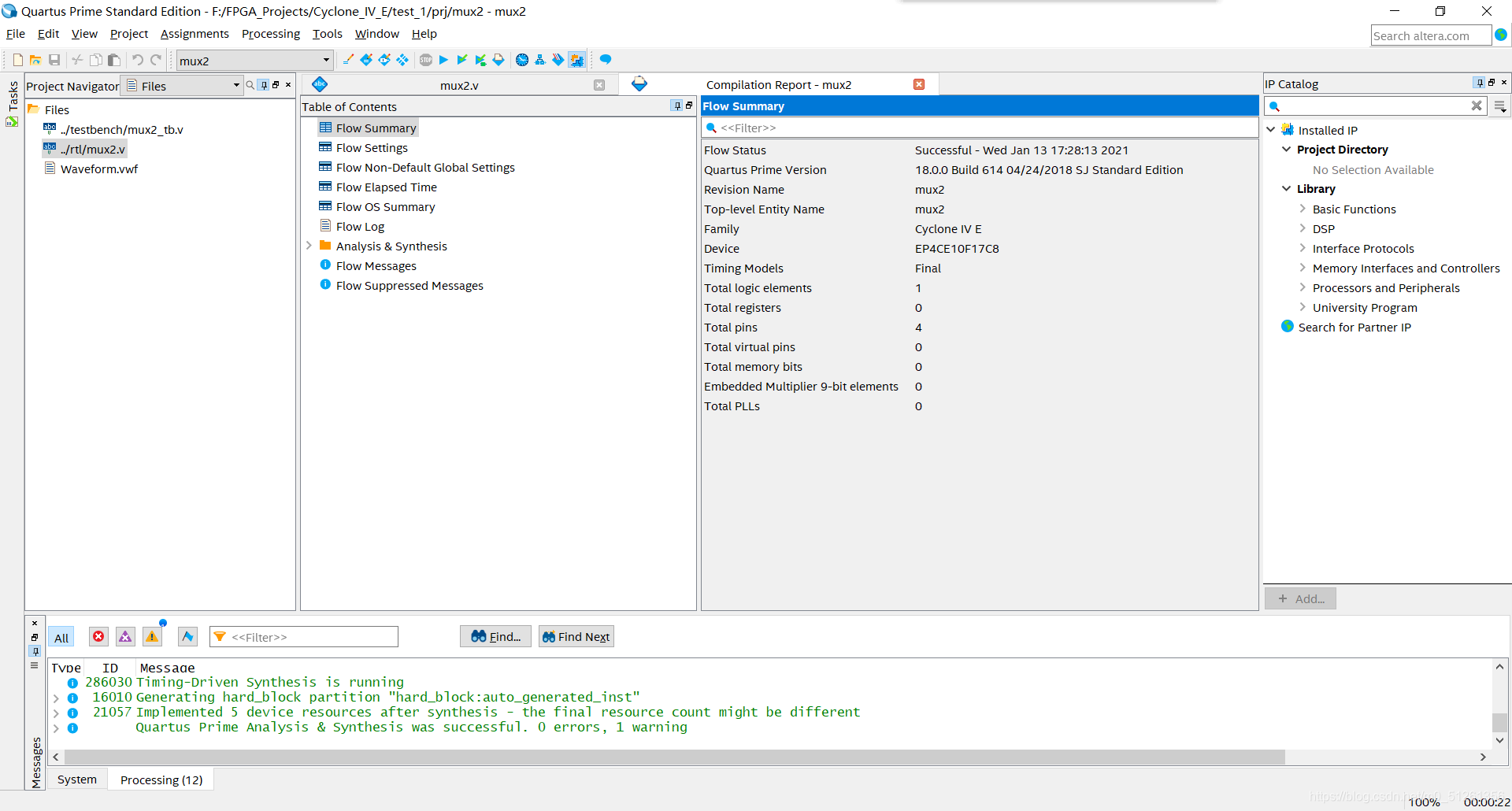

接下来点击"Start Analysis&Synthesis"或者按Ctrl+K进行分析综合。当右下角显示进度为100%时分析综合完毕,出现如下界面:

3.关联仿真工具

点击"Tools-Options-General-EDA Tool Options",在Modelsim Altera一栏中选择自己安装的Modelsim Altera的路径,注意一定是"···\modelsim_ase\win32aloem"的格式。

本文介绍了在FPGA开发中使用Quartus II和Modelsim Altera进行联合仿真的详细步骤,包括创建工程、编写设计文件、设置仿真工具路径、创建测试激励文件(testbench)以及进行功能仿真和门级仿真。通过一个二选一数据选择器的例子,阐述了testbench的基本写法和关键设置。

本文介绍了在FPGA开发中使用Quartus II和Modelsim Altera进行联合仿真的详细步骤,包括创建工程、编写设计文件、设置仿真工具路径、创建测试激励文件(testbench)以及进行功能仿真和门级仿真。通过一个二选一数据选择器的例子,阐述了testbench的基本写法和关键设置。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5483

5483

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?