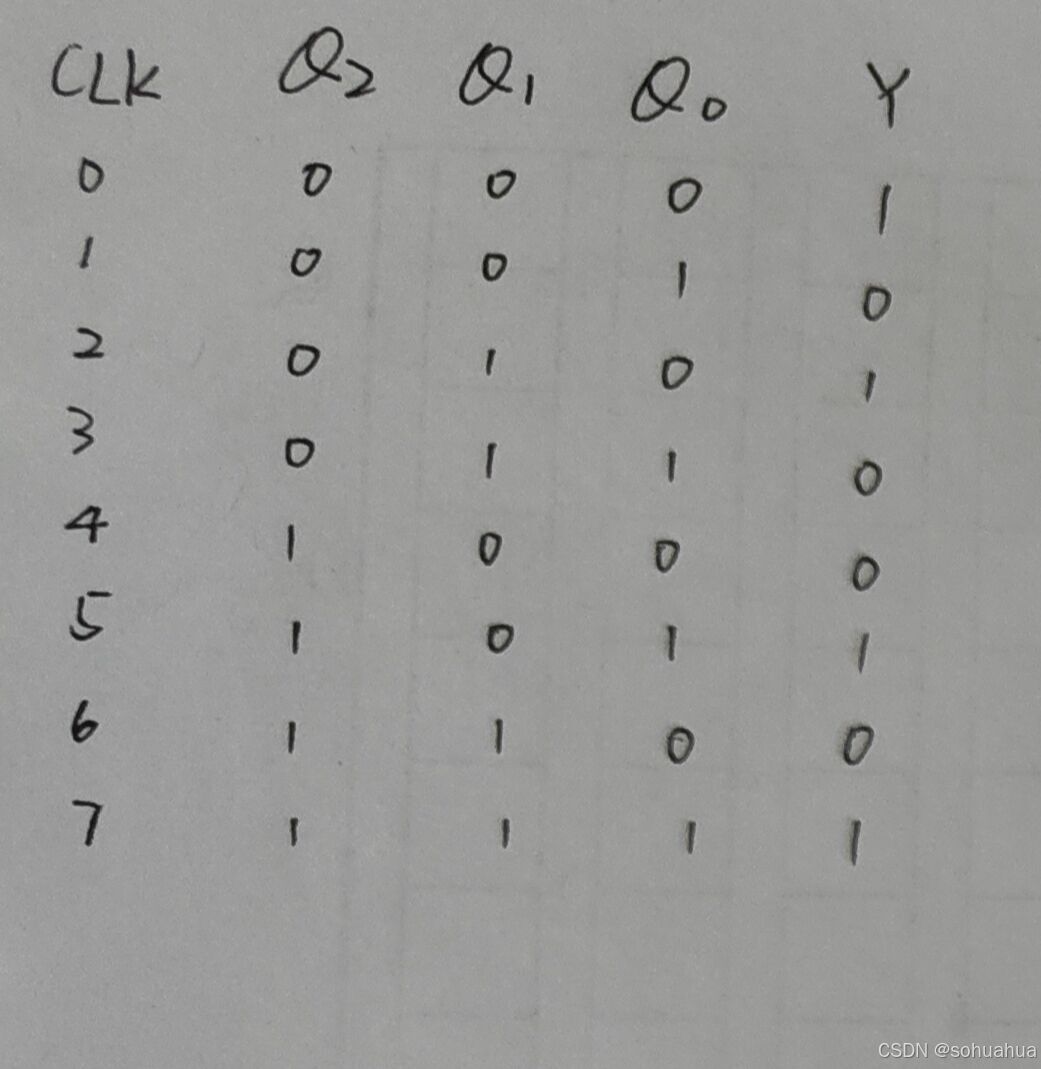

一、课程设计题目1:设计周期性输出10100101的脉冲序列发生器

1、设计任务及功能、参数要求

功能:设计一个同步脉冲序列发生器(可有多种实现方法),周期性输出10100101脉冲序列。

要求:画出电路逻辑图。依据电路逻辑图,选择适当型号的芯片,画出实际电路连线图。依据芯片连线图用实验箱搭建所设计的电路,验证设计是否正确。

注意 :可将输出连接到七段数码管或LED观察现象。

2、设计原理图

3、元器件的具体型号的功能及引脚说明

用到的元器件:

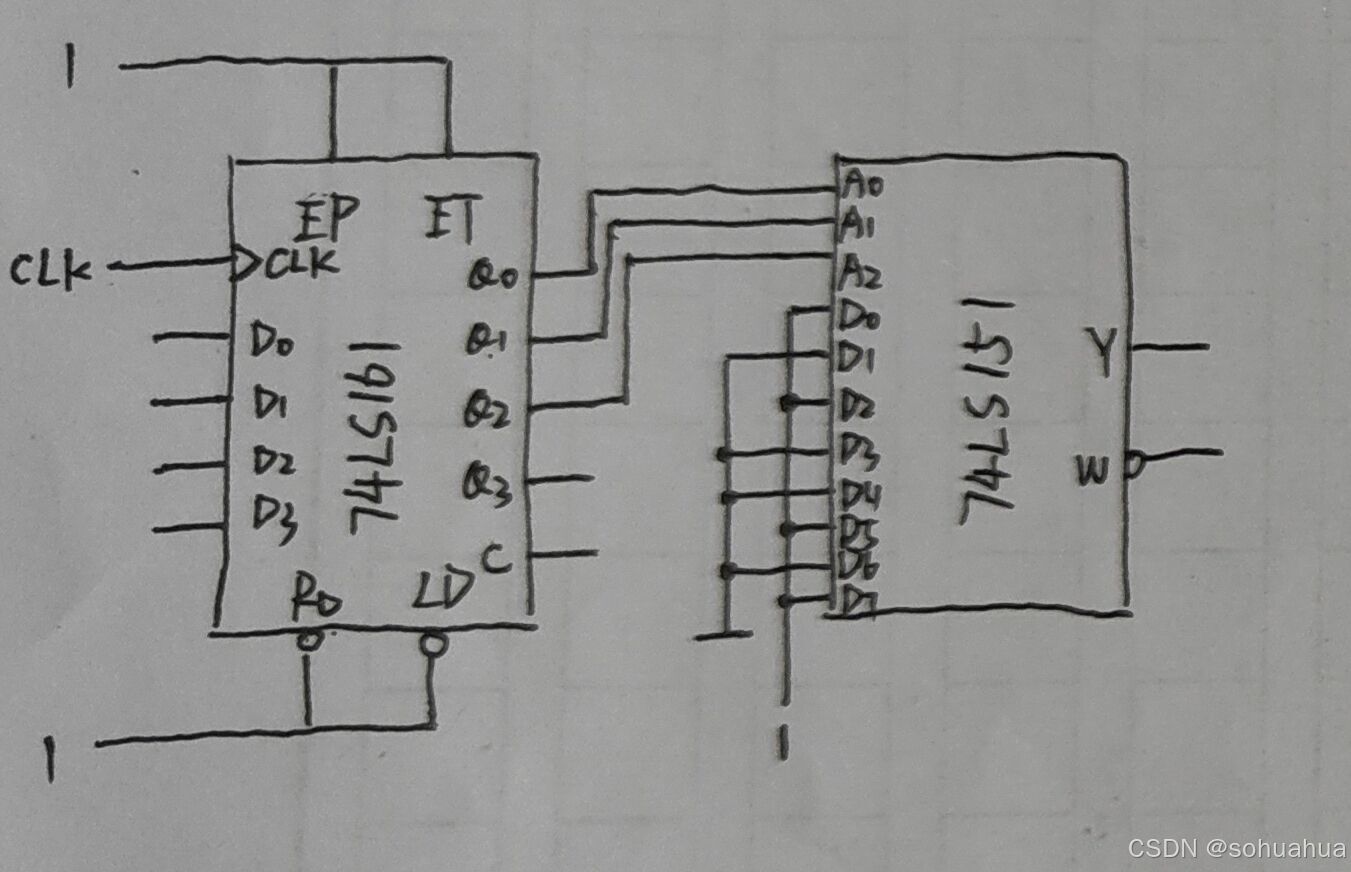

计数器74LS161、数据选择器74LS151

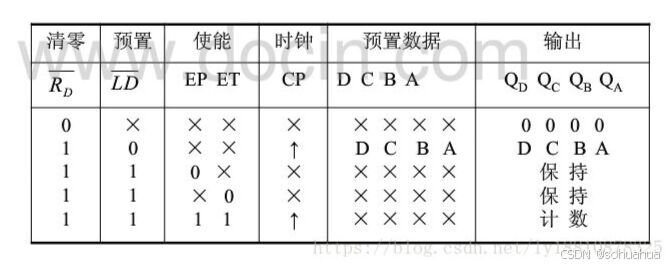

74LS161功能表:

异步清零

同步并行置数

保持功能

计数功能(计到1111时RCo=1)

EP、ET是计数允许端,只有当二者同为一时,计数器处于工作状态

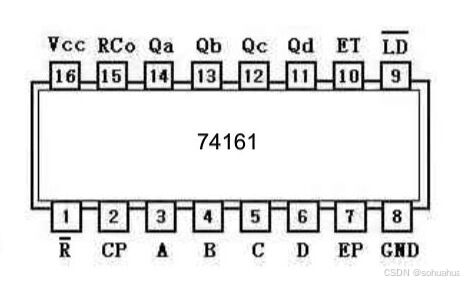

74LS161引脚图:

74LS161引脚说明:

电源:VCC

地:GND

四个数据输入端A、B、C、D

时钟CP

使能端EP、ET

进位输出RCo

置数端LD非

清零端R非

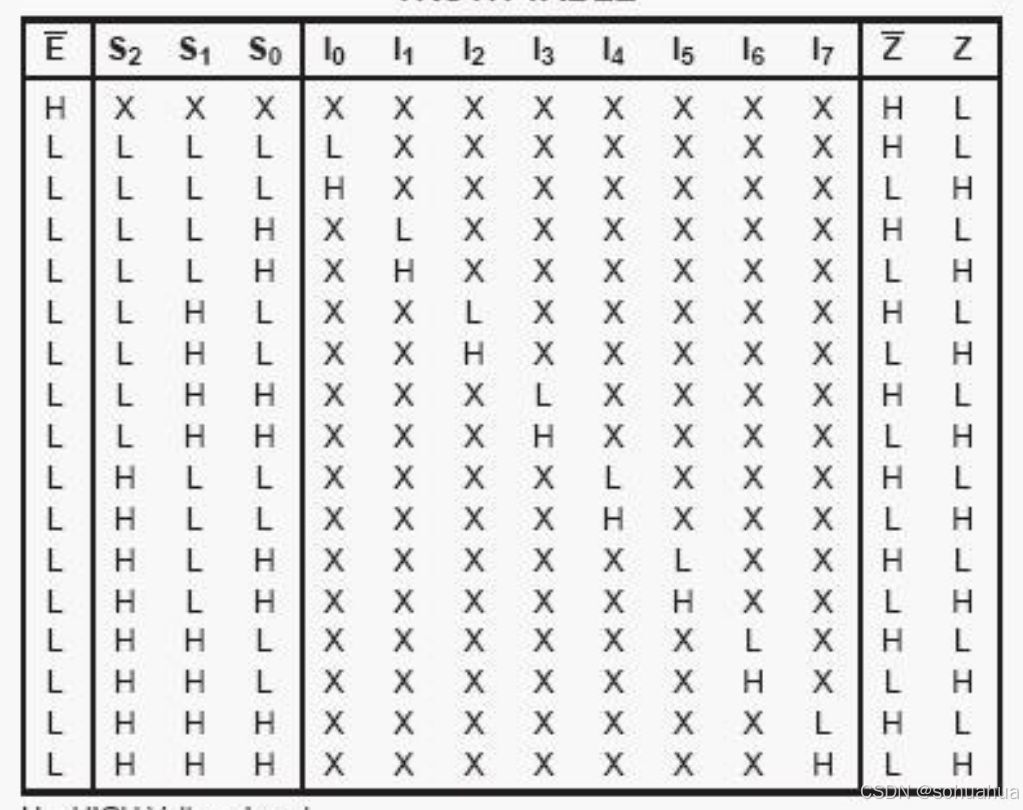

74LS151功能表:

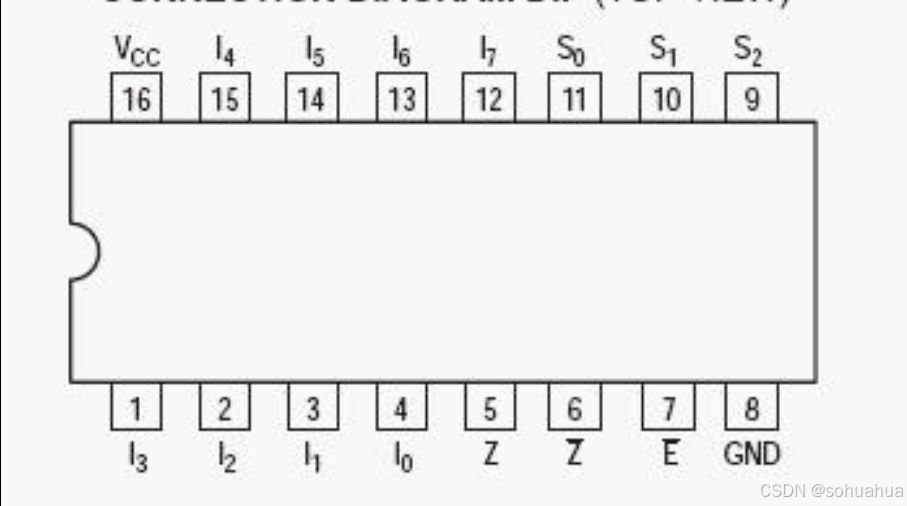

74LS151引脚图:

74LS161引脚说明:

电源:VCC

地:GND

选择控制端:A2、A1、A0

数据输入端:D0—D7

输出端:Y

反码数据输出端:W非

使能端:ST非(低电平有效)

4、系统工作原理

详细描述:

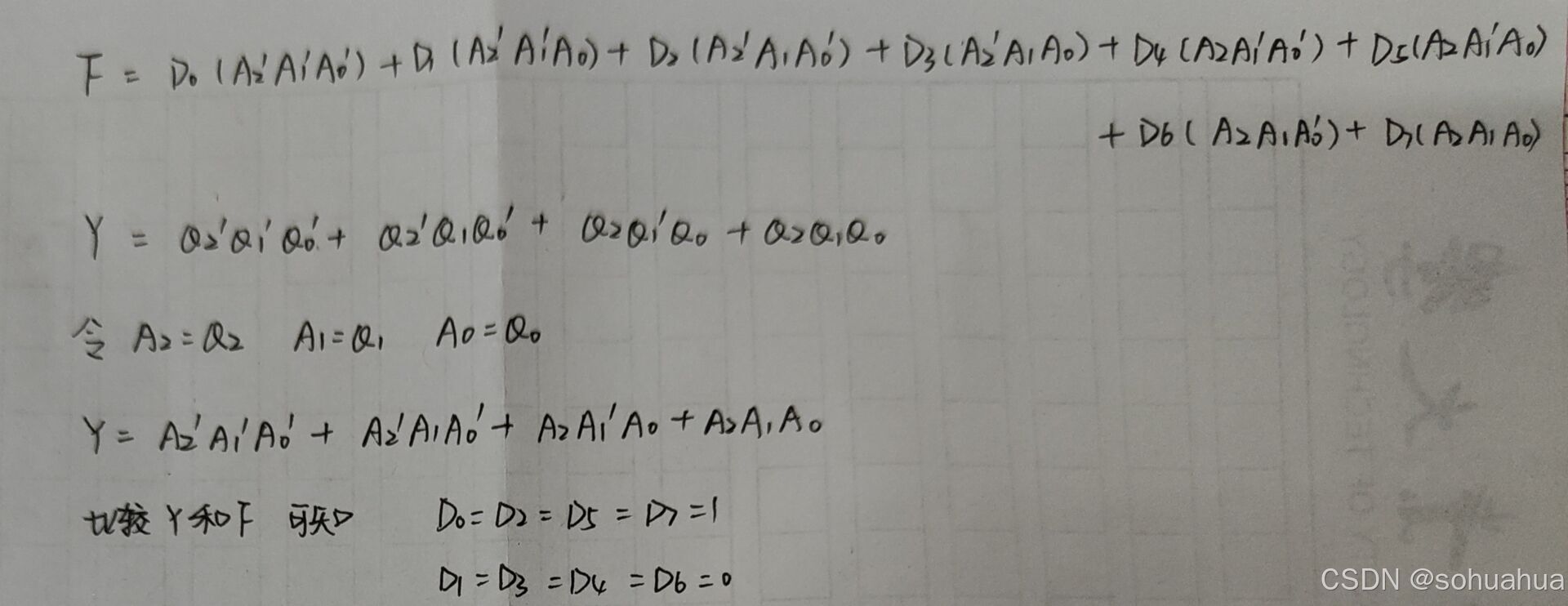

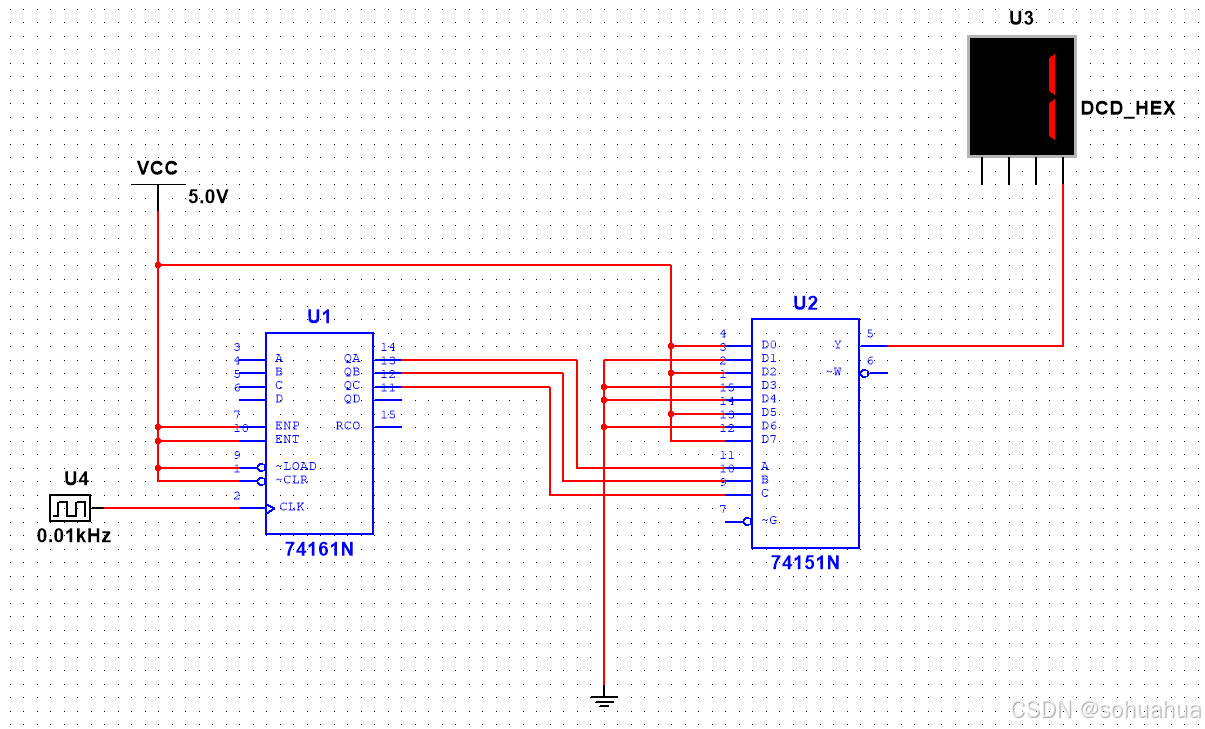

需要产生8位的序列信号10100101,所以可以选择八进制的计数器和一个八选一的数据选择器。八进制的计数器可以取自74LS161(四位二进制计数器)的低3位,八选一的数据选择器选用74LS151。根据74LS161功能表,把EP、ET、RD、LD都接成高电平,当CP信号连续不断地加到计数器上时,QCQBQA的状态便不断循环,D0~D7的状态就循环不断地依次出现在Y端。只要令D0=D2=D5=D7=1、D1=D3=D4=D6=0,便可在Y端得到不断循环的序列信号10100101。

实验仿真:

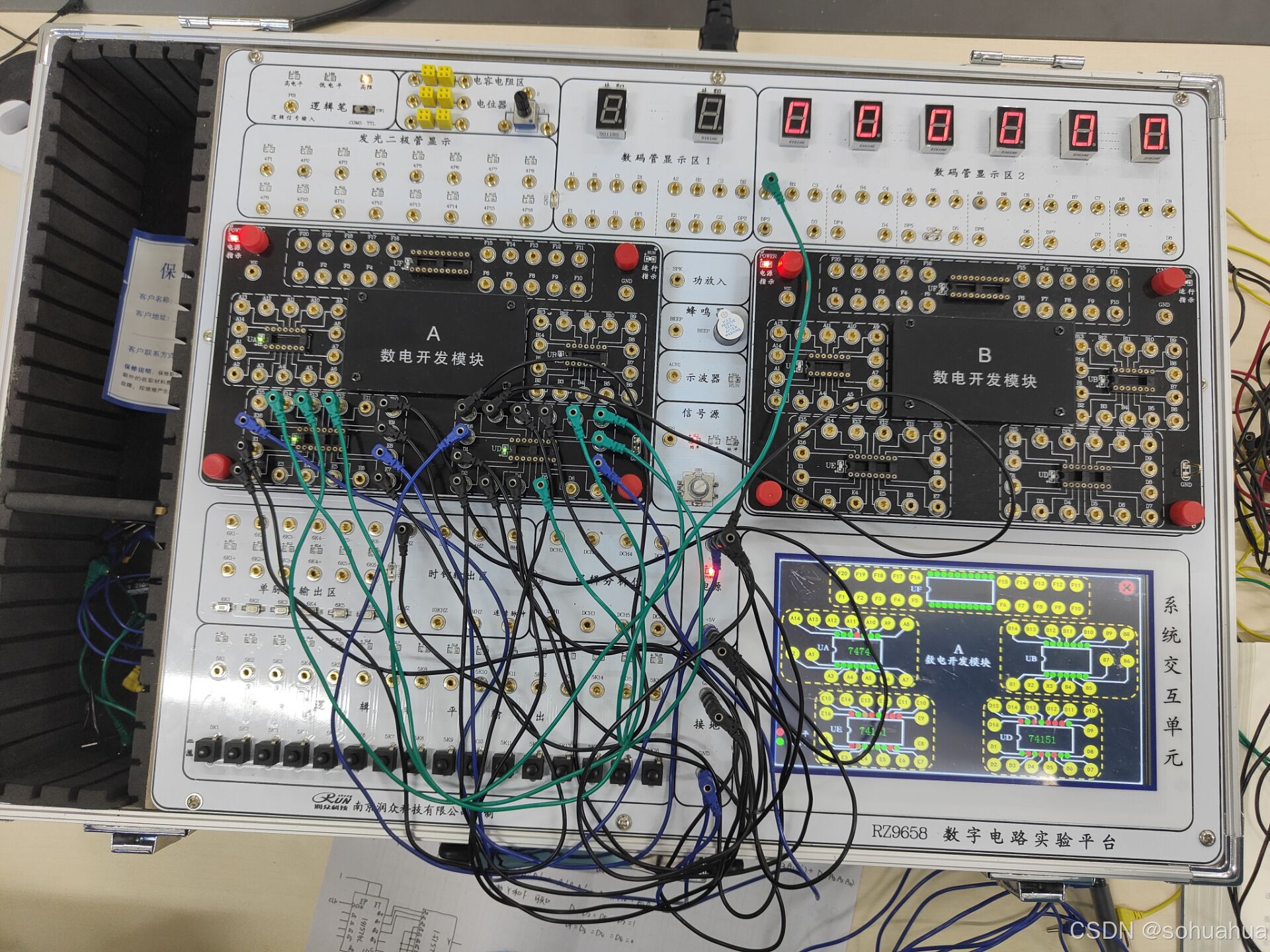

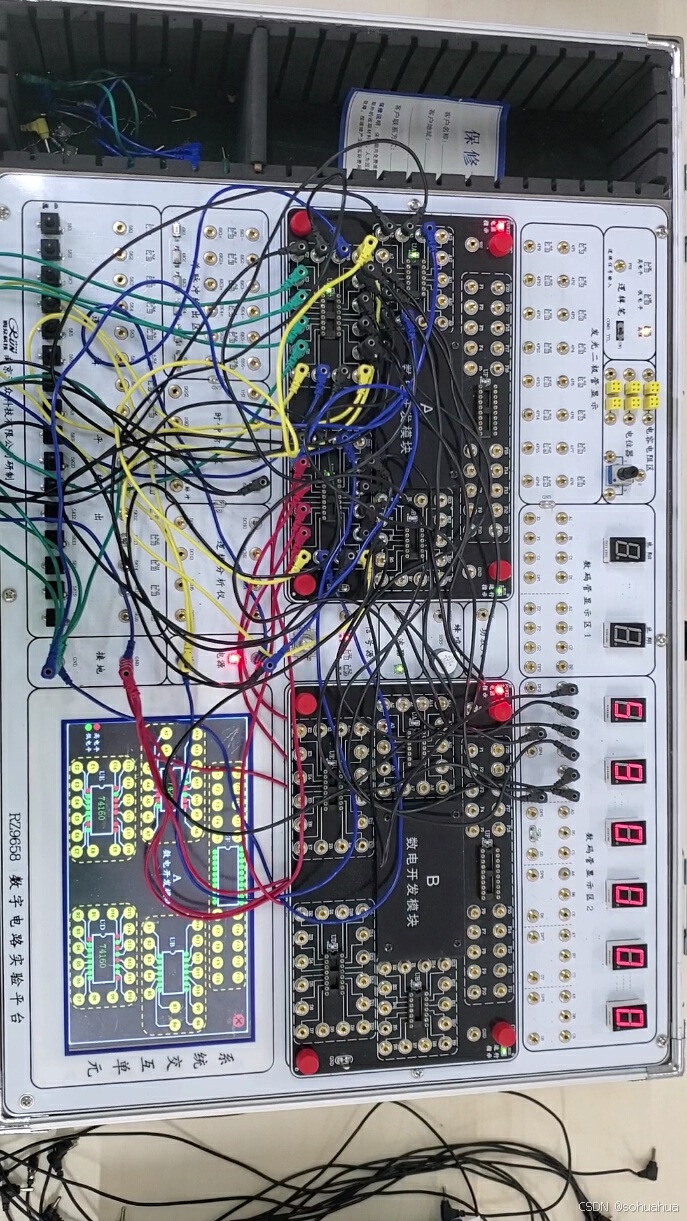

电路搭建最终结果:

5、设计过程中遇到的问题及解决方法

1.Q0、Q1、Q2与A0、A1、A2对应错误:

应该Q0与A0对应、Q1与A1对应、Q2与A2对应。

2. D0~D7连线错误:

根据逻辑式和产生的逻辑函数式可知:D0=D2=D5=D7=1、D1=D3=D4=D6=0,值取1时应该接电源,值取0时应该接地。

3.时钟频率过高结果一闪而过无法观察:

换一个低的时钟频率。

6、系统的优缺点及进一步改进措施。

优点:在需要修改序列信号时,只要对加到D0~D7的高、低电平加以修改即可实现,而不需要对电路结构作任何改动。因此,使用这种电路既灵活又方便。

缺点:只能产生8位的序列信号。

改进措施:添加QD即可产生多于8位的序列信号。

二、课程设计题目2:简易秒计时器设计与制作

1、设计任务及功能、参数要求

任务及功能:要求设计一个能显示两位秒信号的数字电子钟,分电路设计、电路安装、电路调测三个阶段完成。

参数要求:通过1Hz时钟接入计数器,计数器初值为00,按递增方式计数,增到59时,再自动返回到00。计数通过显示译码芯片同七段数码管连接并显示,设计方案可根据需要灵活选择计数器芯片。

实验要求

1、用Multisim设计并仿真

2、选择合适的芯片,并在实验箱上连线验证结果

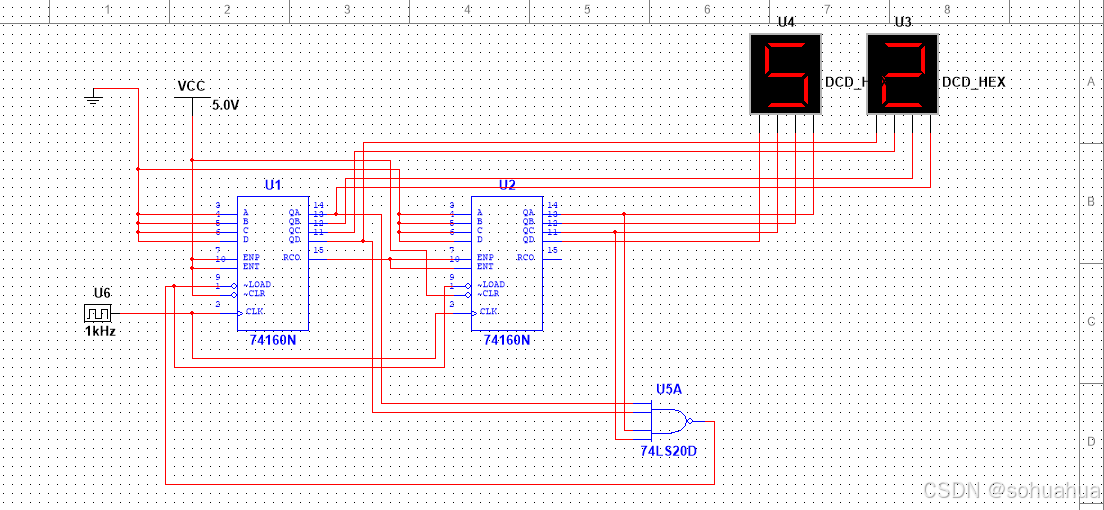

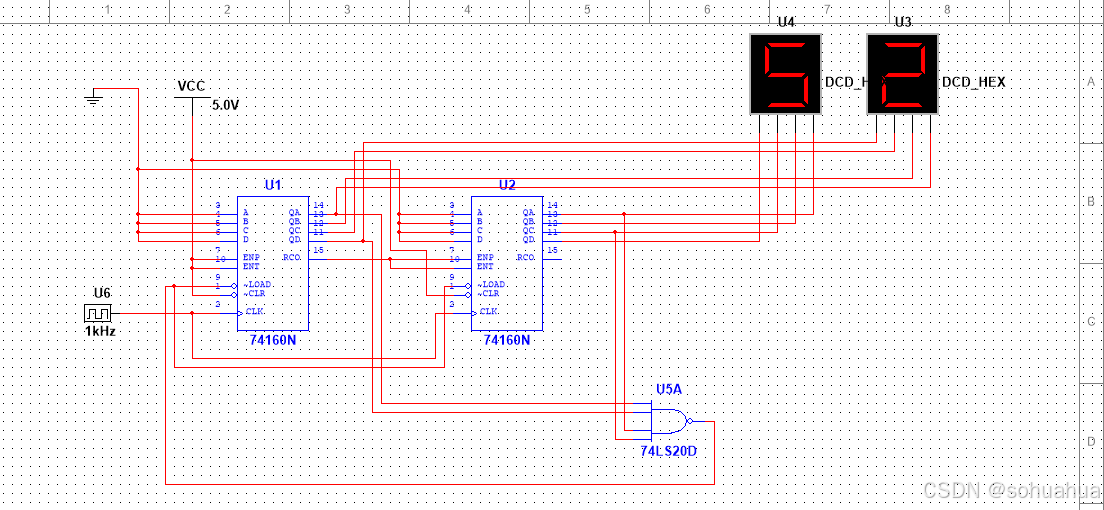

设计原理图

3、元器件的具体型号的功能及引脚说明

74160N 是十进制加计数器, 它有异步清零、 同步预置数等功能。

引脚说明:

电源:VCC

地:GND

四个数据输入端:P0、P1、P2、P3

时钟:CP

使能端:EP、ET

进位输出:TC

置数端:PE非

清零端:R非

输出:Q0、Q1、Q2、Q3

74ls20是常用的双4输入与非门集成电路,常用在各种数字电路和单片机系统中,其逻辑功能是完成四个输入的逻辑与非计算功能。 74ls20的引脚图如下: 74ls20包括两个4输入与非门,内含两组4与非门。

![]()

4、系统工作原理

工作原理:使用两片十进制74160,通过同步置数的方法实现0~59这60个状态,最终通过将输出端口与七段数码管相连接,显示结果完成实验。

连接过程:

两片74160的ABCD端接地、CLK都与1kHZ时钟相连;

第一片的LOAD、CLR、ENP、ENT接电源,QA(引脚14)和QD(引脚11)分别接在74ls20的引脚1和引脚2;

第二片的ENP和ENT与第一片的CO端连接,LOAD与第一片的LOAD 连接,CLR接电源,QA(引脚14)和QC(引脚10)分别接在74ls20的引脚4和引脚5;

74LS20的输出端Y(引脚6)与第二片的LOAD连接;

第一个的七段数码管的ABCD端与第二片74160的QAQBQCQD分别连接;

第二个的七段数码管的ABCD端与第一片74160的QAQBQCQD分别连接。

仿真图:

电路连接图:

5、设计过程中遇到的问题及解决方法

(1)芯片引脚个数与数字电路实验平台的模块不对应

解决方法:选择与实验所需芯片引脚个数相同的模块

(2)线路连接好后无法查看实验结果

解决方法:要将芯片的输出与七段数码管连接

(3)七段数码管显示乱码

解决方法:数码管的端口要与芯片的输出端口一一对应,列如:Qa与Da连接,这里注意要与multisim仿真做区分

(4)数码管显示过快无法肉眼查看结果是否正确

解决方法:将时钟与频率较小的相连,例如1hz

(5)计数器出现60

解决方法:因为选用的是同步置数法没有过渡态,所以应该选用0~59这60个状态。将60改为59解决了这个问题。

6、系统的优缺点及进一步改进措施。

同步电路优缺点:

优点:

a、有利于仿真器的仿真;

b、可以使所设计的系统成为 100% 的同步时序电路,有利于时序分析,而且可综合出较高的 Fmax;

c、由于只在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的复位毛刺。

缺点:

a、复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。同时还要考虑诸如 clk skew 、组合逻辑路径延时 、复位延时等因素(所以复位信号有时需要脉冲展宽,用以保证时钟有效期间有足够的复位宽度);

b、由于大多数的逻辑器件的目标库内的 DFF 都只有异步复位端口,所以,倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会一方面额外增加FPGA内部的逻辑资源,另一方面也增加了相应的组合逻辑门时延。

异步复位优缺点:

优点:

a、大多数目标器件库的 DFF 都有异步复位端口,那么该触发器的复位端口就不需要额外的组合逻辑,这样就可以节省资源;

b、设计相对简单;

c、异步复位信号识别方便(电路在任何情况下都能复位而不管是否有时钟出现)。

缺点:

a、最大的问题在于它属于异步逻辑,问题出现在复位释放时,而不是有效时,如果复位释放接近时钟有效沿,则触发器的输出可能进入亚稳态(此时 clk 检测到的 rst_n 的状态就会是一个亚稳态,即是0是1是不确定的),从而导致复位失败。

b、可能因为噪声或者毛刺造成虚假复位信号(比如以前的游戏机玩到一半突然复位)(注意:时钟端口、清零和置位端口对毛刺信号十分敏感,任何一点毛刺都可能会使系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要考虑的问题);

c、静态定时分析比较困难。

d、对于 DFT (Design For Test可测性设计)设计,如果复位信号不是直接来自于 I/O 引脚,在 DFT 扫描和测试时,复位信号必须被禁止,因此需要额外的同步电路。

三、课程设计题目3:八选一数据选择器

1、设计任务及功能

(1、安装ModelSim软件

(2、建立work库及新建工程

在建立工程(project)前,先建立一个工作库(library),一般将这个 library 命名为work。尤其是第一次运行 modelsim 时,是没有这个“work”的。但我们的 project一般都是在这个 work 下面工作的,所以有必要先建立这个 work。 File -> new -> library,接下来新建工程File -> new -> project

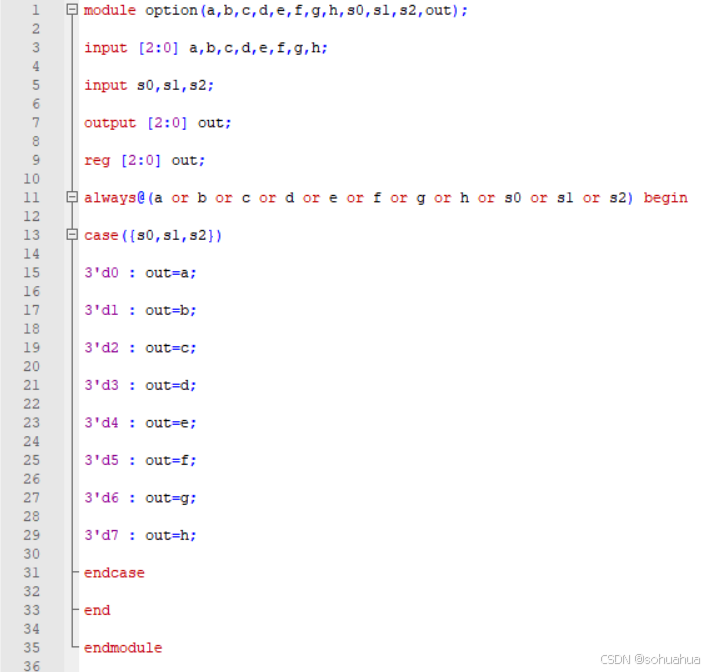

(3、编写Verilog语言代码,描述4选1数据选择器的功能。

(4、用Verilog语言编写Test Bench测试程序。

(5、生成测试波形图

2、设计代码及仿真代码

(1)设计代码

module test(a,b,c,d,e,f,g,h,s0,s1,s2,out);

input [2:0] a,b,c,d,e,f,g,h;

input s0,s1,s2;

output [2:0] out;

reg [2:0] out;

always@(a or b or c or d or e or f or g or h or s0 or s1 or s2) begin

case({s0,s1,s2})

3'd0 : out=a;

3'd1 : out=b;

3'd2 : out=c;

3'd3 : out=d;

3'd4 : out=e;

3'd5 : out=f;

3'd6 : out=g;

3'd7 : out=h;

endcase

end

Endmodule

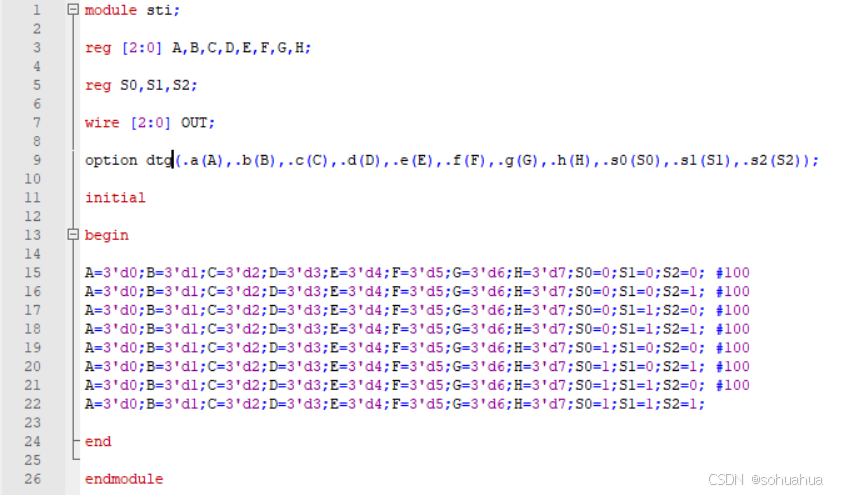

- 测试代码

module test_tb;

reg [2:0] A,B,C,D,E,F,G,H;

reg S0,S1,S2;

wire [2:0] OUT;

test mux(A,B,C,D,E,F,G,H,S0,S1,S2,OUT);

initial

begin

A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=0;#100

A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=1; #100

A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=0; #100

A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=1; #100

A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=0; #100

A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=1; #100

A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=1;S2=0; #100

A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=1;S2=1;

end

endmodule

3、设计过程

5、设计过程中遇到的问题及解决方法

(1)测试代码的波形图时objects为空。

解决方法:调用出现错误。调用时应与设计代码的文件名一致。

(2)波形错误。

解决方法:d表示十进制b表示二进制。要与数字对应一致。

6、优缺点及进一步改进措施。

1.代码的变量定义可以去掉【2:0】即位宽,以及将后面的更改为一致,以防报错。

2.调用时可以使用

test mux(.a(A),.b(B),.c(C),.d(D),.e(E),.f(F),.g(G),.h(H),.s0(S0),.s1(S1),.s2(S2));

用法,这种调用方法的优点是其中的调用变量可以不按顺序。

1、设计任务及功能

(1、安装ModelSim软件

(2、建立work库及新建工程

在建立工程(project)前,先建立一个工作库(library),一般将这个 library 命名为work。尤其是第一次运行 modelsim 时,是没有这个“work”的。但我们的 project一般都是在这个 work 下面工作的,所以有必要先建立这个 work。 File -> new -> library,接下来新建工程File -> new -> project

(3、编写Verilog语言代码,描述4选1数据选择器的功能。

(4、用Verilog语言编写Test Bench测试程序。

(5、生成测试波形图

2、设计代码及仿真代码

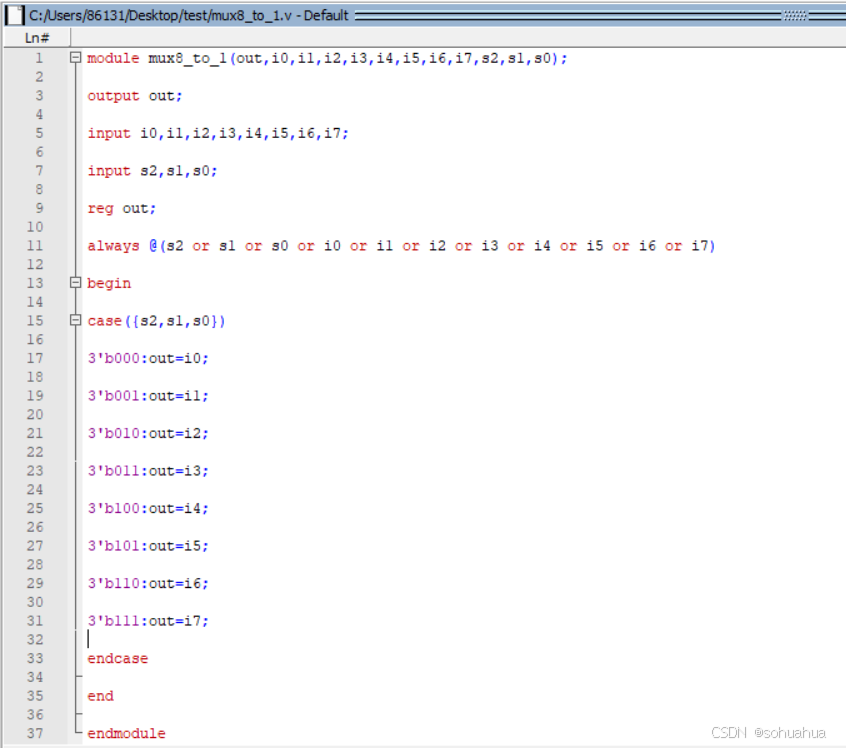

设计代码:

module mux8_to_1(out,i0,i1,i2,i3,i4,i5,i6,i7,s2,s1,s0);

output out;

input i0,i1,i2,i3,i4,i5,i6,i7;

input s2,s1,s0;

reg out;

always @(s2 or s1 or s0 or i0 or i1 or i2 or i3 or i4 or i5 or i6 or i7)

begin

case({s2,s1,s0})

3'b000:out=i0;

3'b001:out=i1;

3'b010:out=i2;

3'b011:out=i3;

3'b100:out=i4;

3'b101:out=i5;

3'b110:out=i6;

3'b111:out=i7;

defult:$dispiay("Invalid control signals");

endcase

end

endmodule

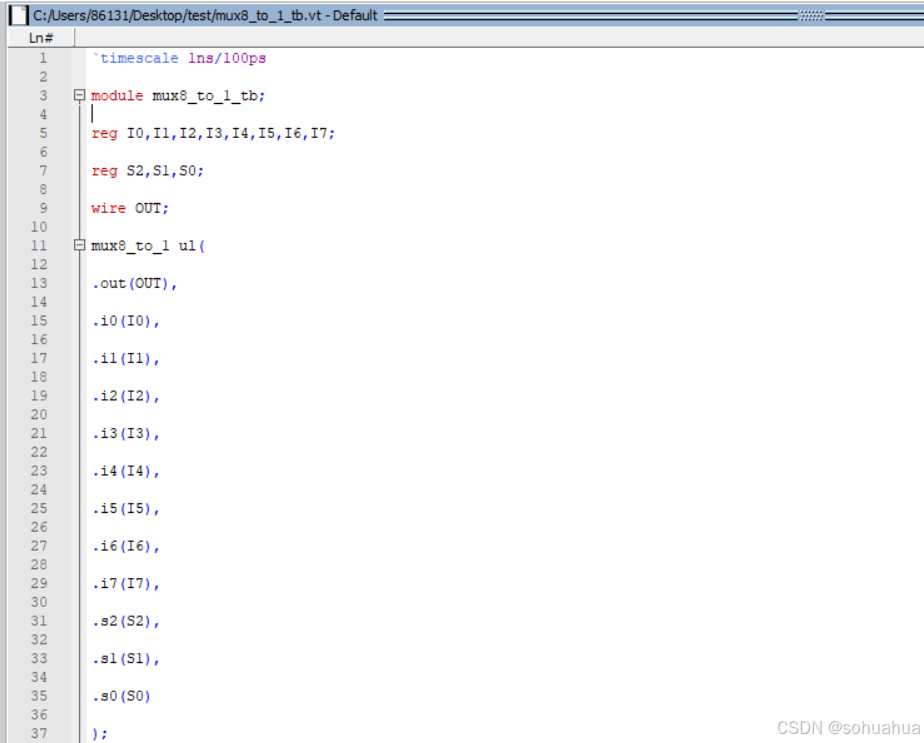

测试代码:

`timescale 1ns/100ps

module test_tb;

reg I0,I1,I2,I3,I4,I5,I6,I7;

reg S2,S1,S0;

wire OUT;

test(.out(OUT),.i0(I0),.i1(I1),.i2(I2),.i3(I3),.i4(I4),.i5(I5),.i6(I6),.i7(I7),.s2(S2),.s1(S1),.s0(S0));

initial

begin

I0=1;I1=0;I2=0;I3=1;I4=1;I5=1;I6=0;I7=0;

S2=0;S1=0;S0=0;

#10 S2=0;S1=0;S0=1;

#10 S2=0;S1=1;S0=0;

#10 S2=0;S1=1;S0=1;

#10 S2=1;S1=0;S0=0;

#10 S2=1;S1=0;S0=1;

#10 S2=1;S1=1;S0=0;

#10 S2=1;S1=1;S0=1;

end

endmodule

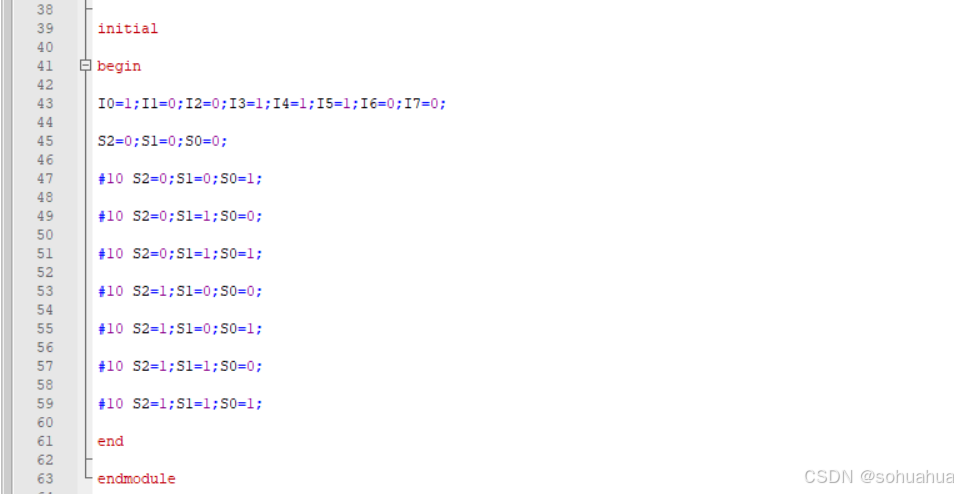

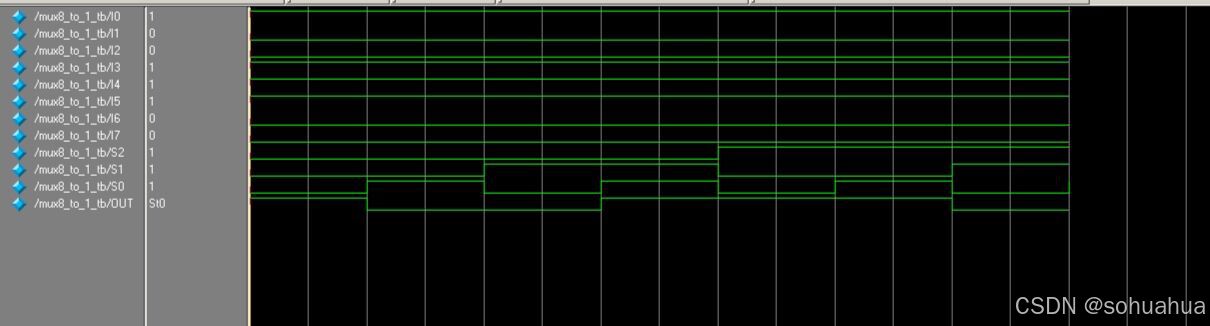

3、设计过程

5、设计过程中遇到的问题及解决方法

经过多次的练习,本次实验在操作过程中基本很流畅,没有再碰到对软件不够熟悉的情况。但是,本次实验结果却存在一定问题,例如,命名名字时不符合要求出现错误、端口的匹配问题,在写程序的时候误将位宽写在了变量名的后面,虽然程序能够运行但有警告,仿真波形是错误的,可见在写程序时警告有时也是致命的,这要求我们在学习的过程中思想一定要严谨!还有选择端口S2、S1、S0的波形没有出现,都是直线,当时在实验过程中没有找到问题所在,后来分析是时间的设置太短,改变时间后波形才出现。

6、优缺点及进一步改进措施。

书上说在模块外部输入可以是wire型或reg型,但在写程序时激励模块往往要初始化数据,所以编程时其类型往往声明为reg型。

总结与心得

通过这次实验,使我对通过这次课程设计,加强了我们动手、思考和解决问题的能力。在整个设计过程中,我们通过这个方案包括设计了并实现了电路的搭建,和芯片上的选择。使用了74LS161, 74LS151,74LS20等芯片,加深了我对芯片功能的理解。其次,我对modelsim的应用更加得心应手,深切的体会到了 verilog是一种描述性语言,这次实验总的来说是比较顺利的,但在过程中还是遇到了一些问题, 但是我明白了我们在书上所学的是远远不够的,更多的要我们自己去实践、探索、勤思考,只有这样我们才能把书本上的知识转化为属于我们自己的知识,才能在学习的道路上走的更远!

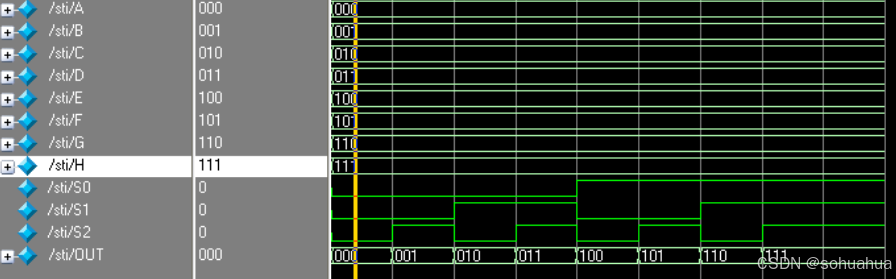

波形分析

1、八选一数据选择器 输入数据为

A=000,B=001,C=010,D=011,E=100,F=101,g=110,h=111;S0,S1,S2,为选择控制端,它们组成一个三位数,记为enable,控制数据的输出,其中S0为最高位,S1次之,S2为最低位。当enable=000,输出A; enable= 001,输出B;enable= 010,输出C;enable= 011,输出D;enable= 100,输出E;enable= 101,输出F;enable= 110,输出G;enable= 111,输出H 观察波形当enable=000时,输出为000即A;当enable=001时,输出为001,即B;当enable=010时,输出为010即C;当enable=011时,输出为011即D;当enable=100时,输出为100即E;当enable=101时,输出为101,即F;当enable=110时,输出为110即G;当enable=111时,输出为111即G,其结果与理论结果相吻合故验证该设计是正确的。

参考文献(10个以上)

modelsim使用方法

2.学习记录(持续学习中):异步清零和同步清零区别和各自优缺点。 异步复位和同步释放实现方法。_异步复位和异步清零的区别-CSDN博客

暂时的异步同步优缺点

3.Verilog中Case语句_verilog case-CSDN博客

case表达式用法

4.【教学】modelsim独立仿真_哔哩哔哩_bilibili

modelsim基本使用方法

1.74151/74LS151 8选1数据选择器-CSDN博客

74151功能表

2.ModelSim的wave波形窗口在哪里打开_modelsim wave 界面打不开-CSDN博客

modelsim波形问题解决

3.verilog - ModelSim Error Loading Design - Stack Overflow

modelsim报错解决

4.https://www.baidu.com/s?ie=utf-8&f=8&rsv_bp=1&ch=&tn=15007414_9_dg&bar=&wd=modelsim%E4%B8%AD%E6%96%87%E6%B3%A8%E9%87%8A%E4%B9%B1%E7%A0%81&oq=HDL%25E6%25BF%2580%25E5%258A%25B1%25E7%25A8%258B%25E5%25BA%258F%25E6%2580%258E%25E4%25B9%2588%25E5%2586%2599&rsv_pq=ffc6917300049226&rsv_t=56d44Sx%2F7IFPLNWaRfYgeRWcFwSYffgSmsGr008ar4b%2B8oKR40gpjg8fYm0%2Fe6CpD2lrYw&rqlang=cn&rsv_enter=1&rsv_sug3=50&rsv_sug1=18&rsv_sug7=100

解决modelsim注释乱码问题

5.https://wenku.baidu.com/view/19763793f524ccbff12184a6.html

Multisim中英文元件库对照表

6.modelsim—Altera显示 “no design loaded”_skullandbones_新浪博客 (sina.com.cn)

解决no design load报错

4844

4844

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?