目录

语言要素

空白符

空白符包含空格符、制表符、换行符,换页符等,它们的存在使程序更具与易读性,不影响编译。

注释符

单行注释:// 内容(不可换行)

多行注释:/* 内容(可换行)*/

标识符

标识符对大小写敏感,且开头字符须为字母或下划线。其是由任意的字母、数字、下划线、$符号组成。

转移标识符

以‘\’符号作为开头,将不合法的标识符转换为合法的标识符。

关键字

在verilog中,所有的关键字都是小写的,他们是事先定义好的确定符,用来组织语言结构。例如:ALWAYS是标识符,而always才是关键字。

数值

以下是在Verilog HDL中四种基本的逻辑数值状态

| 状态 | 含义 |

| 0 | 低电平、逻辑0、“假” |

| 1 | 高电平、逻辑1、“真” |

| x/X | 不确定状态 |

| z/Z | 高阻态 |

整数

表示方法:+/-<size><base_format><number>

- size:位宽,不能为表达式

- base_foramt:进制数的基数符号

- number:可用下划线分割 例如:4‘b10_11 //4位二进制数1011

实数

(1)十进制表示方法:小数点两边必须都有数字

(2)科学计数法

数据类型

主要物理数据类型:连线型、寄存器型、存储器型。

使用四种逻辑电平(0,1,x,z)和八种信号强度对实际电路进行建模

四种逻辑电平是对信号的抽象

信号强度表示数字电路中不同强度的驱动源,用来解决不同驱动下的赋值冲突。

(强度自上而下,强度递减)

连线型

声明:<net_declaration><drive_strength><range><delay>[list_of_variables]

- net_declaration包括 wire,tri,tri0,tri1,wand,triand,trior,wor中的任意一种。

- drive_strength表示连线变量的驱动强度。

- range 用来指定数据为标量或矢量。若该项默认,表示数据类型为1位的标量,超过1位则为矢量形式。

- delay指定仿真延迟时间

- list_of_variables变量名称,一次可定义多个,之间用逗号隔开。

寄存器型

- reg型是数据存储单元的抽象类型,其对应的硬件电路元件具有状态保持作用,能够存储数据,如触发器、锁存器等。

- reg型常用于行为级描述,有过程赋值语句对其进行赋值。

- reg型变量是无符号数,若将一个负数赋值给reg变量,则自动转换成二进制补码形式。

声明:reg<range><list_of_variables>

- range位宽 默认为1。

- list_of_variables变量名称,一次可定义多个,之间用逗号隔开。

存储器型

可以用来描述RAM ROM reg文件。

声明:reg<renge1><name_of_register><range2>

- range1 位宽默认1。

- range2 寄存器个数,存储深度,格式[a,b],个数为a-b+1。

- name_of_register变量名称,一次可定义多个,之间用逗号隔开。

抽象数据类型

整型 integer<list_of_register_variables>

例子:

integer index;//32位有符号整数

integer i[22:0];//整型数组有23位

时间型 timeinteger<list_of_register_variables>

(用于模拟时间的存储与计算处理)

例子:

time a;//一个64位的时间型变量

实型 real<list_of_variables>

(浮点数数值,用于延迟时间的计算)

参数型 parameter 参数=表达式1,参数=表达式2,参数=表达式3.....

(常量,提高程序可读性与维护性)

例子:

parameter a=1,b=1;

运算符和表达式

优先级:单目运算符>双目运算符>多目运算符

算数操作符

+、-、*、÷、取模(%)

1.计算结果的位宽是最长操作数的位数。

2.计算结果在超出最长操作数位数时,超出的高位被舍去。

例子:a=4'b1111;

b=3'b011;

$display("%b",a*b);//结果为4‘b1101,高位被舍去了。

关系操作符

>、<、>=、<=

结果为1bit 0、1、x。

相等关系操作符

==、!=、===、!==

比较结果三种,即1、0、x。

逻辑运算符

&&、||、!

操作数中存在不定态x,则逻辑运算的结果也是不定态的。

按位运算符

~、&、|、^、^~

归约运算符(缩位运算符)

单目运算符,在操作数内按位操作

&、|、异或^,以及相应的非操作 ~&、~|、^~、~^

移位运算符

左移运算符<<、右移运算符>>

用0补空位

条件运算符

表达式:<条件表达式>?<表达式1>:<表达式2>

条件表达式的计算结果为真时,执行表达式1;结果为假时,执行表达式2。

连接和复制运算符

连接运算符{},复制运算符{{}}。

reg[2:0]a; reg[3:0]b; reg[5:0]c; reg[7:0]e; a=3'b101; b=4'b1110; c={2{a}}; e={a,b}; $display("&b",c);//结果6'b101101 $display("&b",e);//结果8'b01011110

模块的基本概念

模块

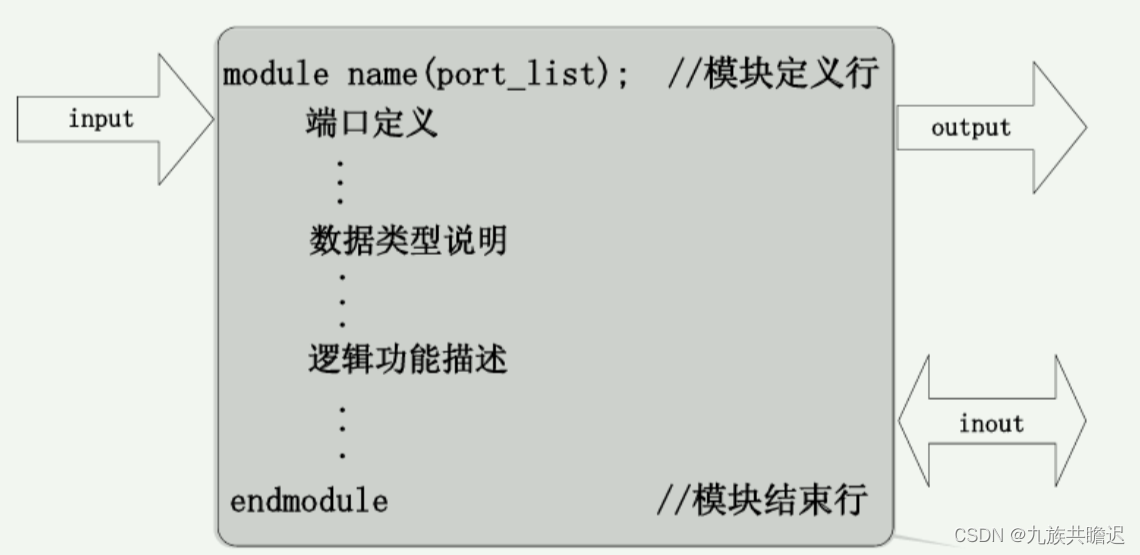

模块是verilog hdl的基本单元,它代表一个基本的功能块,用于描述某个设计的功能或结构以及其他模块通信的外部接口。

一个模块主要包括:模块的开始与结束、模块端口定义、模块数据类型说明和模块逻辑功能描述这几个基本部分。

- 模块的开始与结束:以关键词module开始,以关键词endmodule结束的一段程序,其中模块开始语句必须要以分号结束。

- 端口定义:用来定义端口列表里的变量哪些是输入 (input)、输出(output)和双向端口 (inout)以及位宽的说明。

- 数据类型说明:数据类型在语言上包括wire、reg、memory和parameter等类型,用来说明模块中所用到的内部信号、调用模块等的声明语句和功能定义语句。

- 逻辑功能描述:用来产生各种逻辑(主要是组合逻辑和时序逻辑)。

端口

模块的端口可以是输入端口 Cinput)、输出端口 (output)或双向端口 Cinout)。

模块定义时规定的端口名。格式如下:

模块名(连接端口1信号名,连按端口2信号名……);严格按端口顺序对应,提高了程序的可读性和可移植性。

1610

1610

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?