这里我用的是红帽子的虚拟机里面的cadence软件进行版图绘制过程(新手小白,希望能得到更多的指正)。

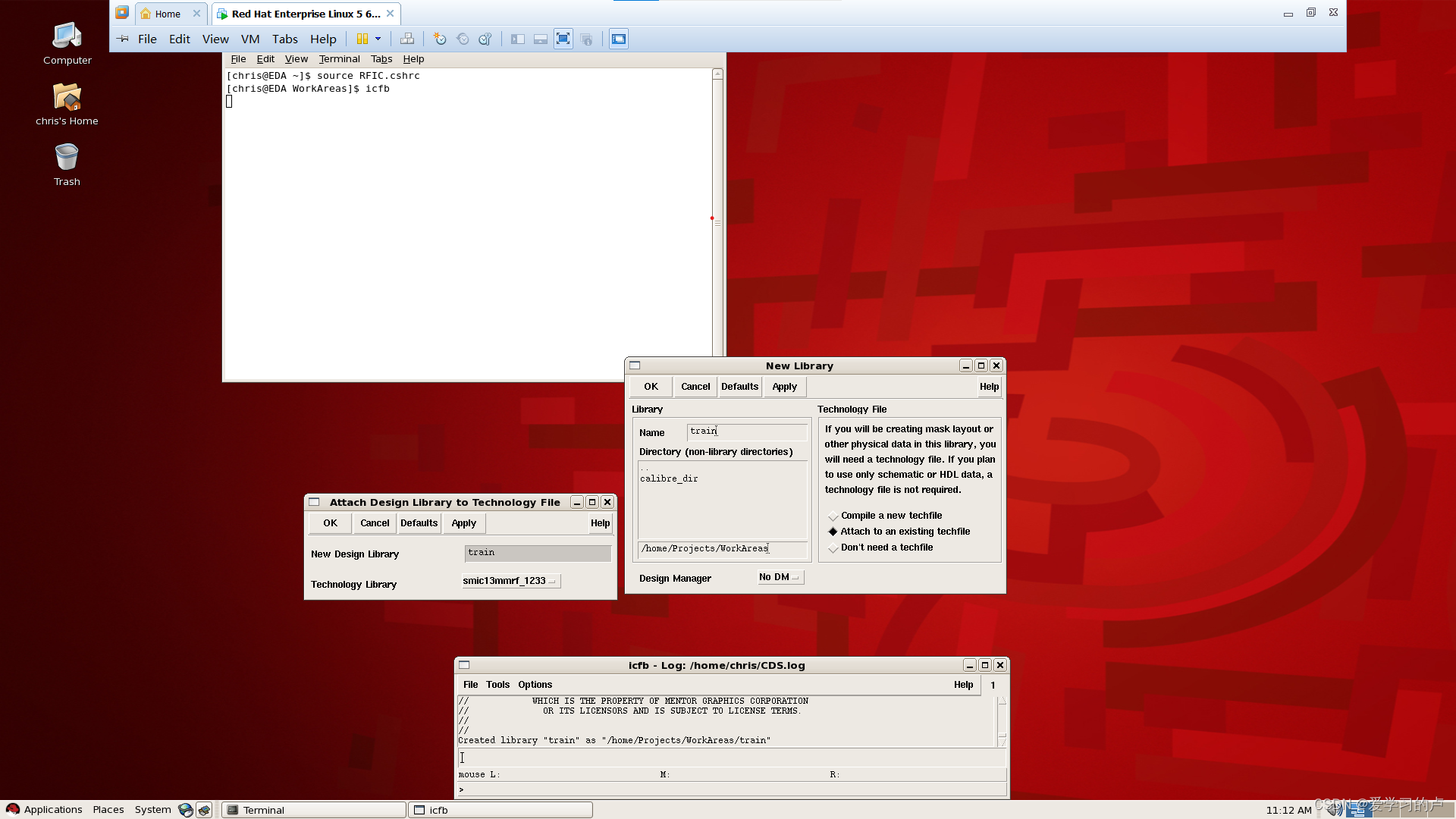

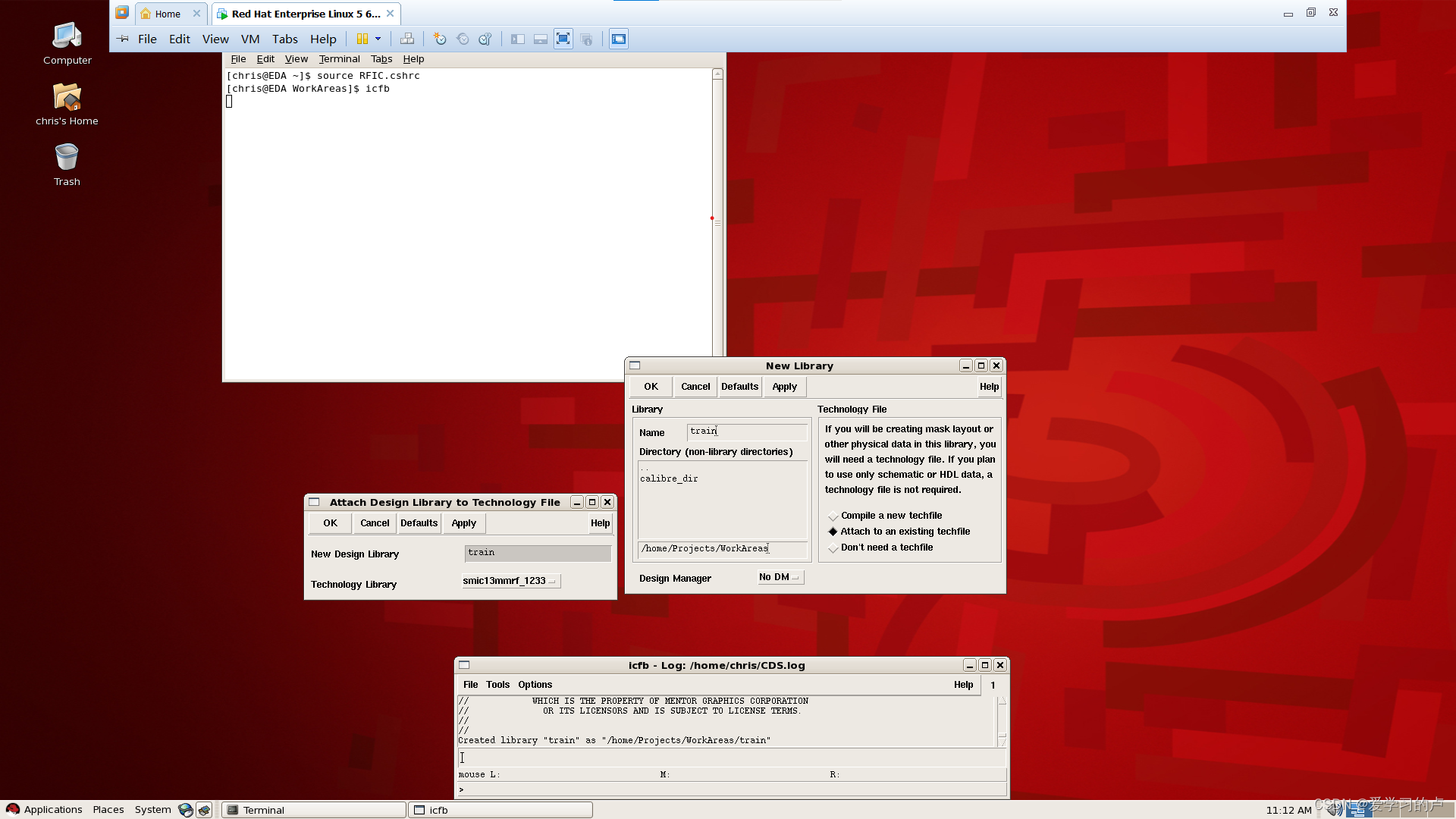

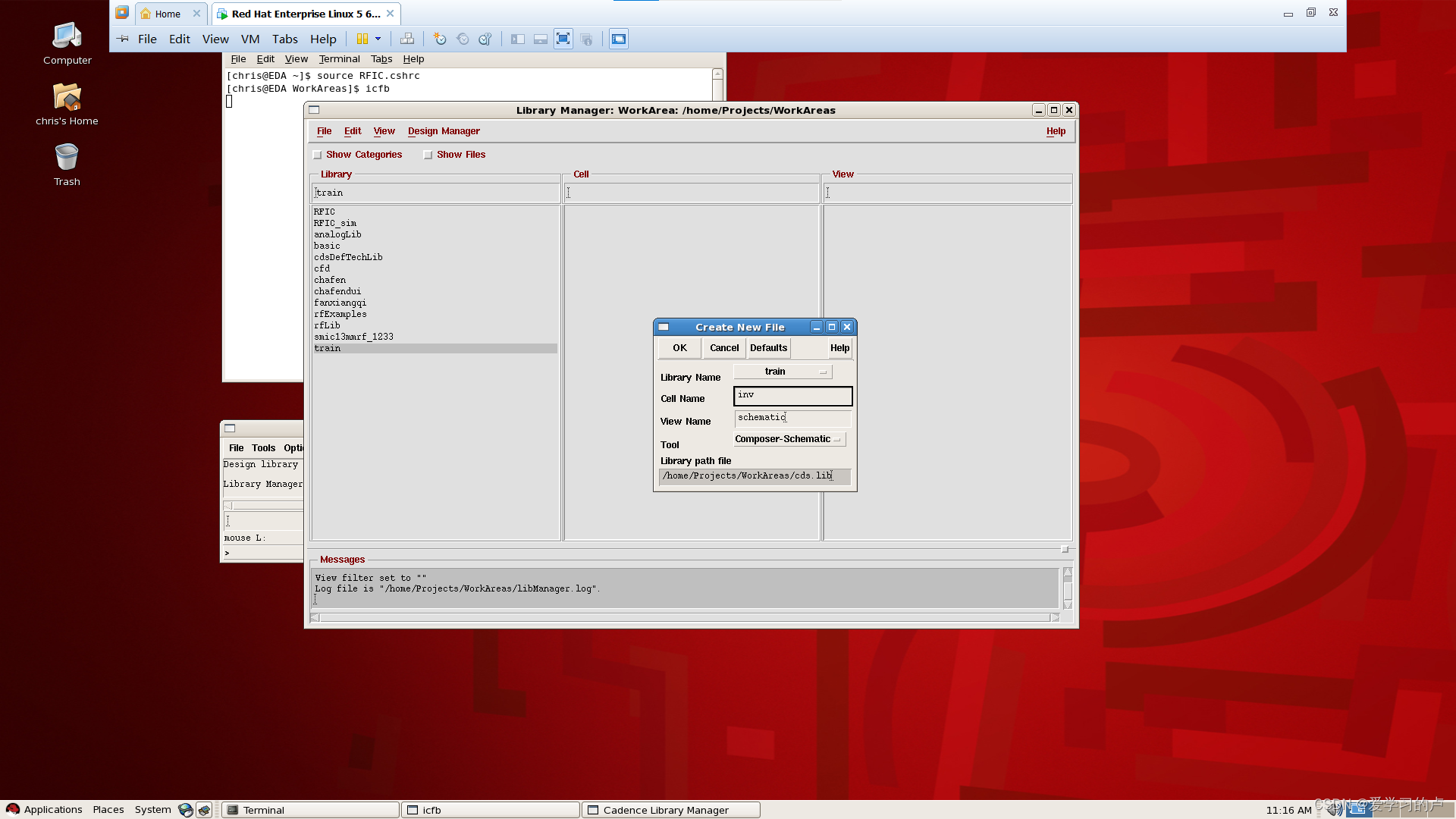

首先建立库,这里我建立了名为train的库,以后所有的工作都在train这个库里执行。

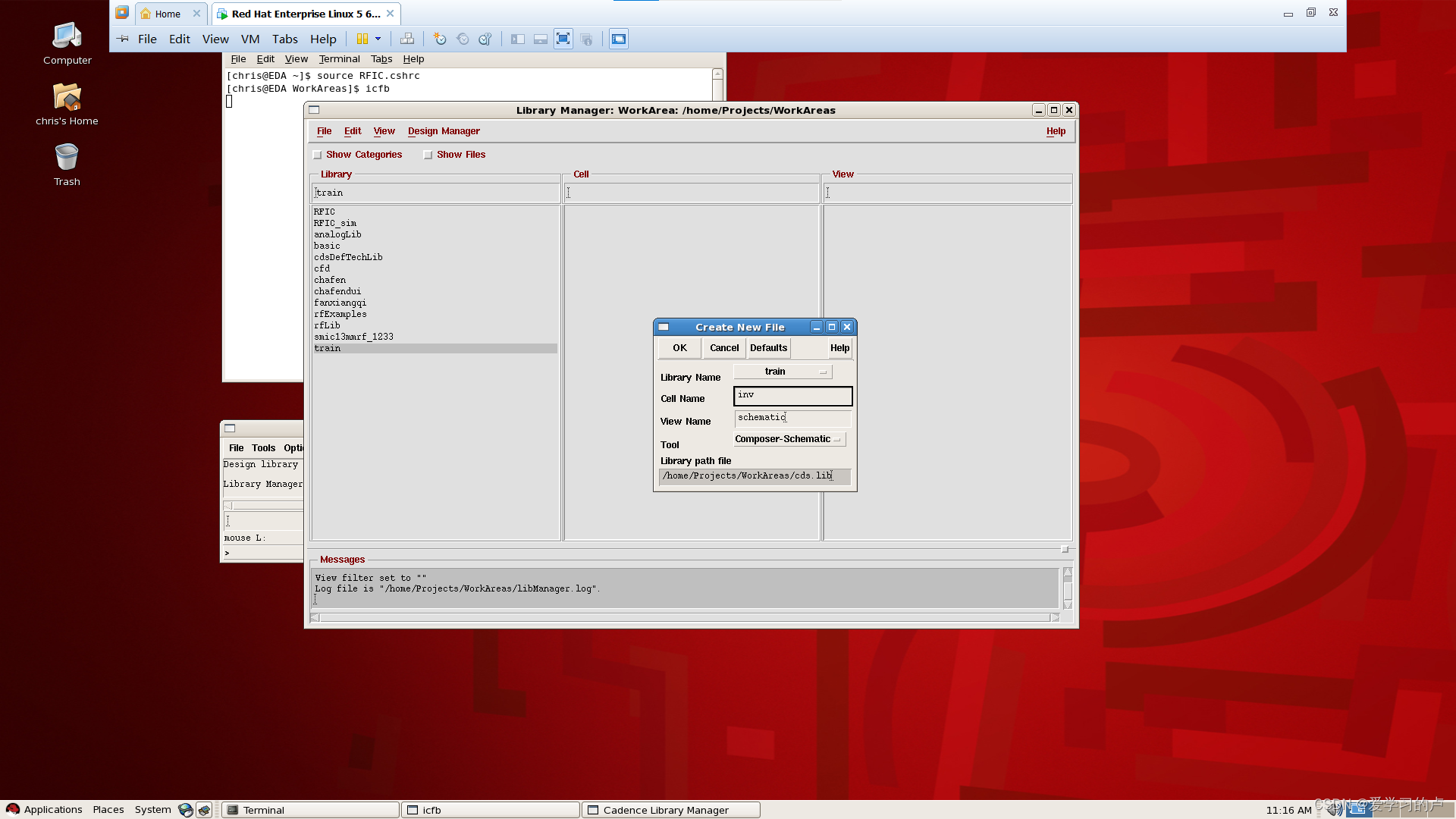

在这个train库中建立本次实验目标——反相器,点击“ok”开始绘制原理图。

在这个train库中建立本次实验目标——反相器,点击“ok”开始绘制原理图。

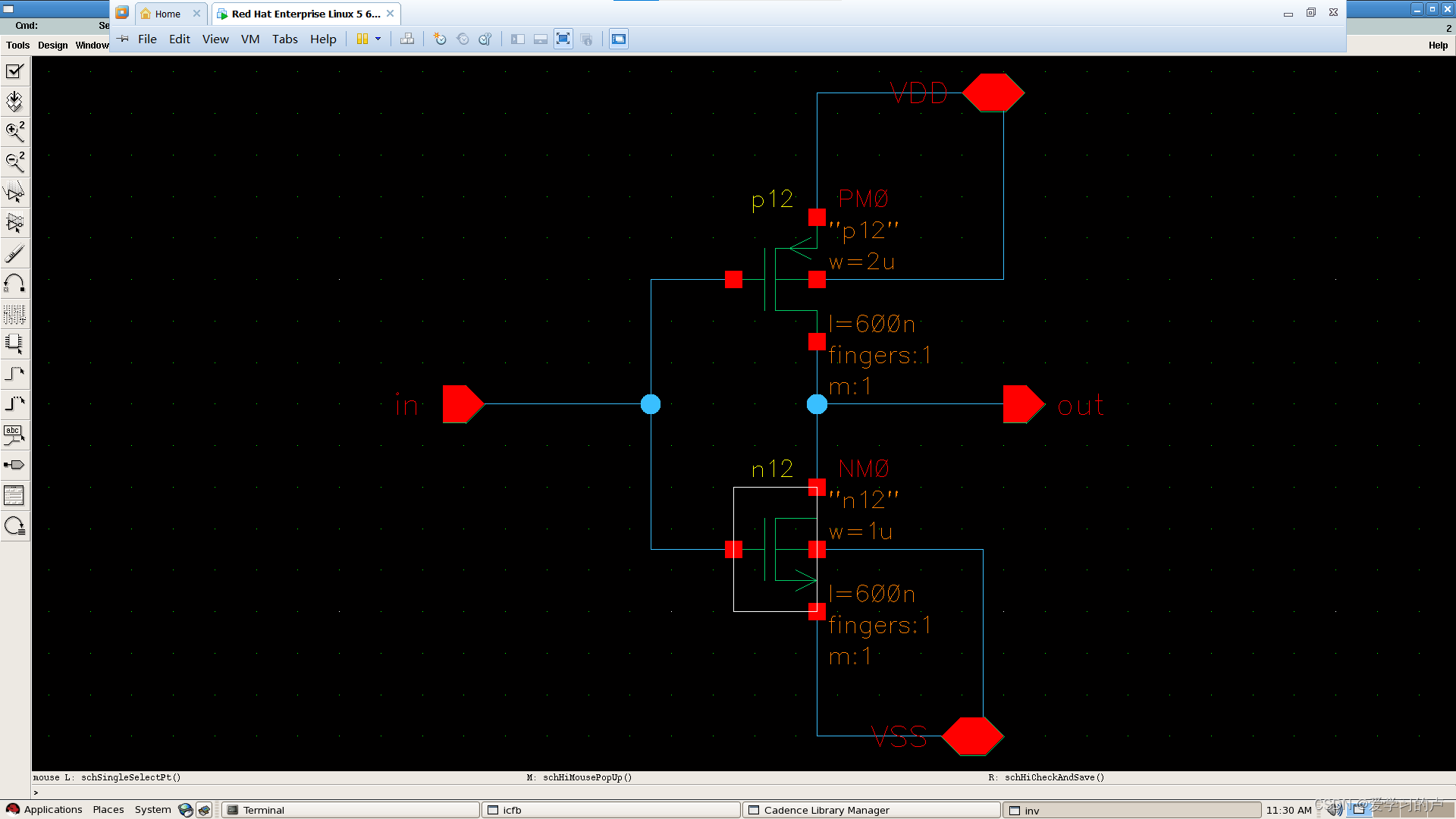

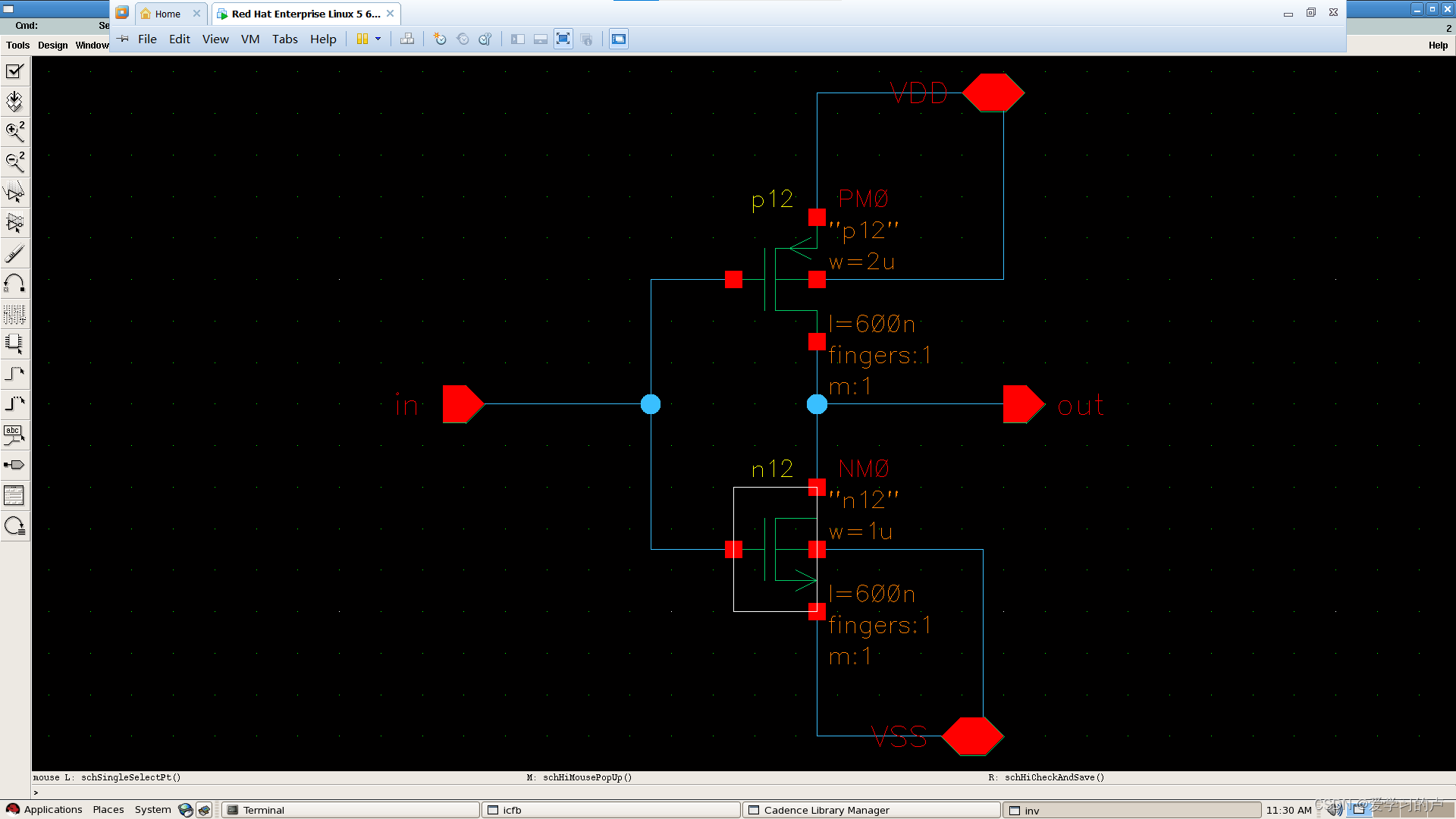

check and save看是否出现错误。

layout XL转版图绘制

将原理图导入至版图,这里我将衬底显示出来,并且默认左源右漏。(切记先调格点,这里我将格点调制0.005)。

这里我用的是红帽子的虚拟机里面的cadence软件进行版图绘制过程(新手小白,希望能得到更多的指正)。

首先建立库,这里我建立了名为train的库,以后所有的工作都在train这个库里执行。

在这个train库中建立本次实验目标——反相器,点击“ok”开始绘制原理图。

在这个train库中建立本次实验目标——反相器,点击“ok”开始绘制原理图。

check and save看是否出现错误。

layout XL转版图绘制

将原理图导入至版图,这里我将衬底显示出来,并且默认左源右漏。(切记先调格点,这里我将格点调制0.005)。

2120

2120

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?