目录

1. 反相器的原理图设计

2. 反相器的版图设计,DRC/LVS/PEX参数提取

一、版图设计

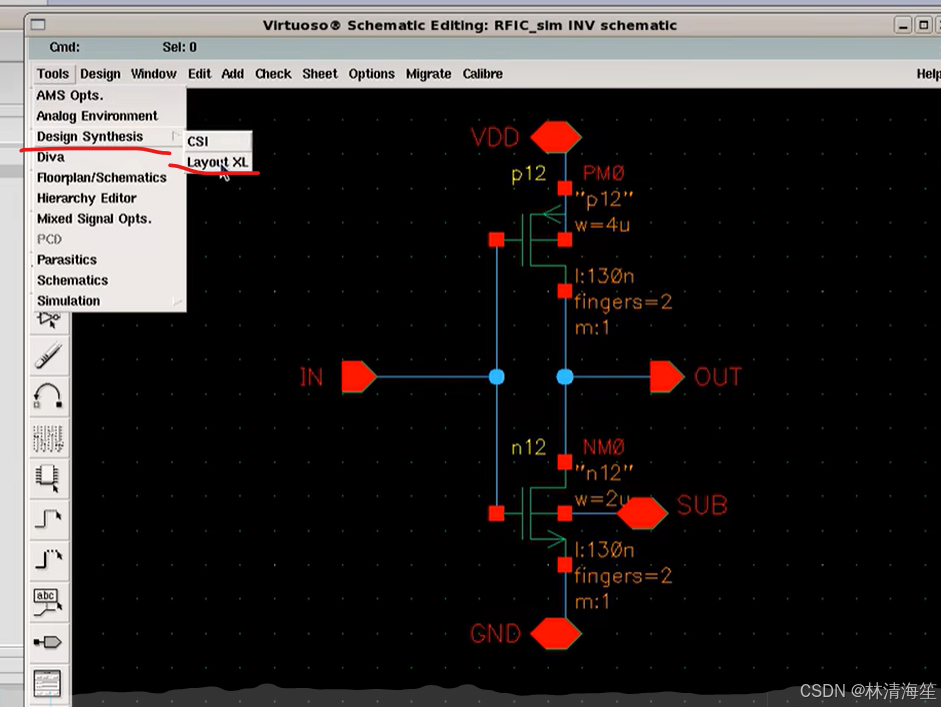

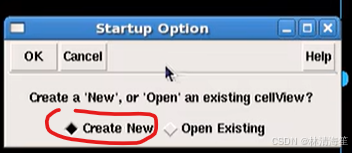

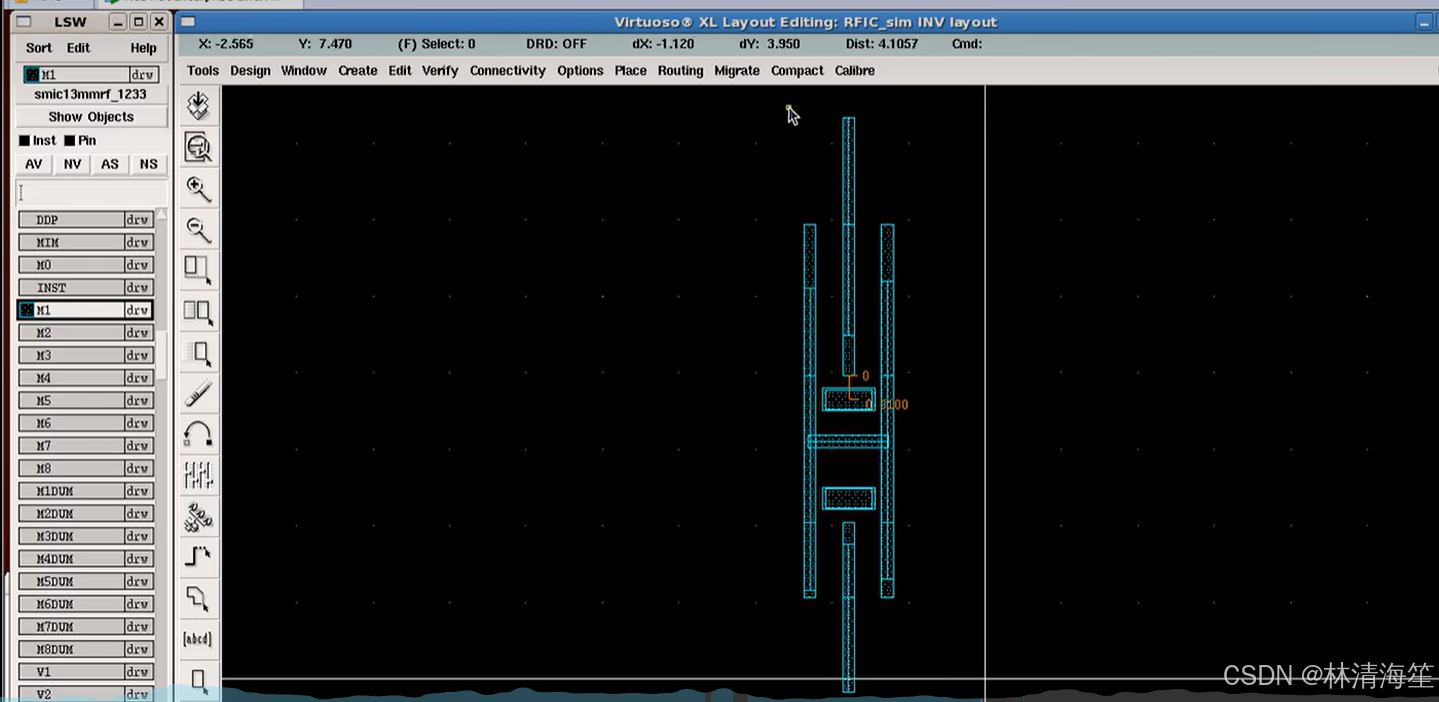

首先打开设计好的原理图,点击Tools-design synthesis-layout xl

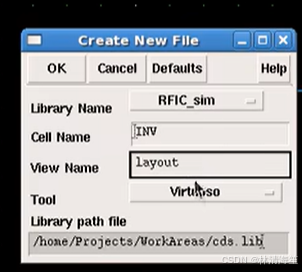

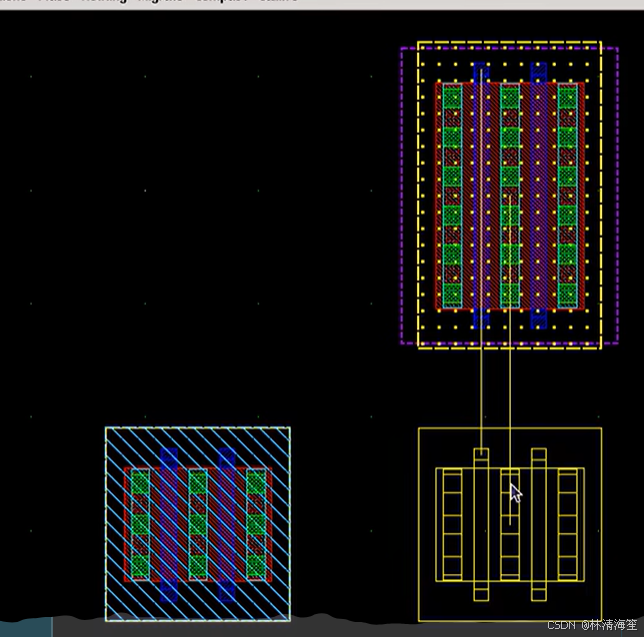

此时会有三个窗口,

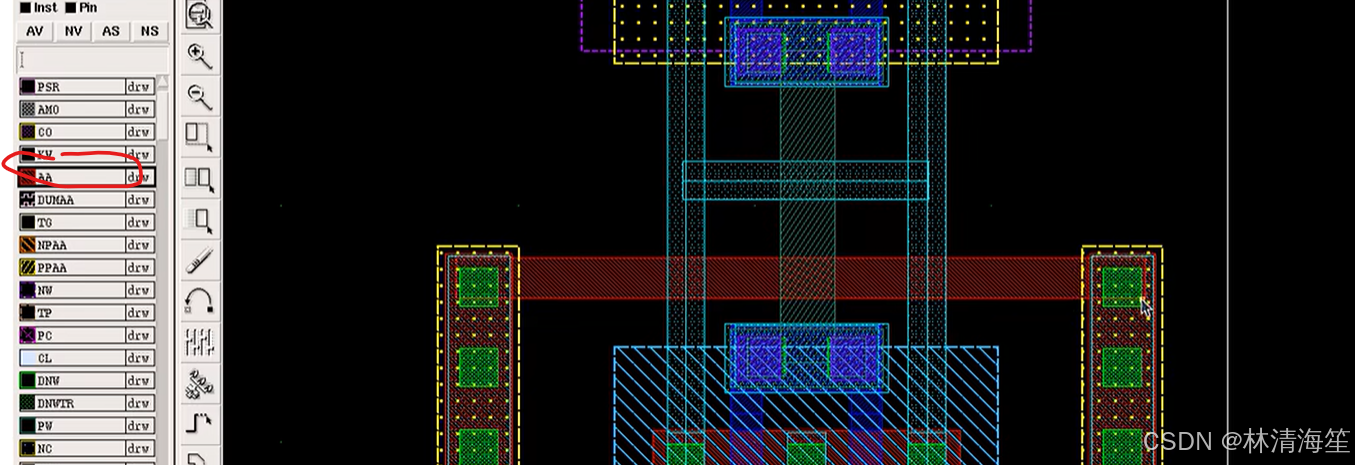

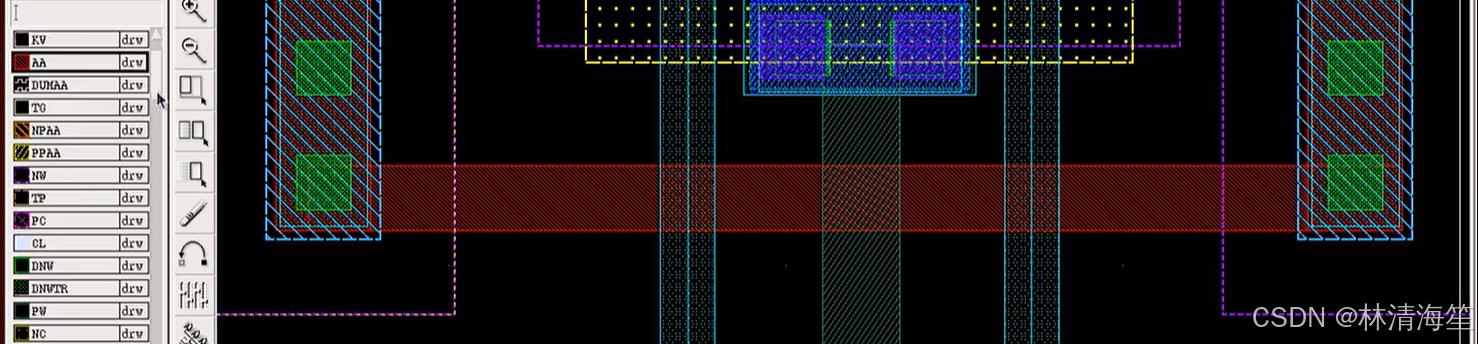

左边的窗口是层的属性LSW,这是工艺中做版图所有用到层的信息。

中间是原理图,右边是layout设计窗口,是一一对应的关系

1. LSW层级属性介绍

- AA:有源层

- NW:即N-Well层

- DNW:即Deep Nwell

- GT:即晶体管的栅极,gate层

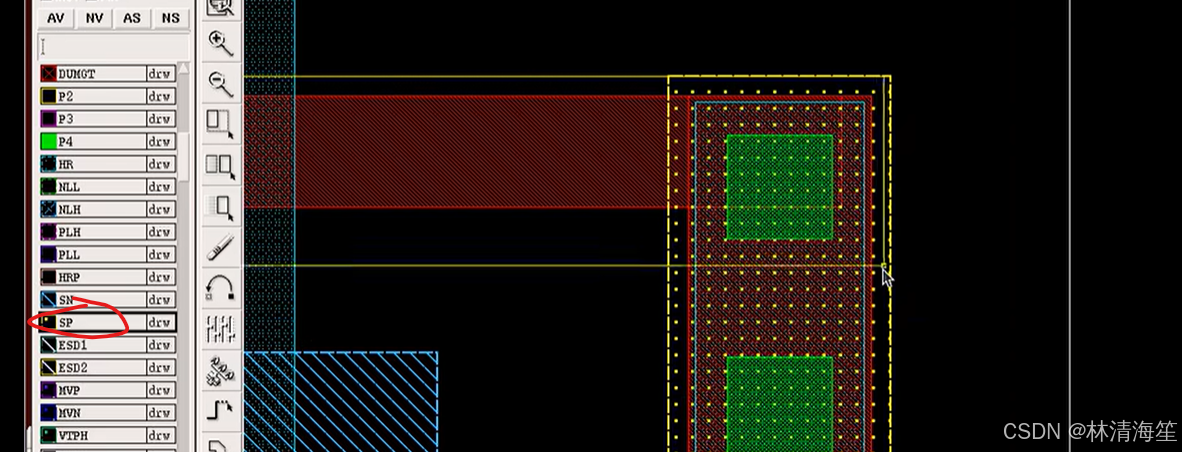

- SN:N型注入

- SP:P型注入

- M1:金属层,一般版图设计最多用到6层M6

- V1:过孔层,即金属1层到金属2层之间的过孔

- PSUB:标志层

- CTXT:文字层

- TM:顶层后金属

后缀为drw表示可以用来绘制的层

2. 调入原理图中元器件到版图中

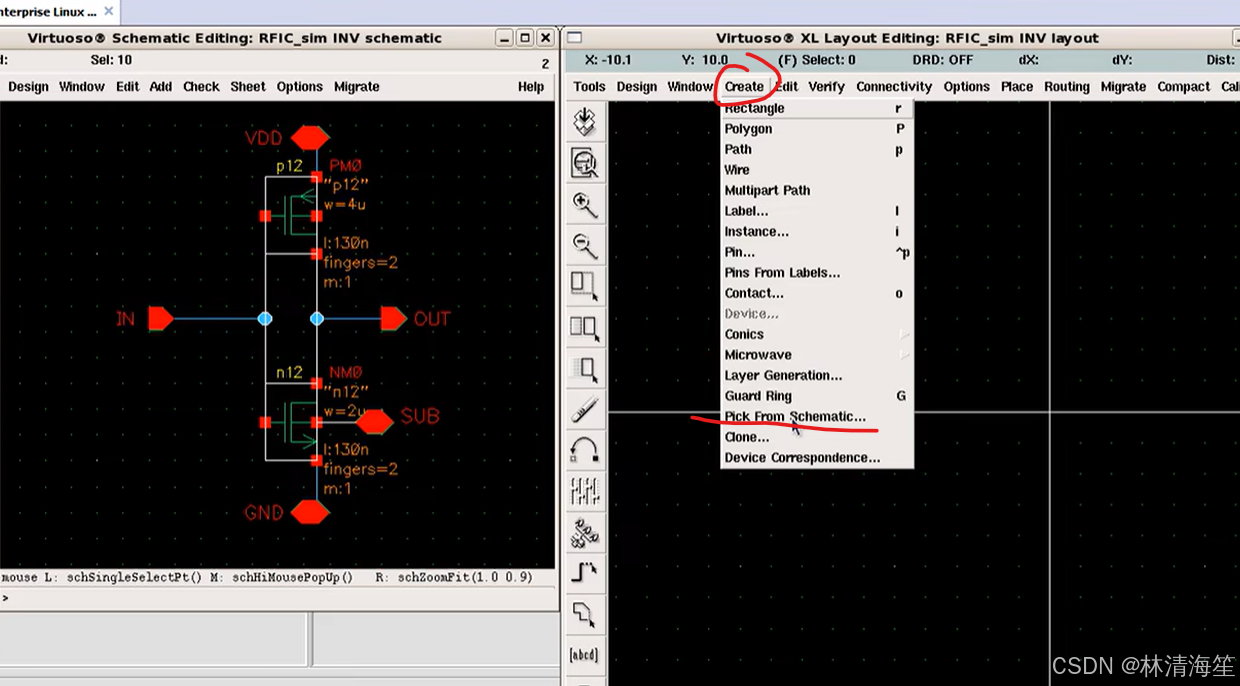

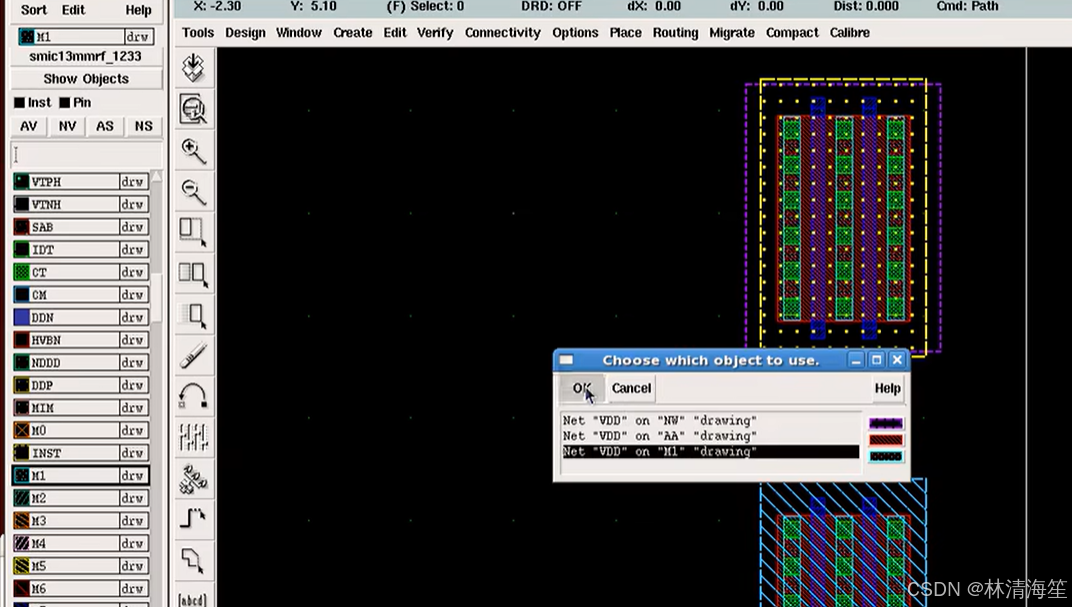

在原理图中,按住shift键,选择两个晶体管,

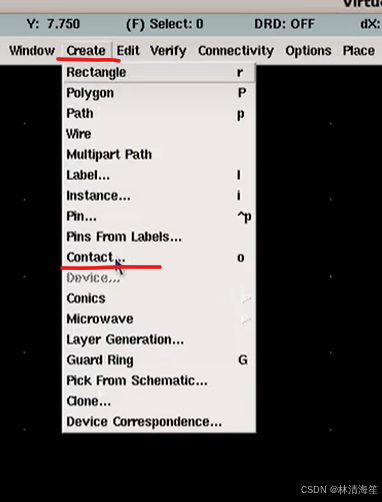

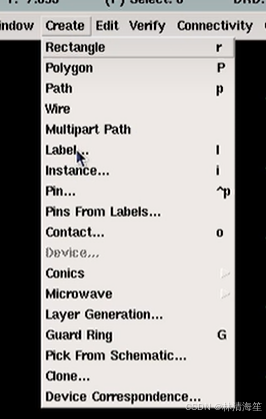

然后切换到layout的窗口中,选择Create——pick from schematic

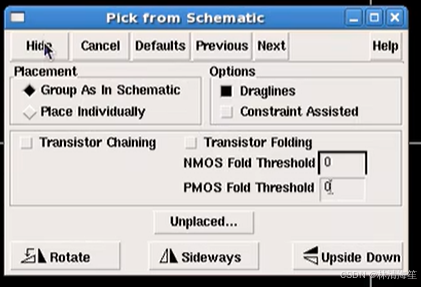

弹出的对话框选择默认设置,然后就可以在layout中放置元器件了

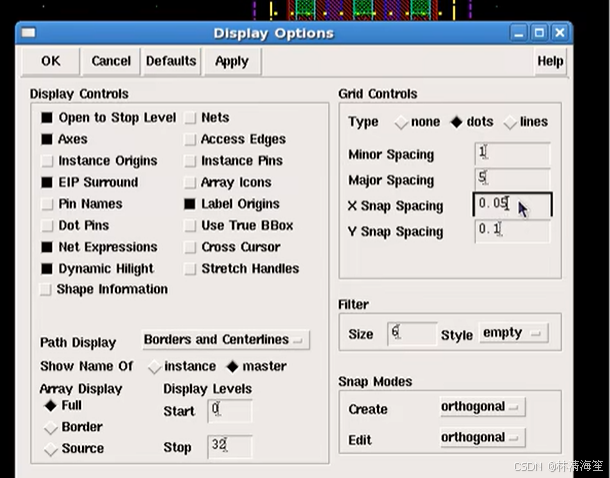

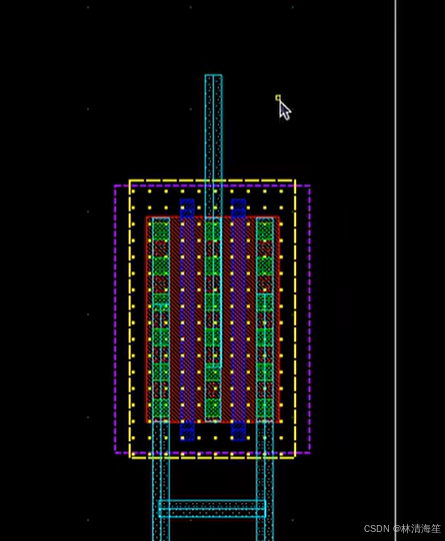

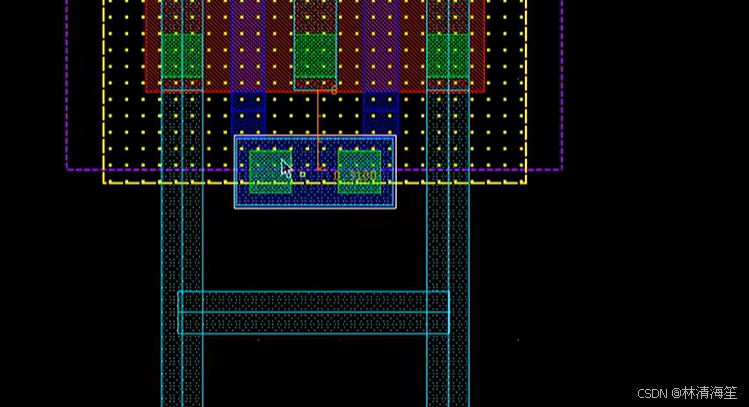

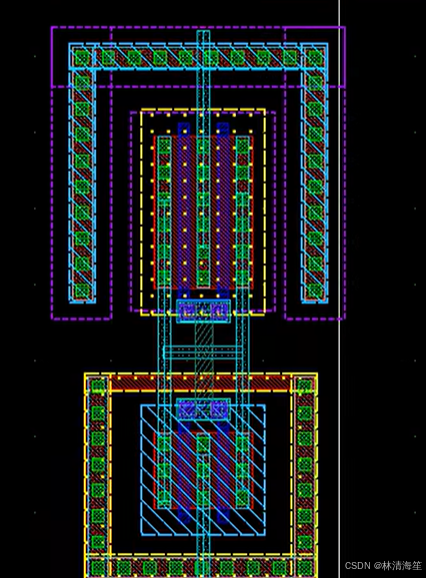

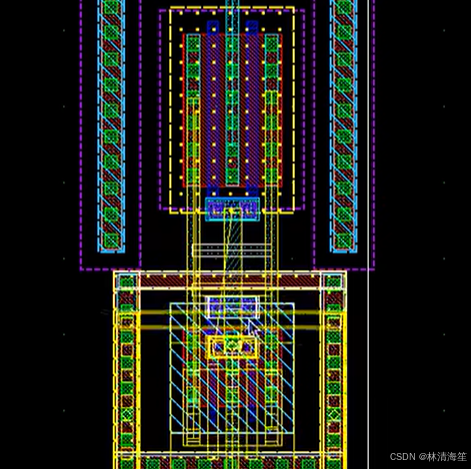

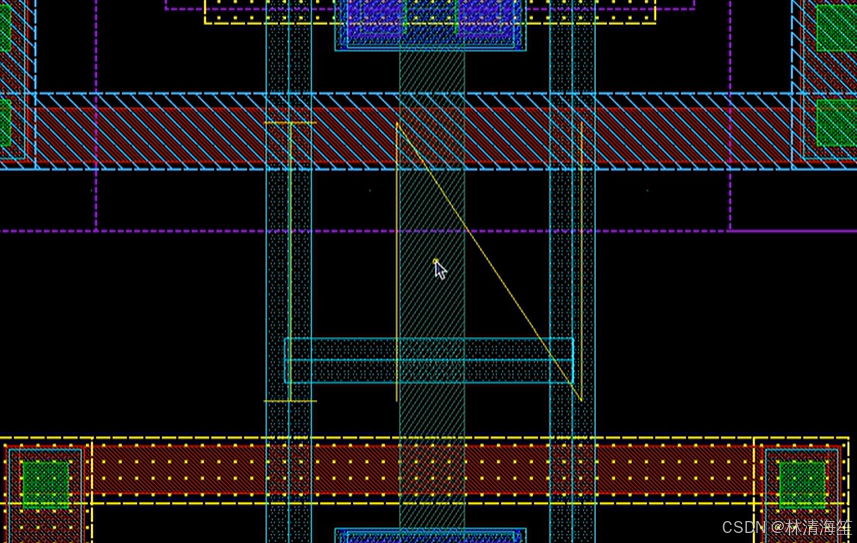

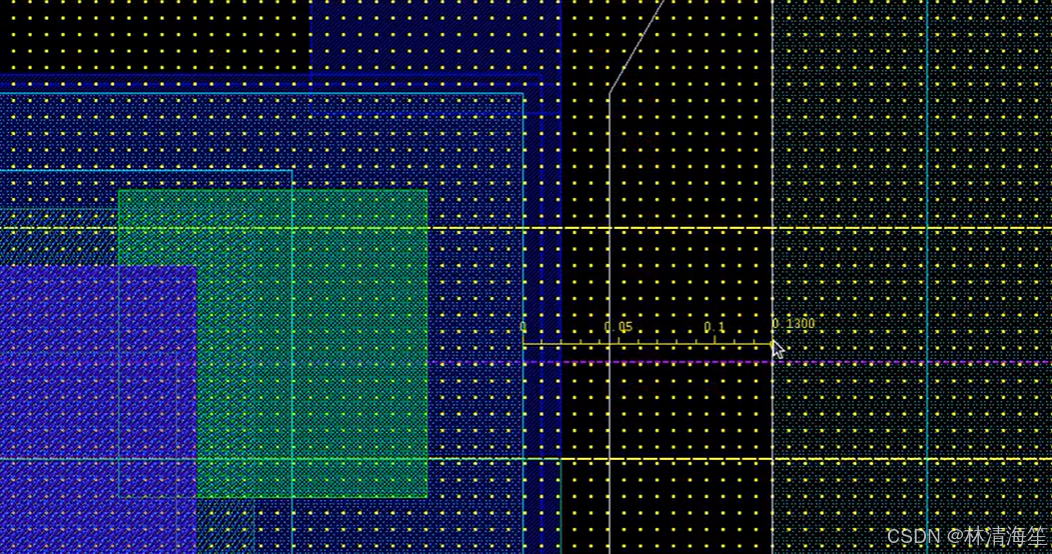

目前显示的都是框,如果想要查看元器件具体的电路版图,按住shift+F键,就可以显示出所有的层级,如果退出显示的话,按住Ctrl+F键,就只会显示元器件的框了

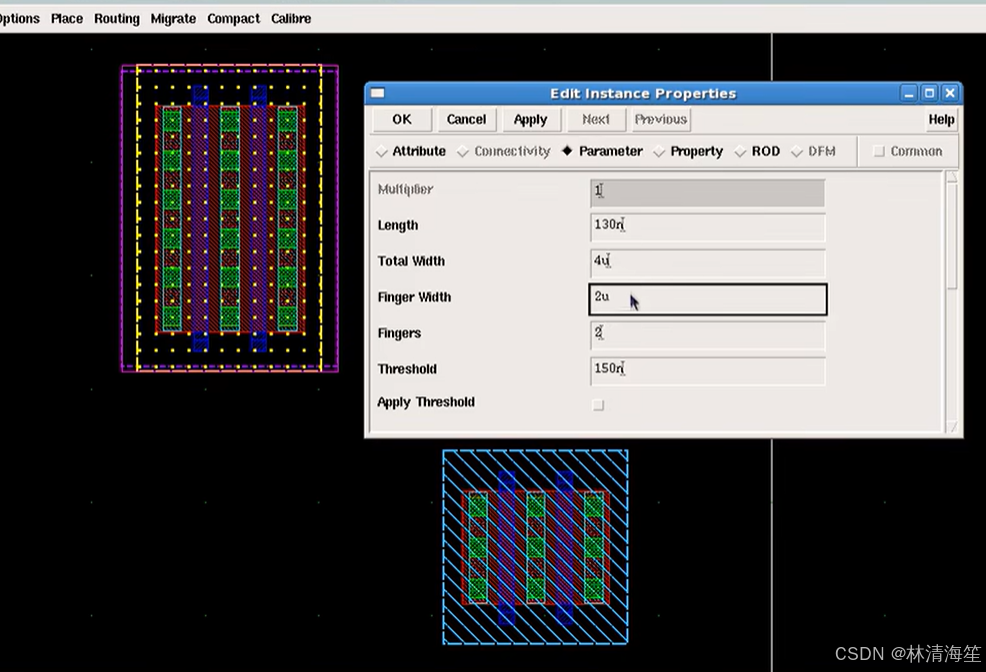

如果想要查看元器件的参数,选中元器件,按住Q键,其参数都是原理图所设计的参数

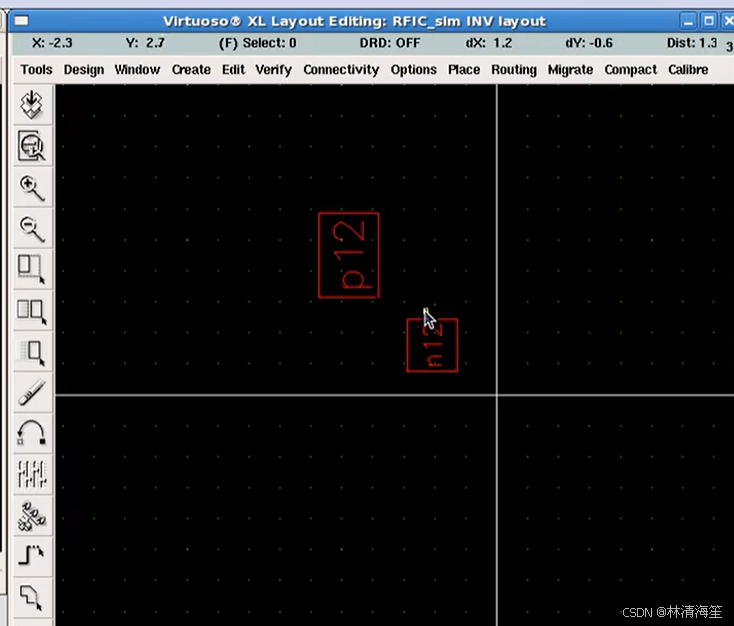

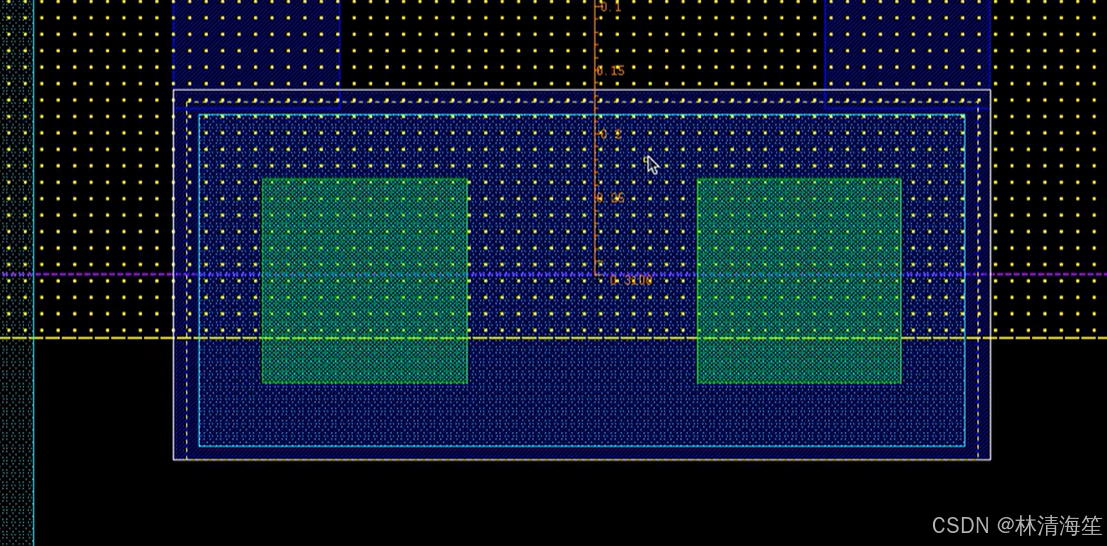

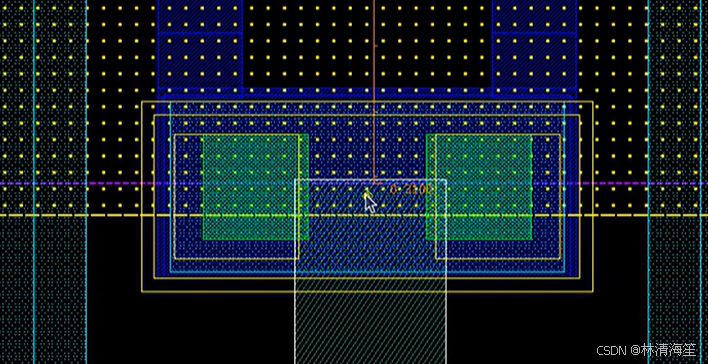

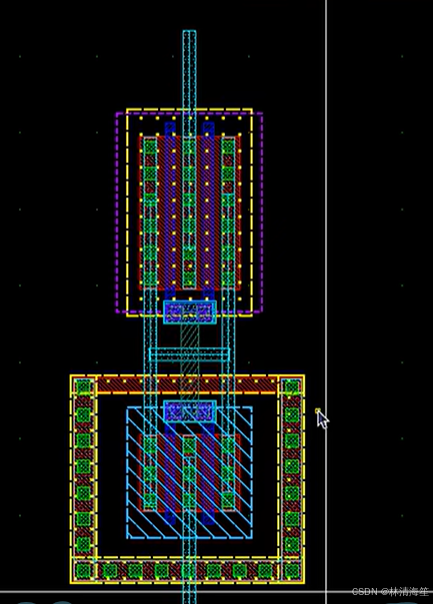

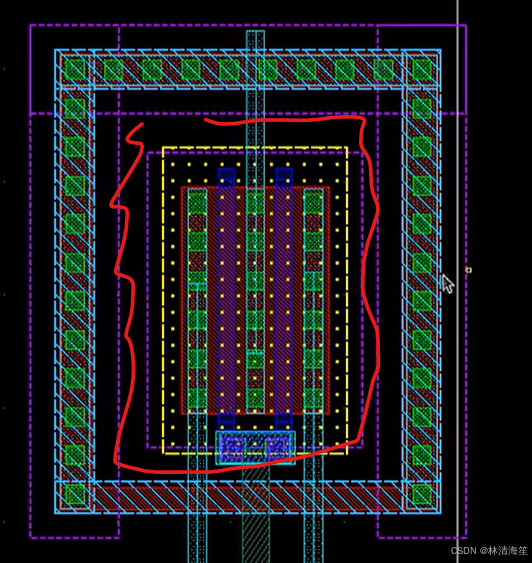

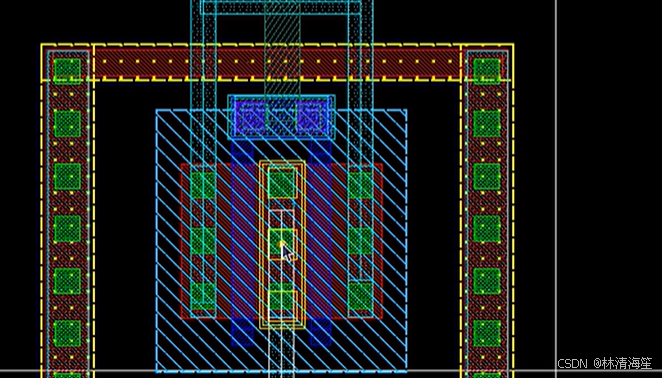

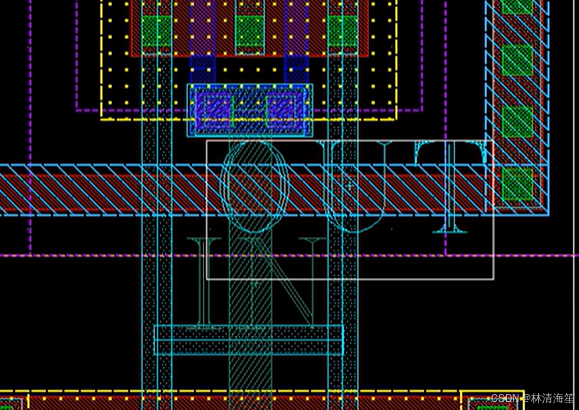

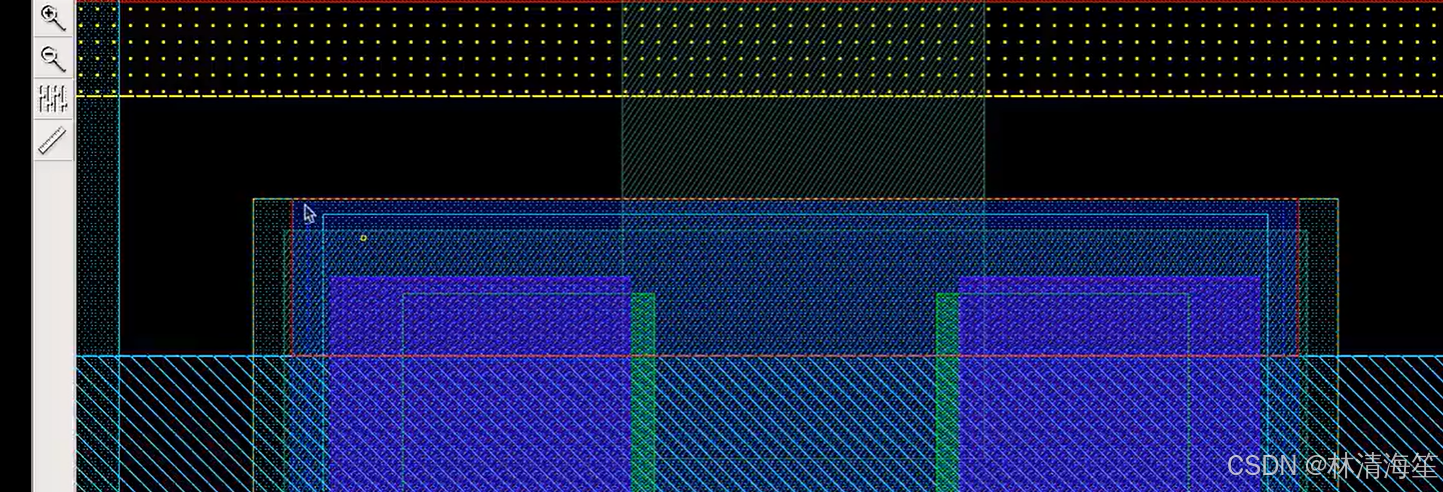

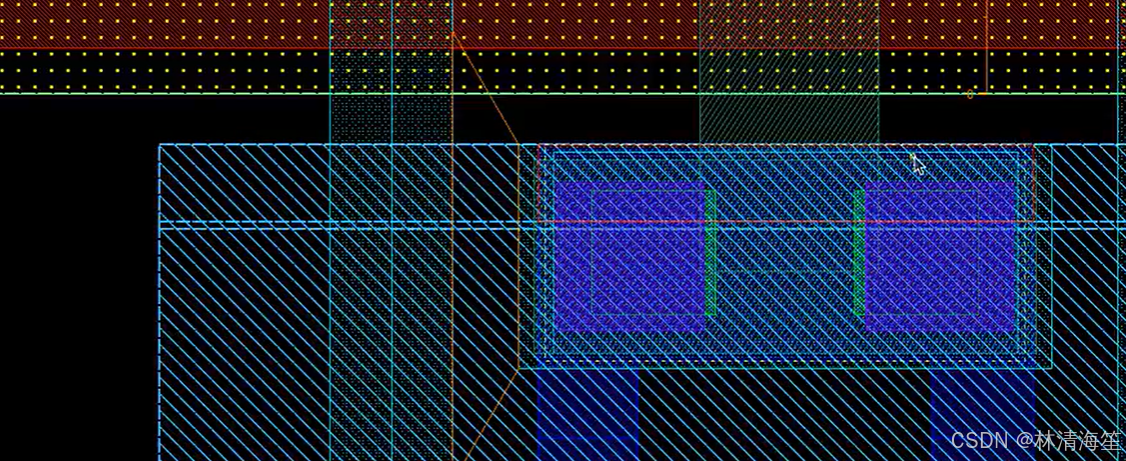

现在查看元器件的MOS层级

外圈蓝色斜线为N型注入层;中间深蓝色长条为GT层,即多晶硅制作的栅极;红色为AA层,即有源层;另外还有金属1层M1,有源层和M1是通过过孔CT层(绿色)进行连接的

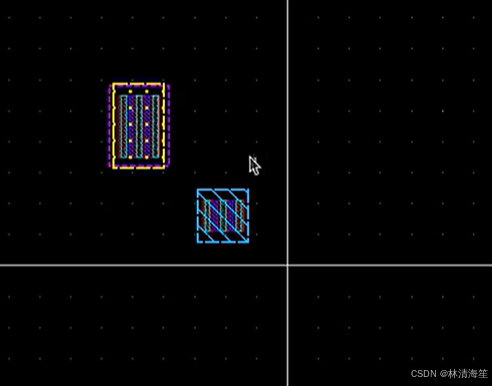

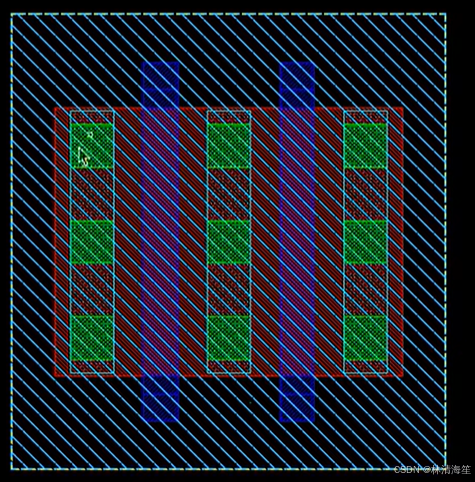

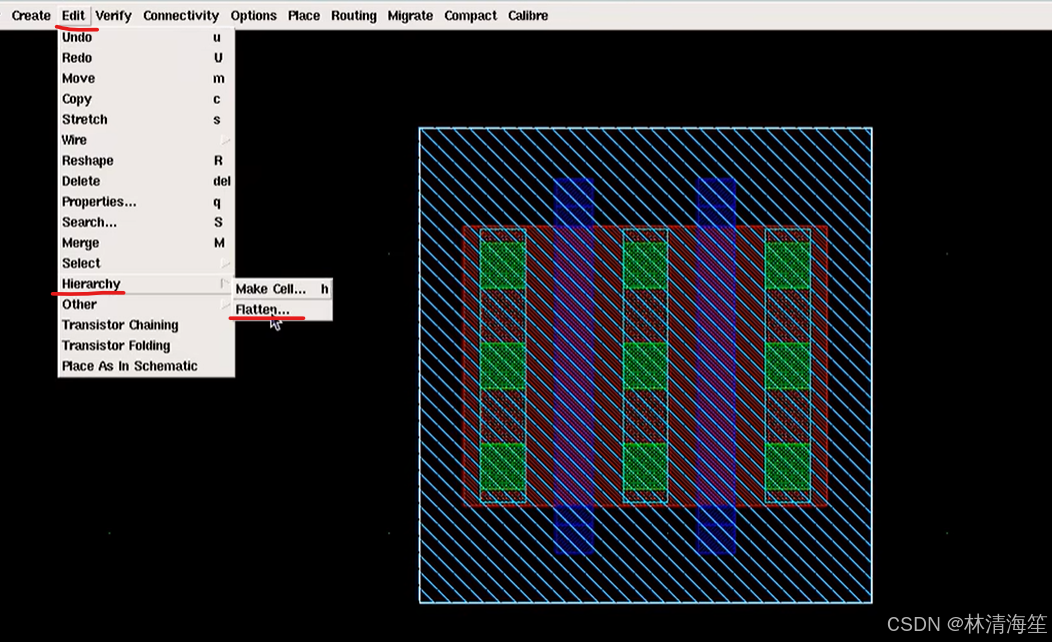

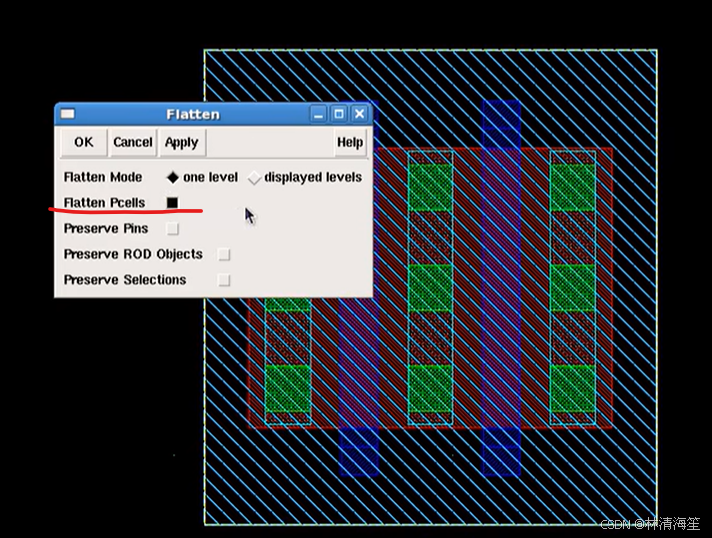

为了更好的查看晶体管的层级,需要先将其打散flatten。

首先选中器件,Edit——Hierarchy——flatten

然后会弹出对话框,因为这个是一个PCells,所以要选择Flatten Pcells

然后查看Pmos,最外面的紫色为NW层,即NWell;黄色的框为P型注入层SP;

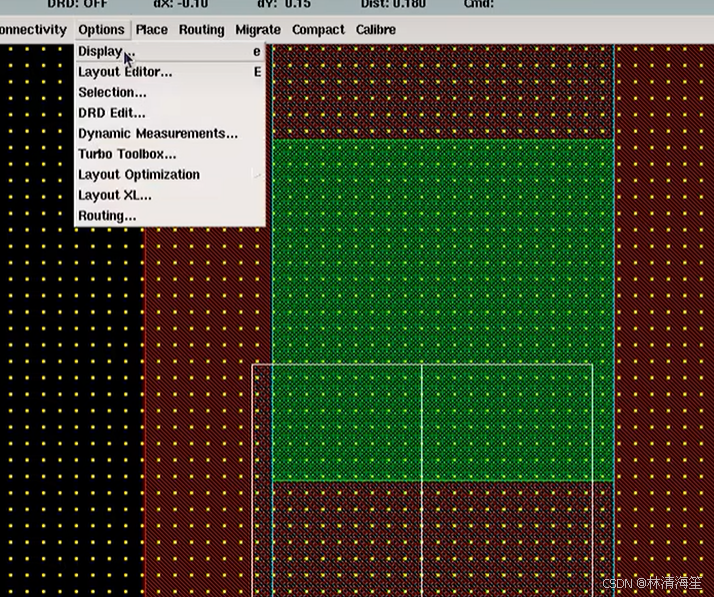

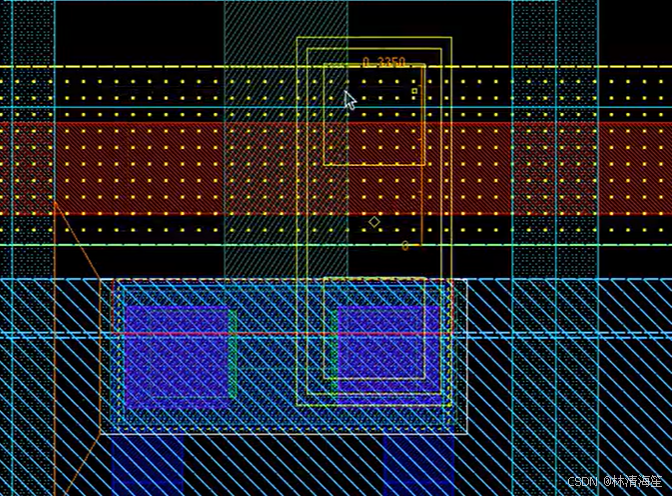

3.格点的分辨率

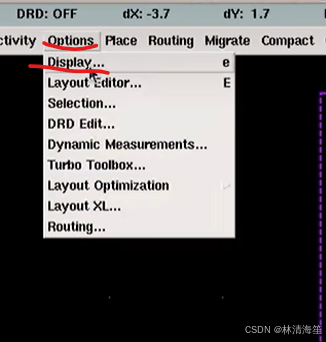

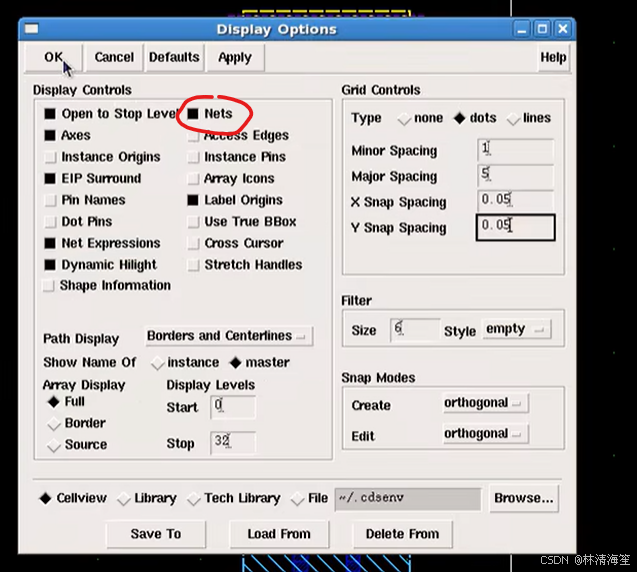

在options——display中

默认的为0.1,我们改小一点为0.05

如果要移动元器件,选中元器件中,按住M键即可

4. 版图的连线

如果要查看连线的关系,在Option——display中选择Nets

连线选择金属1层,连线的快捷键是按住键盘上的P键,显示出连线的起始端口,画完之后按住回车键即可。

将上下的漏端连接在一起。

如何对其修改连线的宽度呢

对不齐线的原因是分辨率太低了,重新调节设置。

将连线对其金属1层。

此外,还要将左右的漏端连接在一起

然后再将上下的源端连接在一起。

假如我们要修改连线的线宽,先按P键显示出连线,然后按住F3键,在这里我们能够设置金属线的宽度,这里默认是0.16um

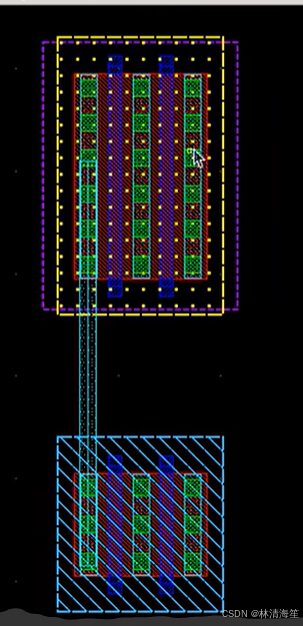

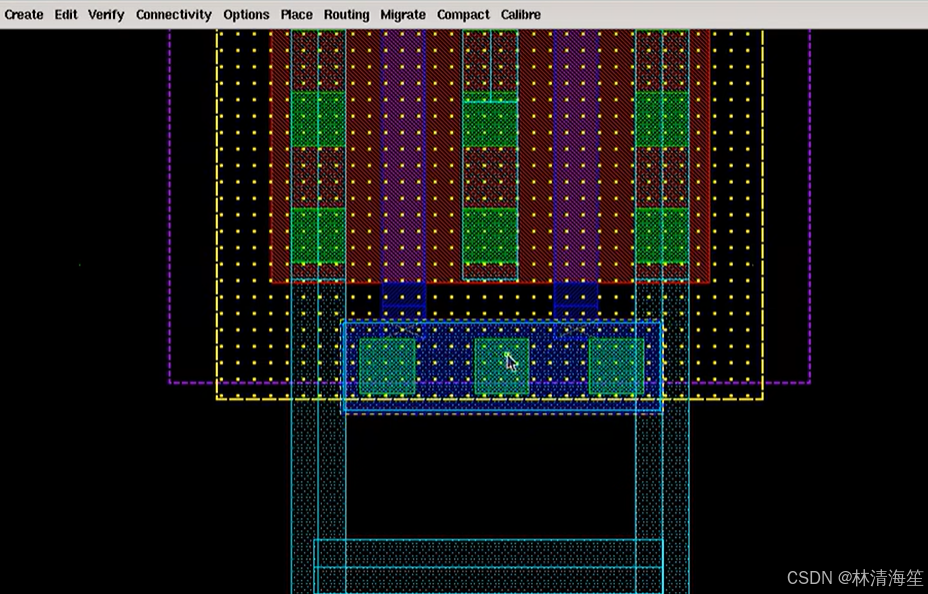

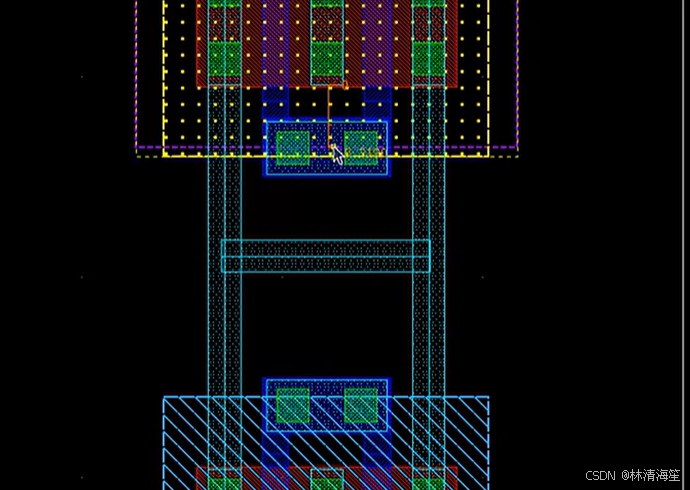

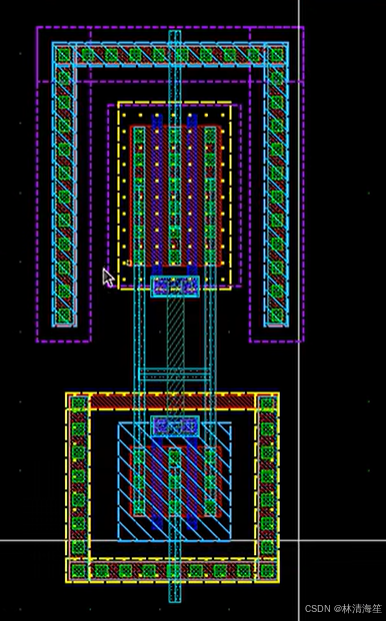

我们把PMOS的源端的连线往上引出,用于接入电源,把NMOS的源端连线往下引出,用于接入GND

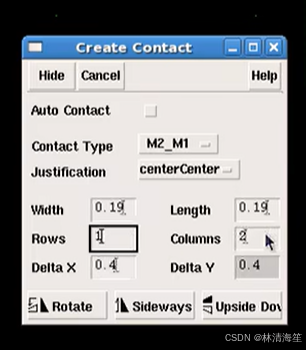

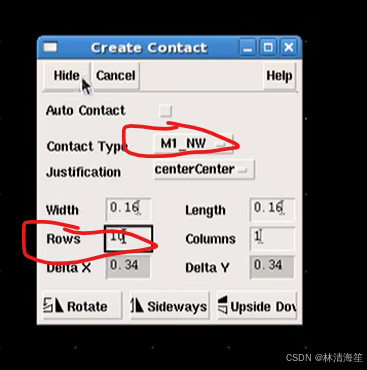

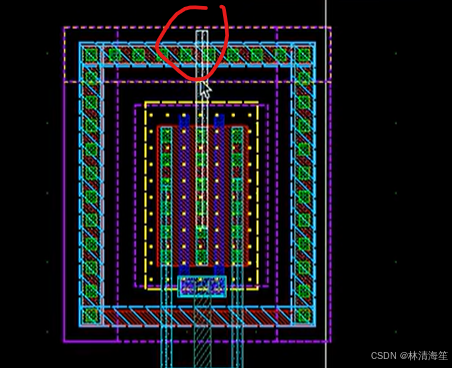

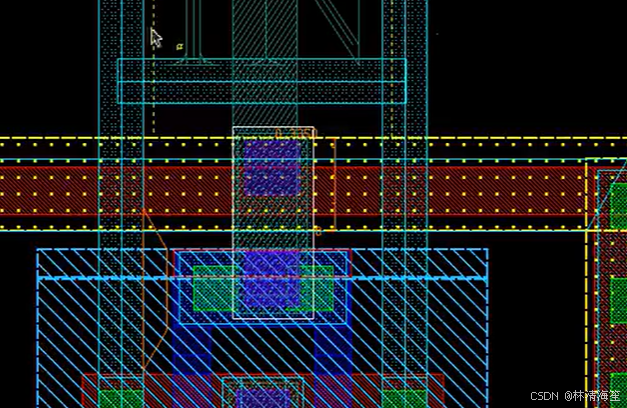

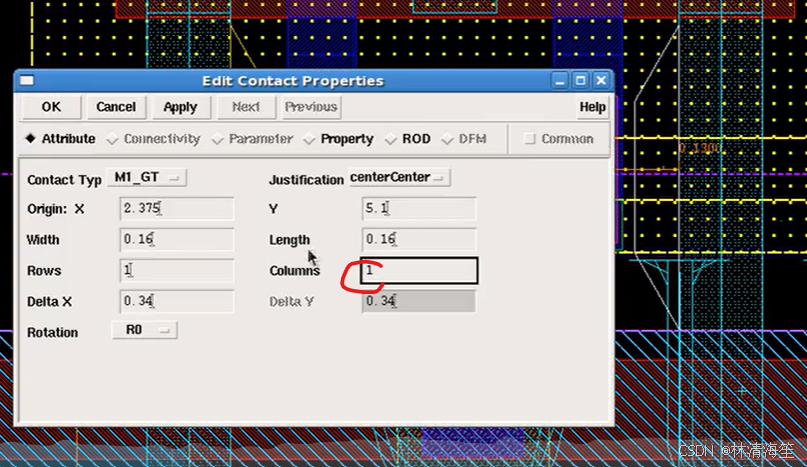

反向器的栅极是连接在一起的,这里就需要用到过孔

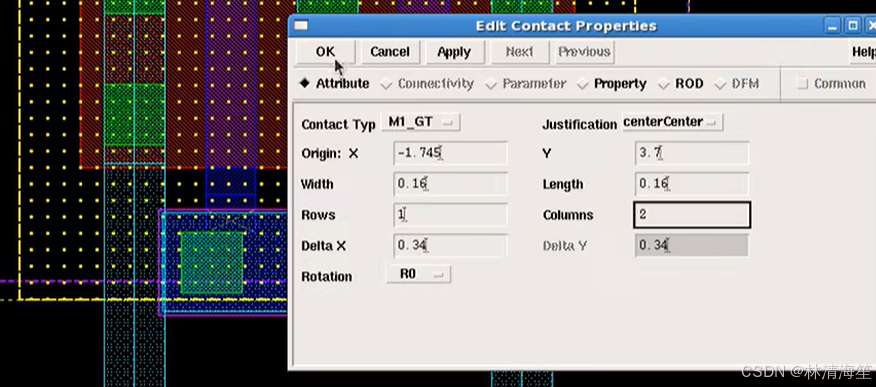

这里可以添加各种各样的过孔,这里把列数设置为3列,然后放着在版图上

但是这里由于过孔太长了,导师金属层连接短路,这里把列数修改为2个,

这样就可以把两边的栅极进行连接

shift+Z逐步缩小版图的快捷键

然后绘制GT层将过孔进行包围连接

同理,将NMOS的栅极进行连接

按住C键,即可将过孔拷贝下来,

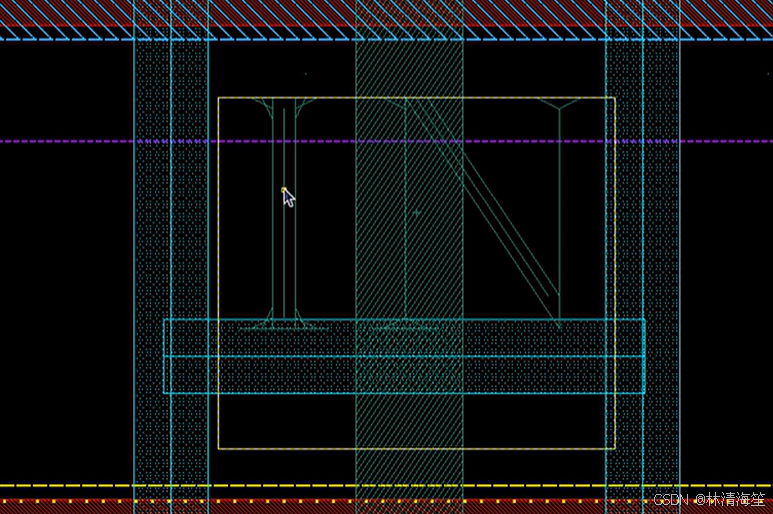

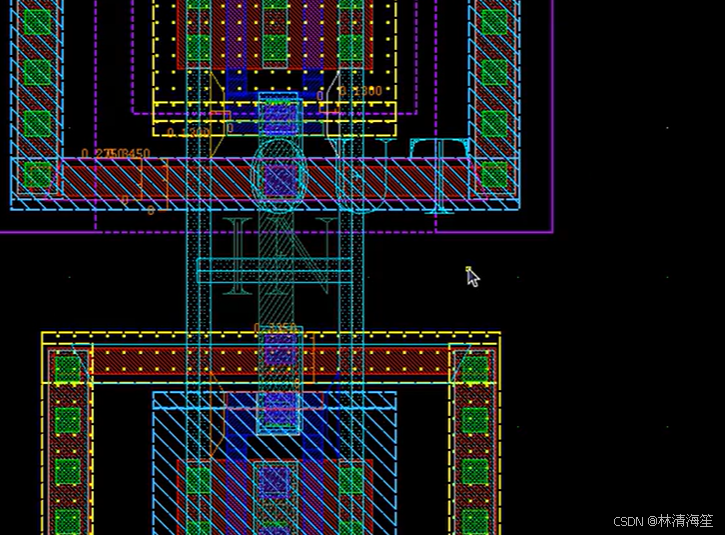

现在需要将NMOS和PMOS的栅极进行连接。

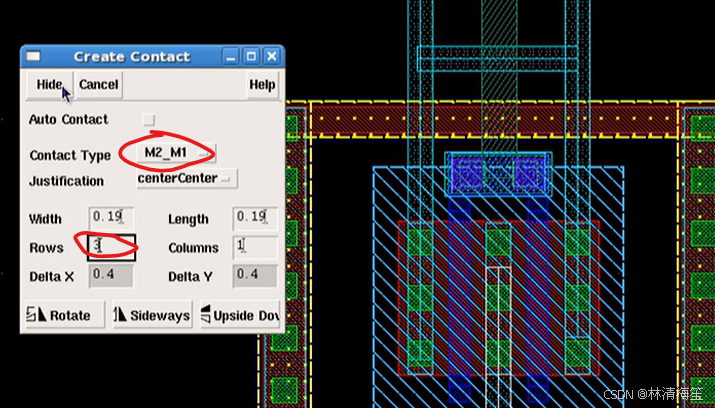

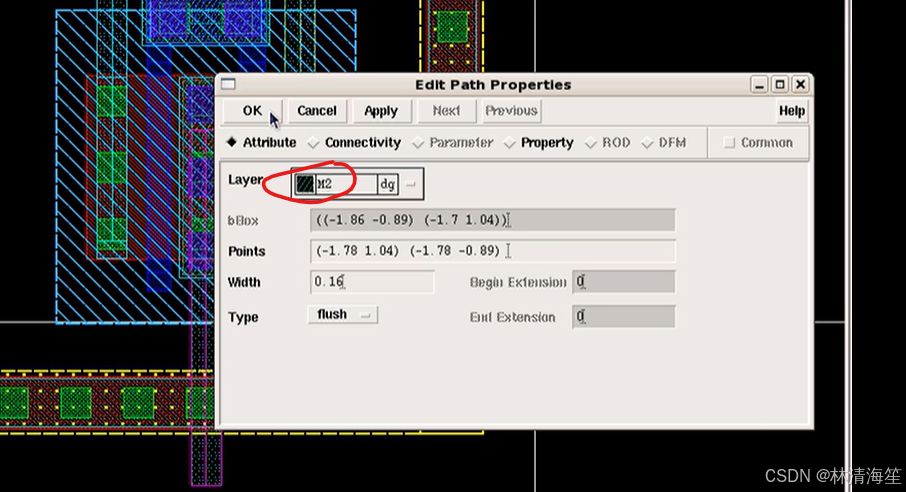

如果使用金属1层连接的话会导致与源极连线的短路,因此这里我们采用金属2层进行连接。

首先选中M2层

但是现在还需要将金属2层与栅极进行连接,因此还需要过孔

然后把过孔放置在栅极处,就完成了金属2层到金属1层的连接。

同样把过孔拷贝到NMOS管的栅极中,就完成两个管子的栅极连线了。

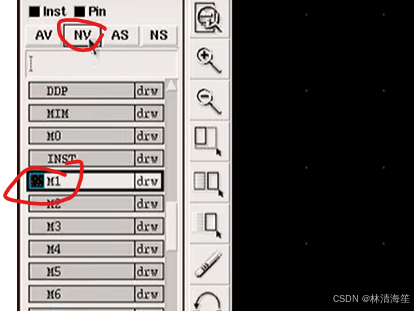

5. 查看某一层的连线

在LSW中选中M1层,点击NV,即隐藏其他的层级显示

然后再选中版图窗口,按住F键就可以查看了

再去点击AV,全部层都能显示出来了。

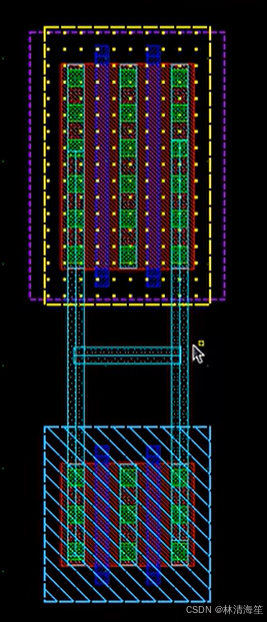

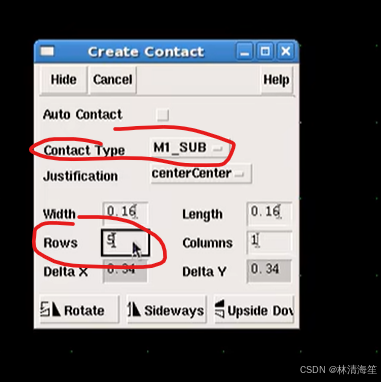

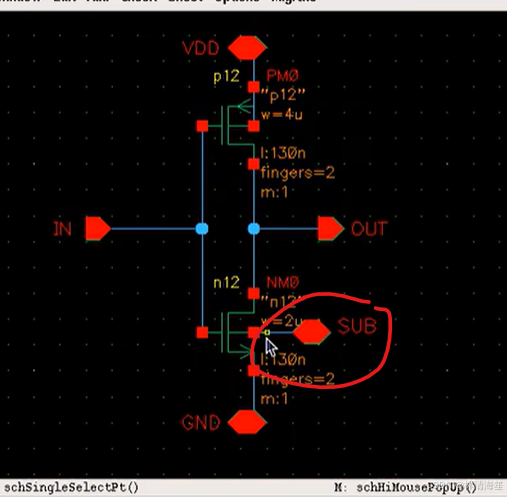

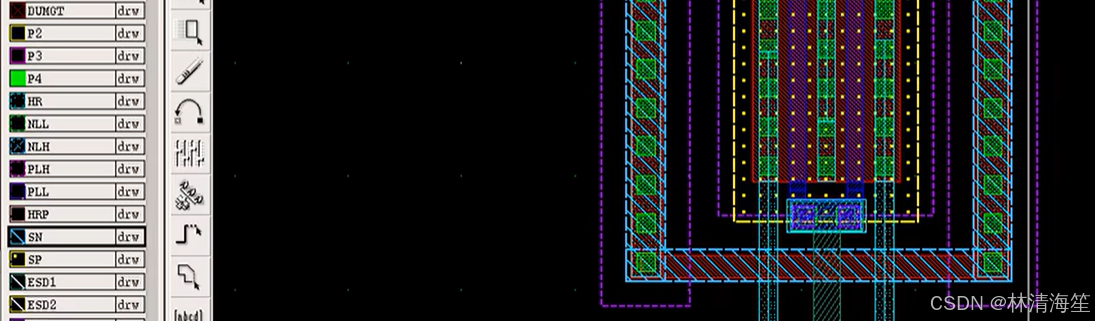

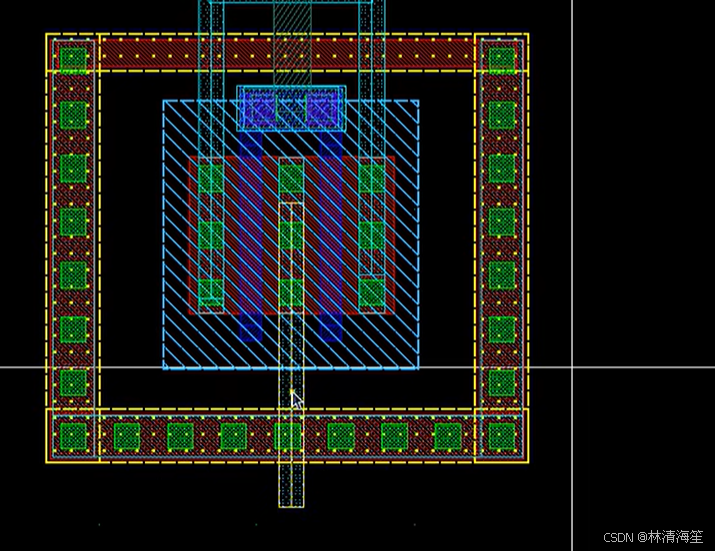

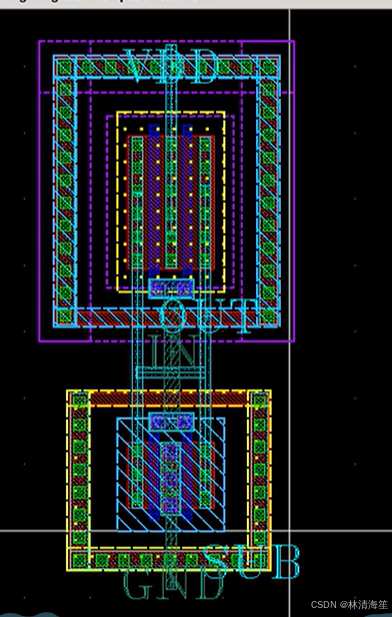

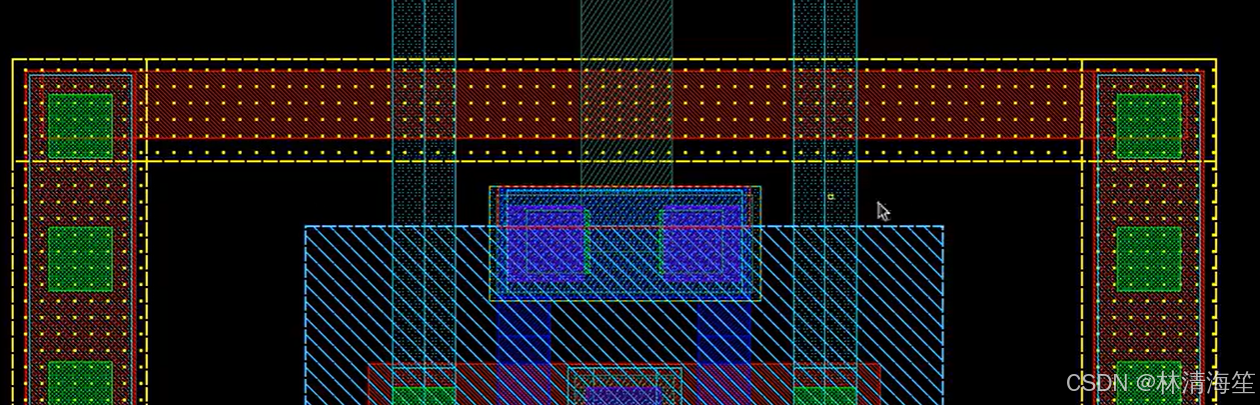

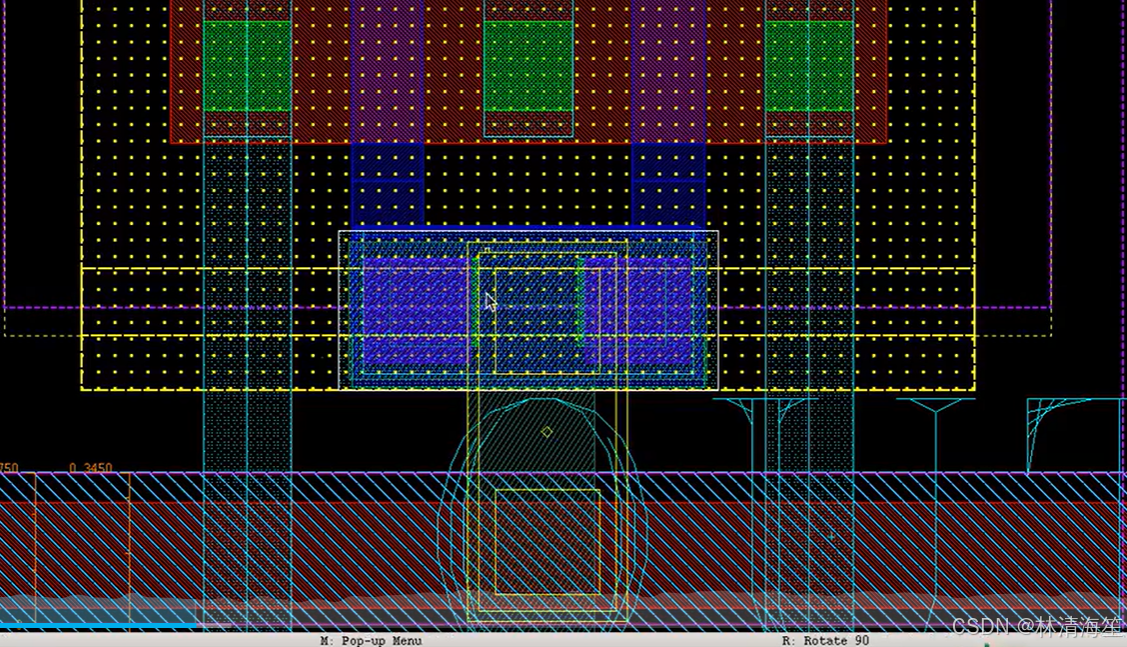

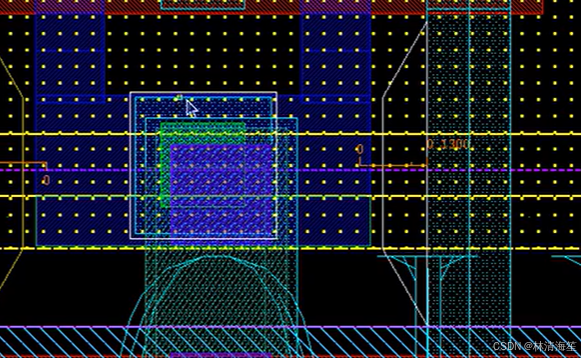

6.添加N井SUB

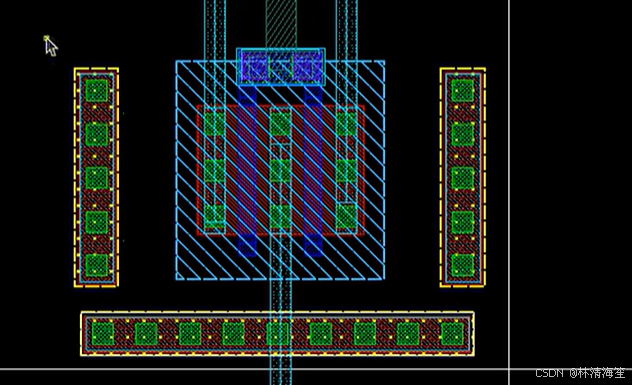

现在还有连电源端和GND端未连线,此外还有衬底接触环,即N井保护环的画法,主要是为了消除lachu效应,同时让晶体管的工作环境更加干净。

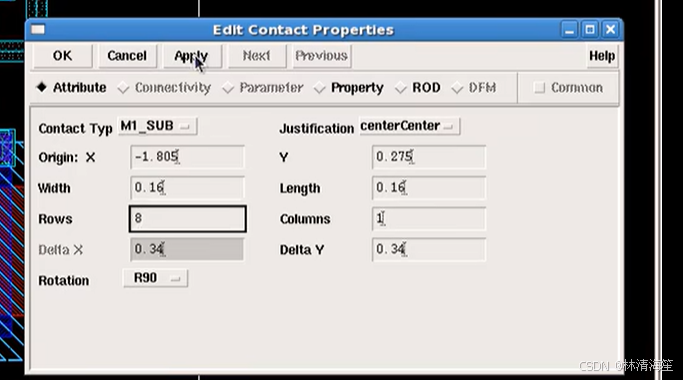

这里也是选择过孔,M1_SUB层,5行1列

这部分就是衬底接触孔了,对应的是原理图SUB的端口

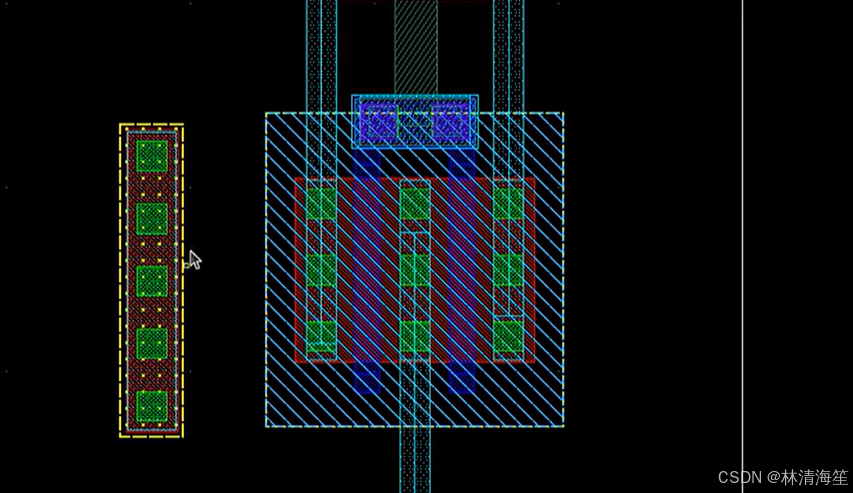

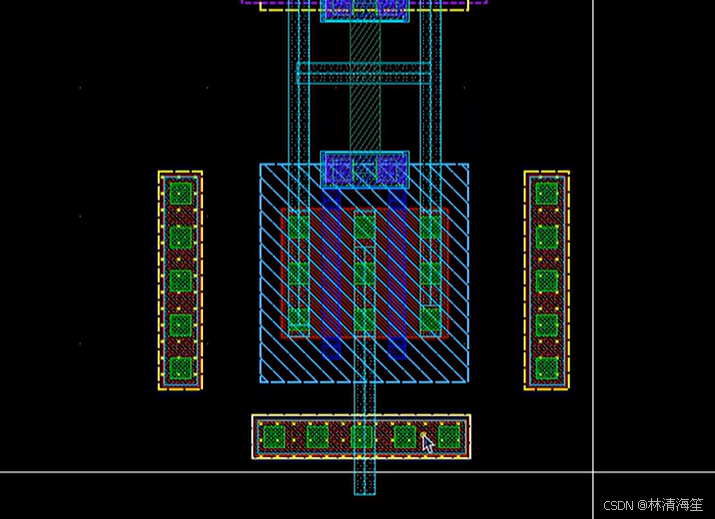

这里我们将SUB围成一个环

我们把加大下面SUB的过孔数量,增大为8

这时候,我们需要把这些过孔全部都连接起来。将过孔对齐就可以全部连接在一起了

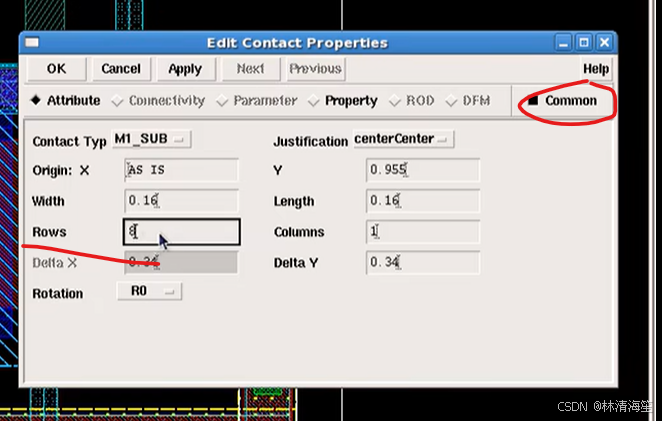

如果我们需要同时修改两个过孔的参数,可以先选中其中一个过孔,按住Shift,在选中另外一个元器件,按住q键。

如果我们需要同时修改,需要选择Common的选项,

这样就可以同时修改了,如果要同时移动,也是同样操作,按住键盘上的M

这时候我们还需要将环进行有源层的连接,这里选中AA层,画出矩形的框,将两部分连接起来。

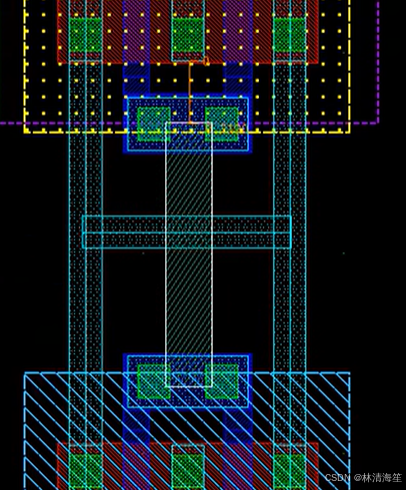

但是现在是有DRC错误的,因为没有N型或P型的注入,

这里我们还需要画SP层将他们包围起来,这个矩形框是要超过有源层的尺寸,才能够满足设计要求的。这样SUB的框就完成了

同样PMOS管也需要N井的保护环,

鼠标右键是对元器件旋转的操作,

现在这两个SUB太近了,现在需要拉动改变他们。

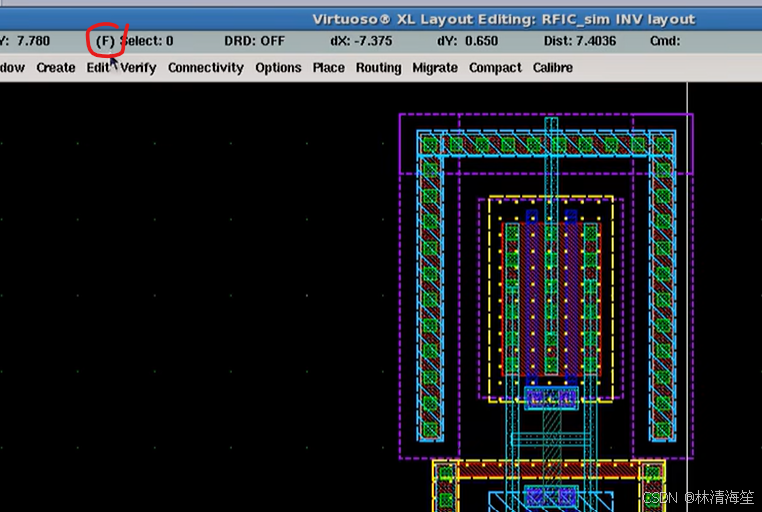

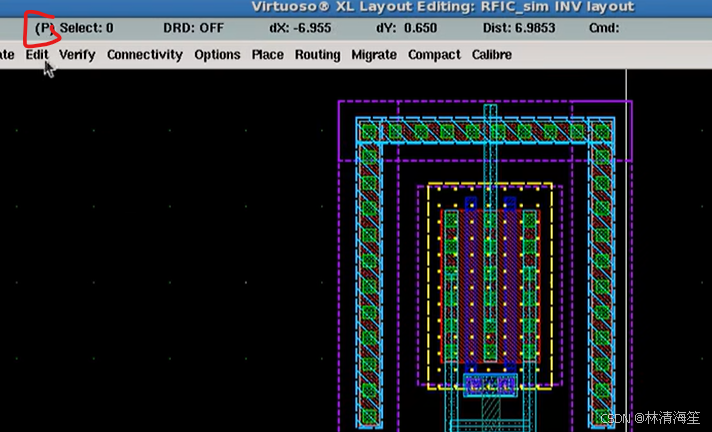

上脚的F表示全部选择器件,按下F4键,会变成P,表示部分选中

这时候我们进行鼠标的框取,

我们按住键盘上的S键,选中原理图上的元器件,

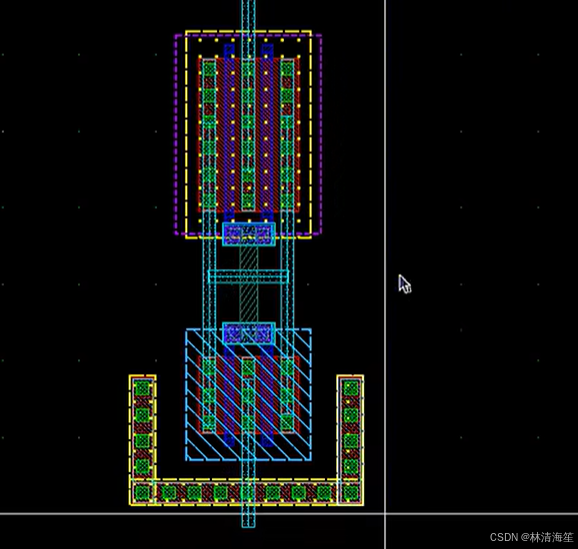

有源层的连接同样采样AA层进行连接

然后用SN层把AA层包围起来

但是现在还有部分区域没有被包围起来,我们要把sub和PMOS管全部放在N井里面,把这个区域画一个矩形框全部包围起来。

使用NW层将全部SUB和PMOS框柱

这时候我们发现金属1层出现短路的情况

在NMOS中,SUB和GND有短路的情况,我们添加一个过孔,把输出的源端换成金属2层进行连接。

然后我们再把金属1层替换为金属2层M2。

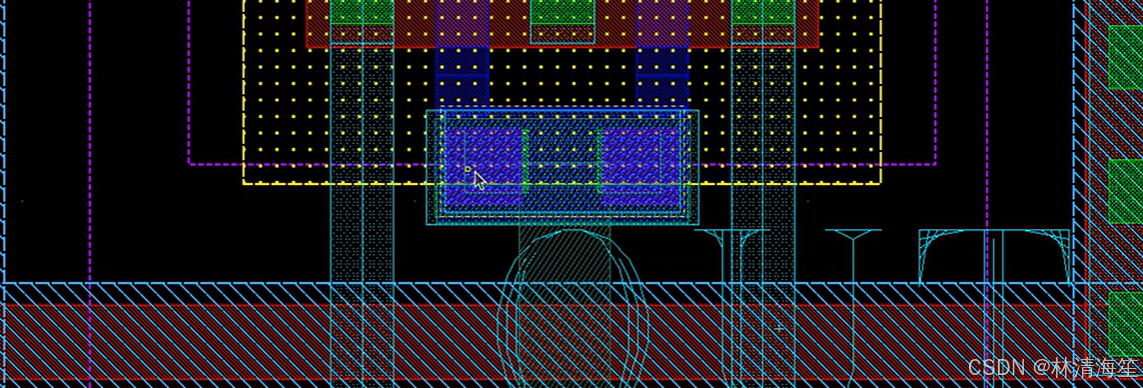

7.添加输入输出端口pin

此外我们还需要添加输入端口,电源、GND、SUB等,

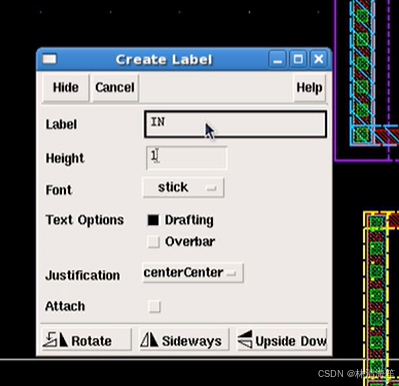

我们通常是添加label,命名层级名字

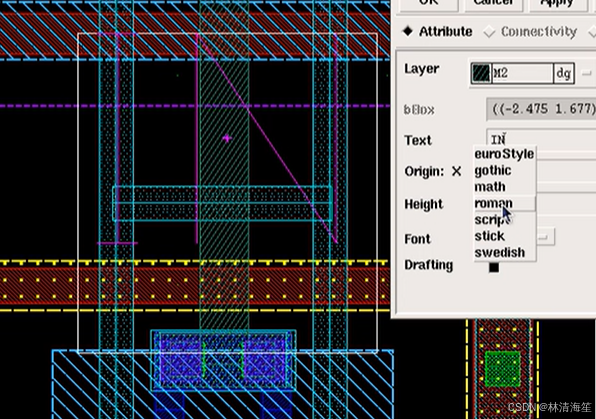

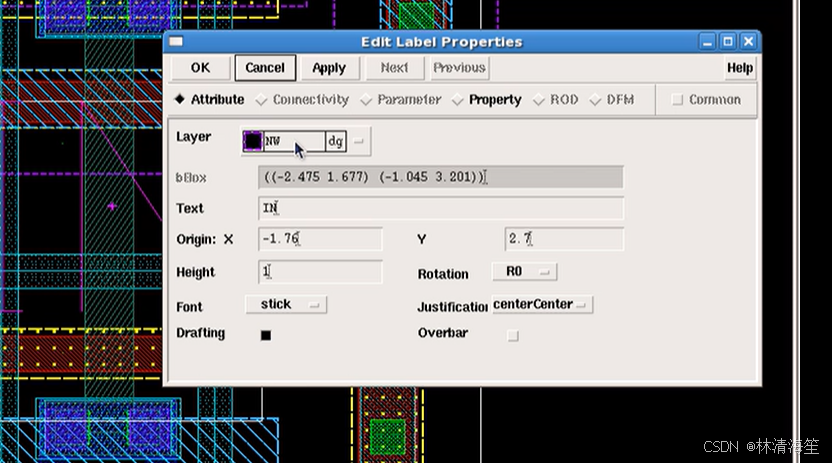

点击Create——label

输入端口名字IN,放置在输入的线上。

然后修改属性,这里默认设置是在NW层上面,我们需要将其更换为M2层

还有就是字体的尺寸和高度都可以进行更改替换。

这里的字体(font)太细了看不清,我们更改为罗马字体roman

输入的pin就添加在了金属2层上面了

在输出端口,是金属1层连接,

然后设置VDD、GND、SUB端口

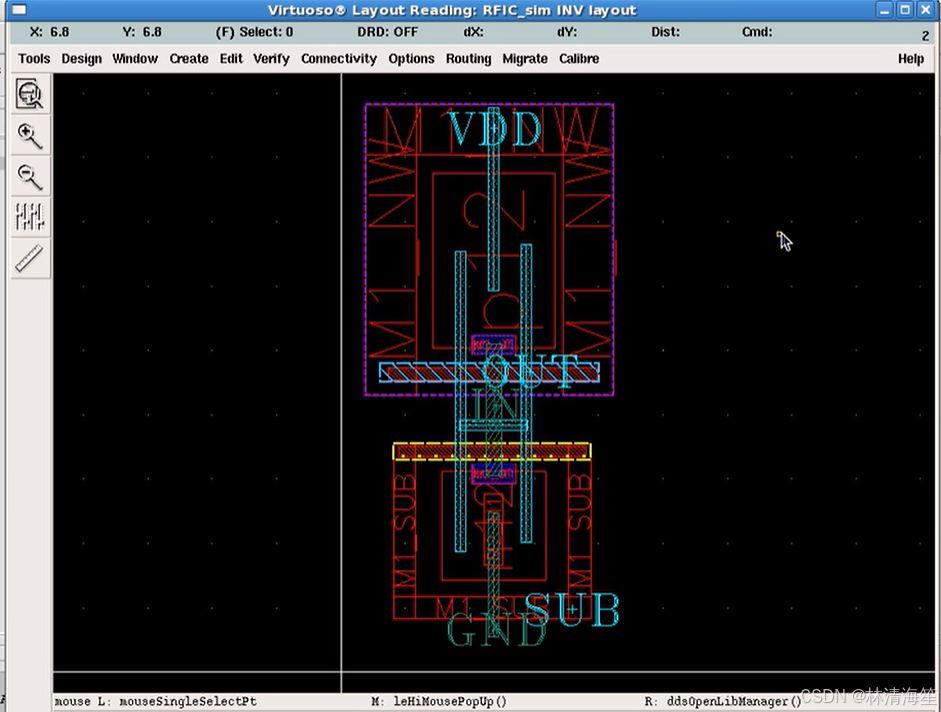

二、版图的验证

用virtuoso版图设计软件设计了反相器,然后用calibre软件对版图进行验证

有设计规则验证DRC,有原理图和版图的比对验证LVS,所有验证完成后,需要对版图的寄生参数进行提取,我们要重新搭建test bench测试电路对寄生参数进行后仿真,来验证寄生参数是否满足设计的要求

我们首先打开前面画好的版图layout

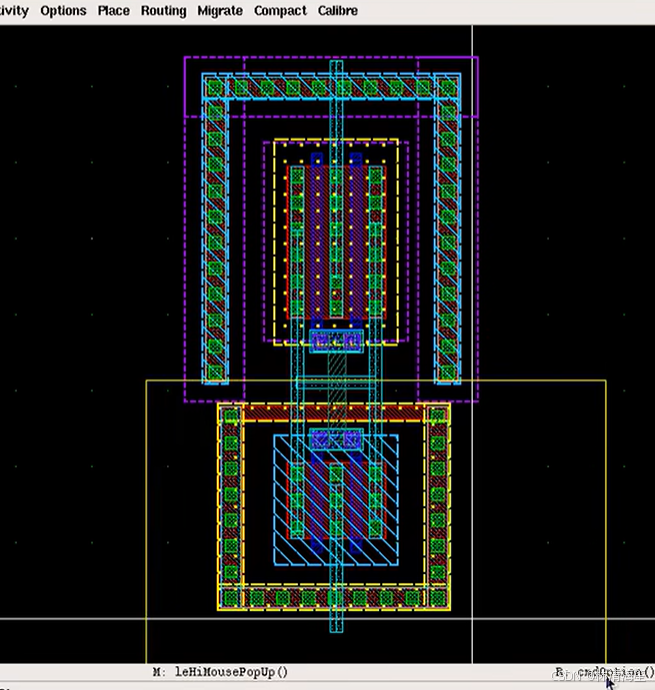

然后我们按住shift+F,把整个版图都显示出来。

然后使用calibre软件进行DRC检查

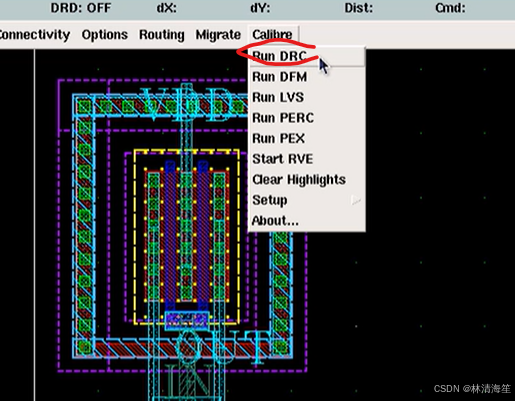

1. DRC检查

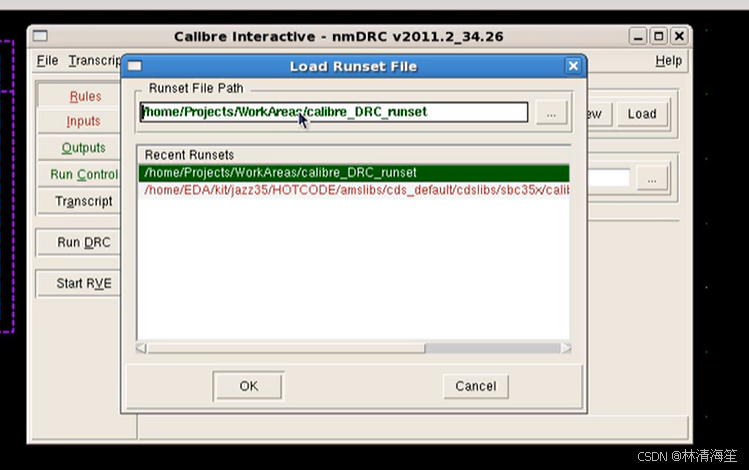

选择Calibre——Run DRC

这里runset是之前已经设定好的,在工作目录下面

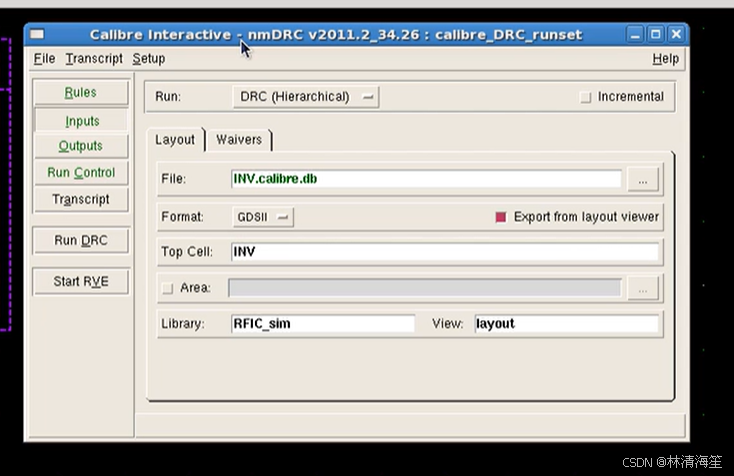

然后所有之前配置的信息都会调入进来

然后点击run drc,接着就会打开查看的窗口

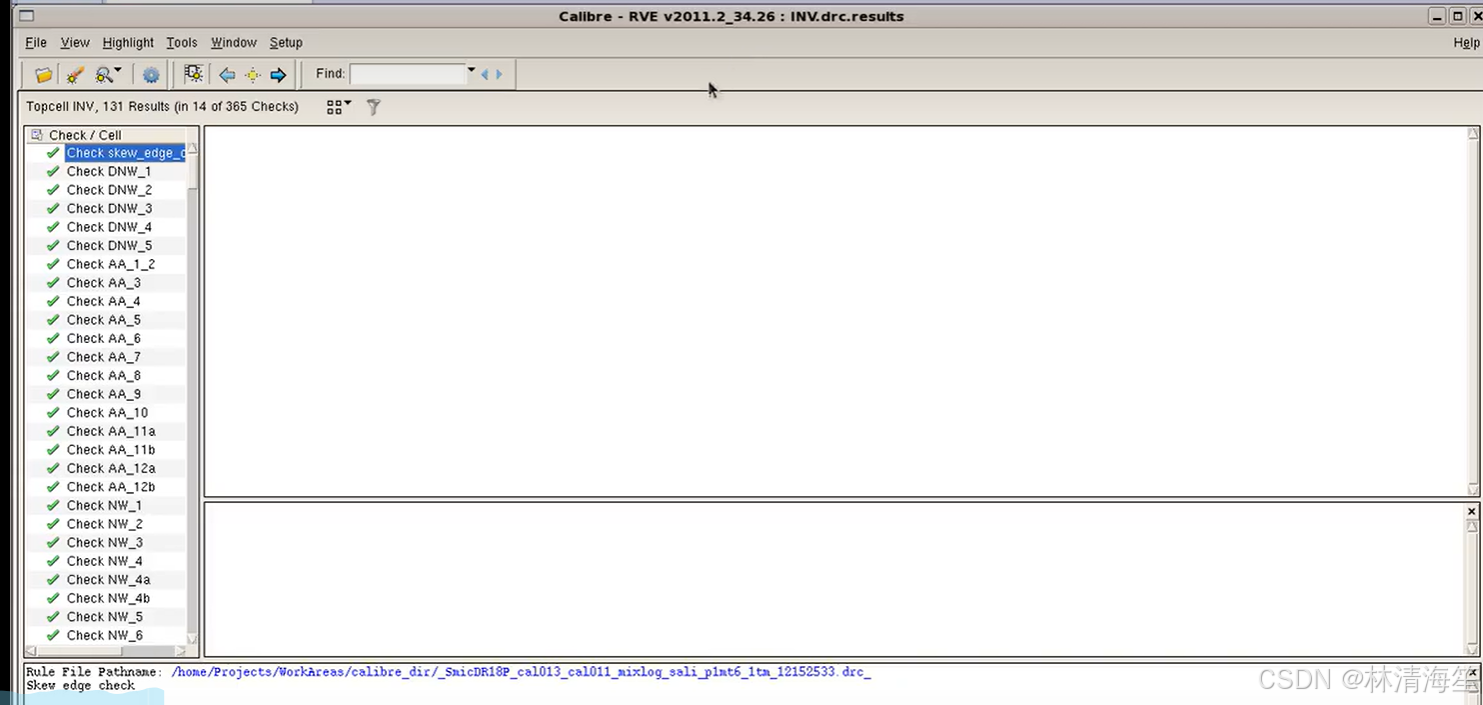

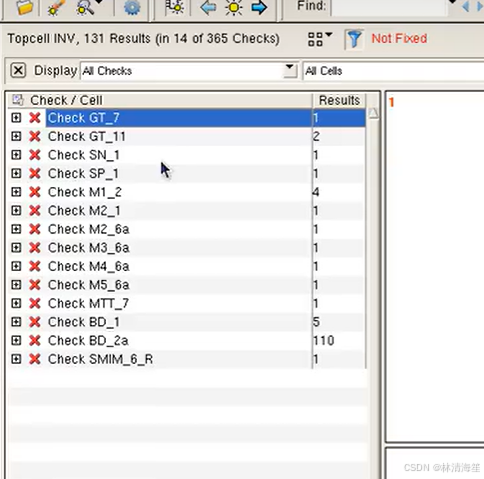

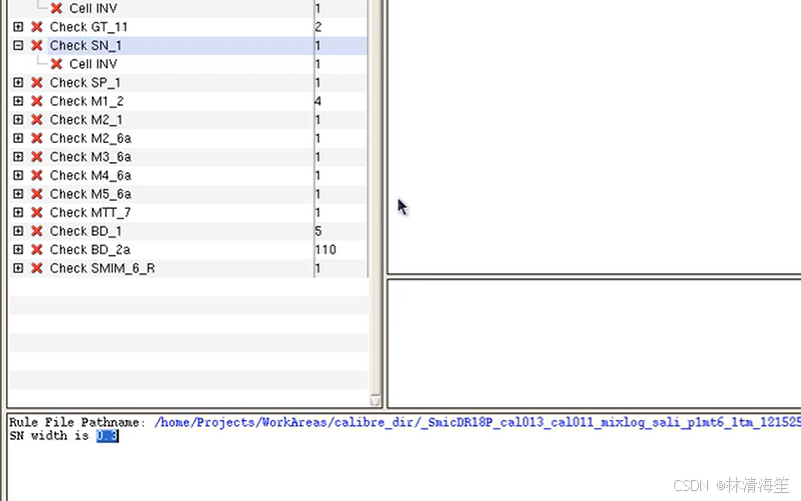

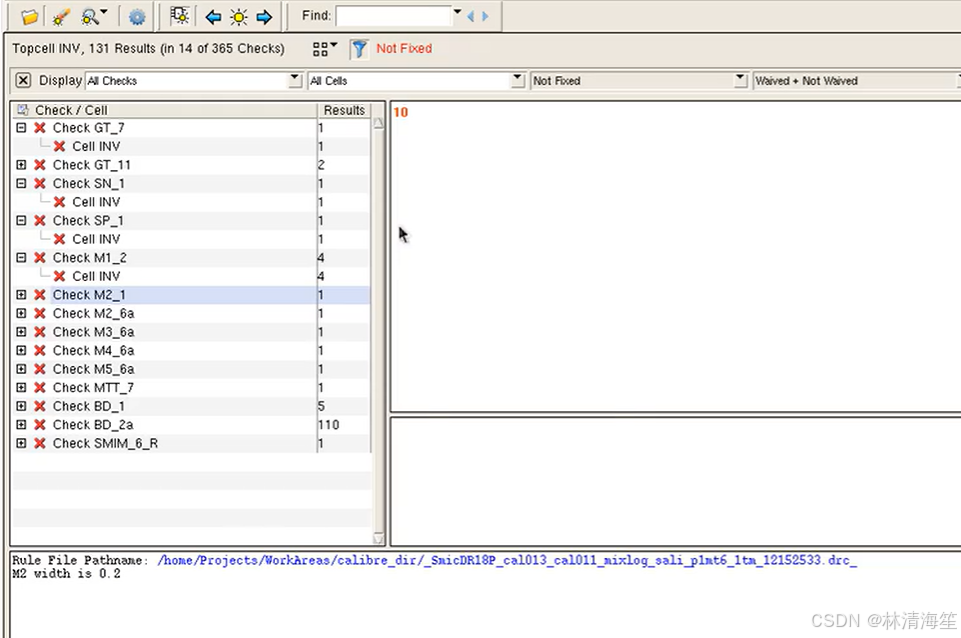

左边1列式全部检查的项

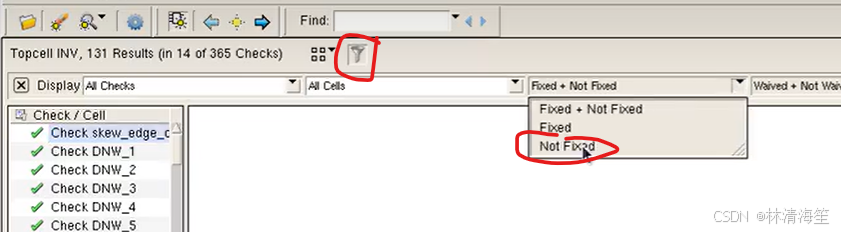

我们需要去寻找没有通过的一些规则,点击筛选(漏斗形状),把通过的检查全部都绿出掉。

选择not fixed,然后点击Apply

然后就会显示出没有检通过的项

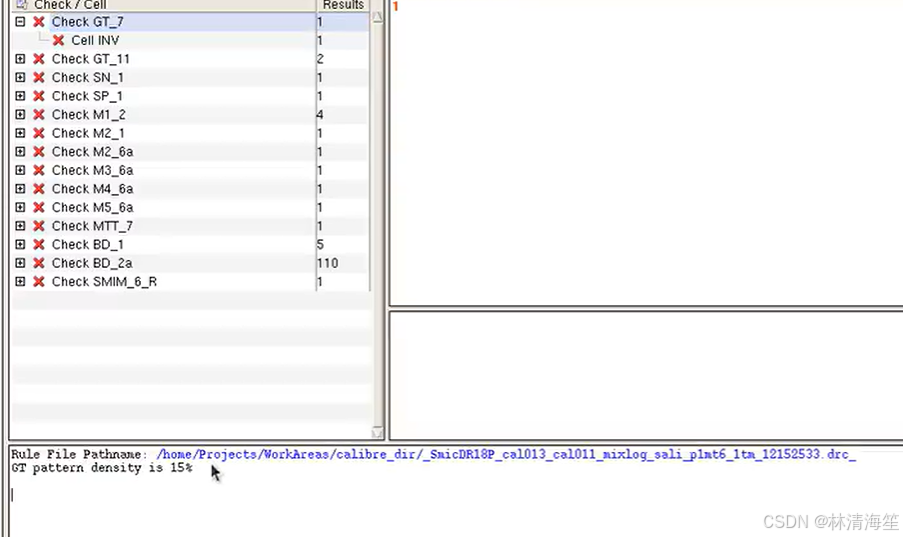

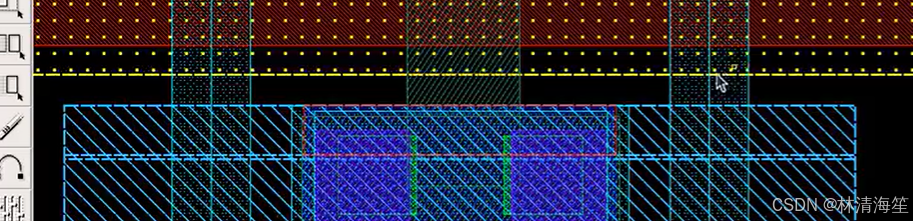

第一个是叫做GT_7的检查错误,查看下面显示栏中对违背的DRC错误规则的说明

这个错误表示GT层多金属的密度小于15%;对于小模块的设计的金属密度的要求,通常不会去修复他。只是在最后做大的芯片在做顶层的版图验证时,需要去填充一些纳米金属,把金属密度提高,来满足工艺生产厂对金属密度生产的要求。

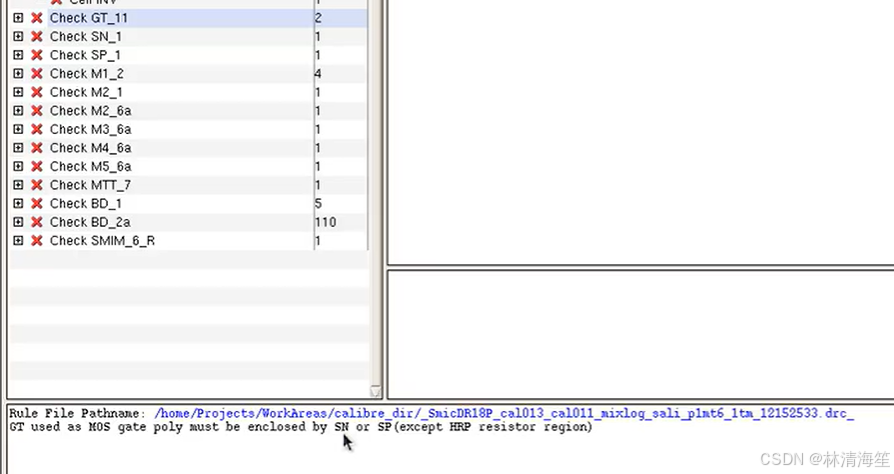

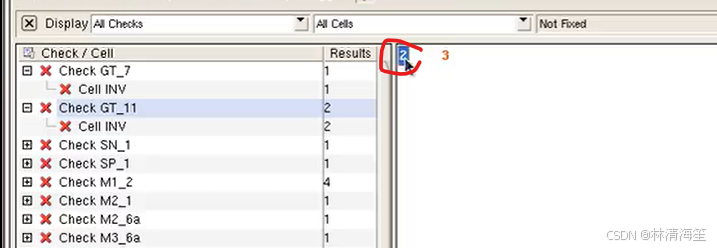

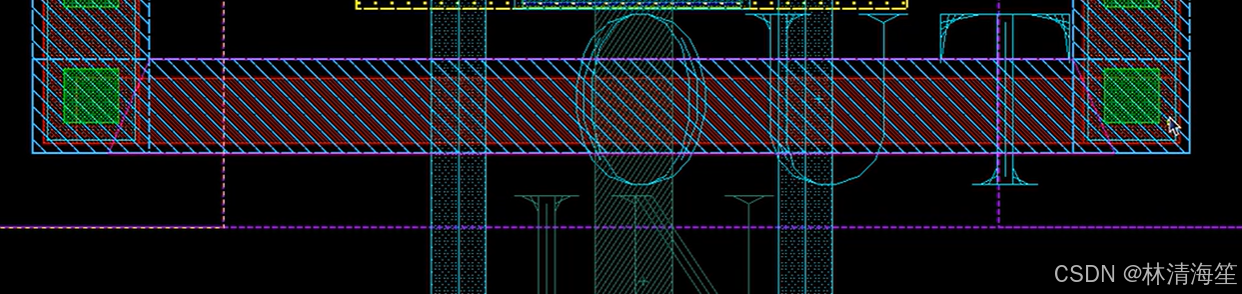

第二个错误是GT_11,表示GT层作为mos晶体管的gate层必须被SN(N型注入)或SP(P型注入)所包围。

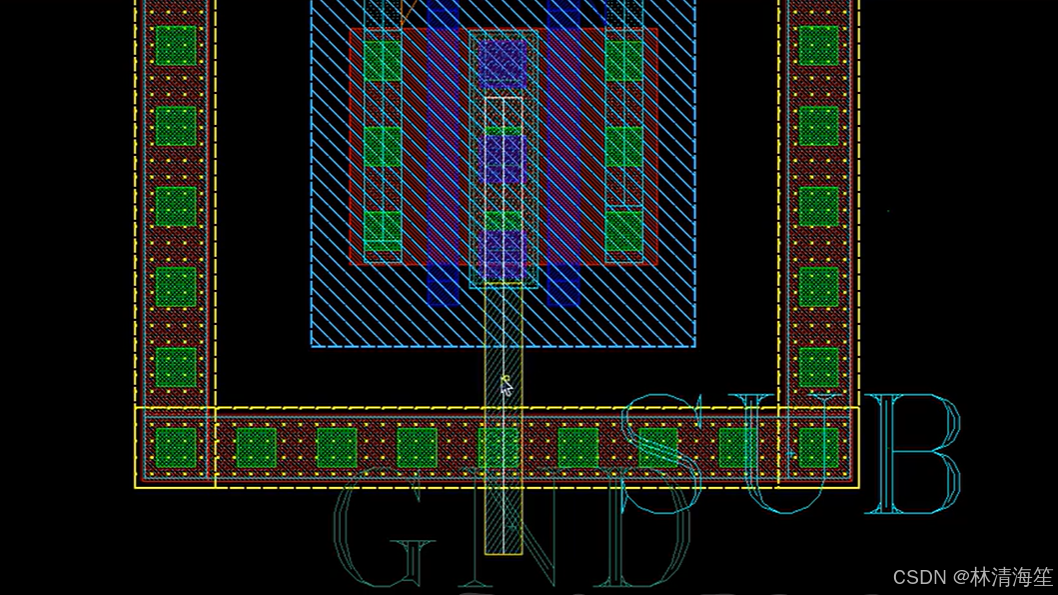

如果需要将错误在版图中显示出位置的话,鼠标左键双机红色数字,这时候我们再打开版图的layout,就会显示出来,有红色框会提示违背规则地方的区域。即说明这个区域没有被SP或SN层所包围。

这块区域没有被下面的N型注入(SP)蓝色斜线区域所包围。

那我们重新画一个矩形窗,把他们全部放在SN窗里面。

第二个错误同样也是画矩形框包起来

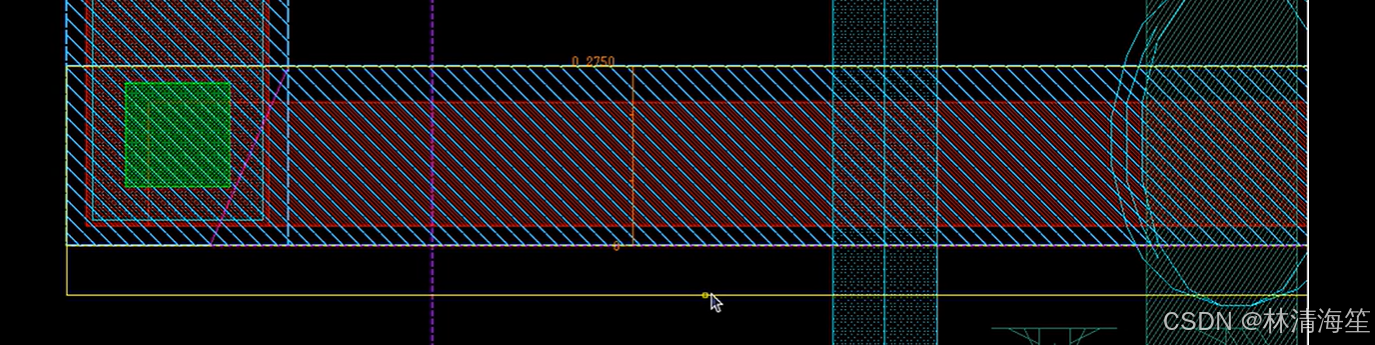

第三个错误是SN_1,即SN层最小宽度为0.3um

跳转到版图,发现是之后加的N型注入,画的宽度不够

量一下发现宽度只有0.275um,

先按键盘F4键切换选中方式,然后将区域拉伸

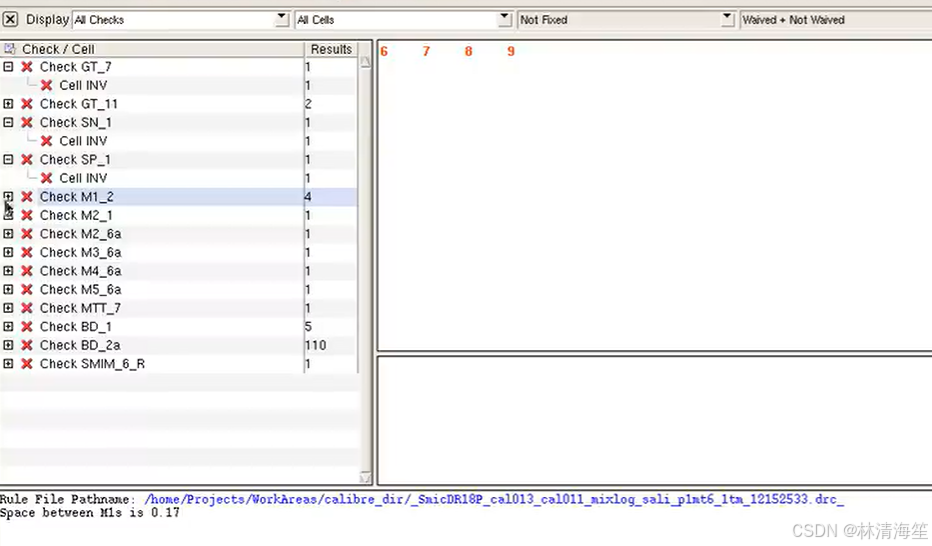

第四个错误是M1_2,表示M1的最小间距为0.17um

可以看到这里是小于0.17um的

因此我们需要旋转M1-M2的过孔。

按住键盘上的M,鼠标右键进行旋转

然后移动对齐

同样上面的M1_M2的过孔进行同样的操作

但是我们测量发现,过孔还是不满足设计要求0.17um

所以我们减小栅极的过孔数,

NMOS的栅极过孔进行同样的处理,减小过孔数

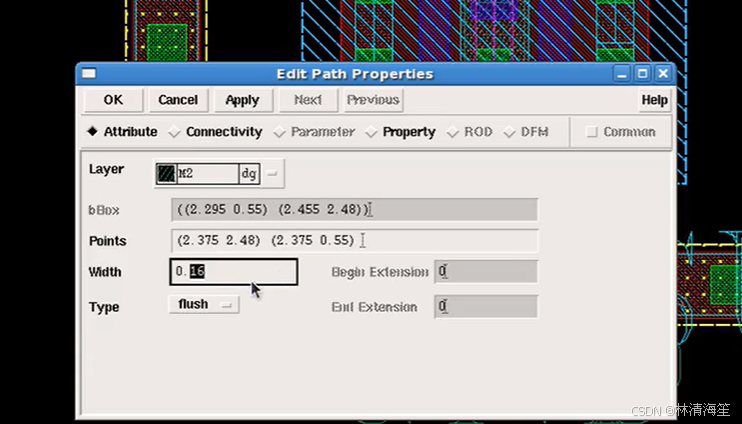

第五个错误是M2_1,最小线宽为0.2um

我们选中连线,修改属性线宽为0.2um

剩余的错误都是密度问题,可以不用管

再重新跑一遍DRC,看是否还有错误

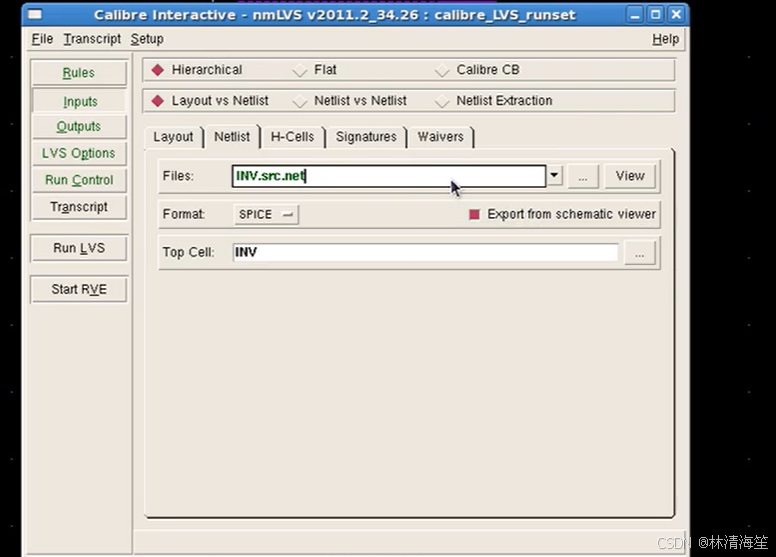

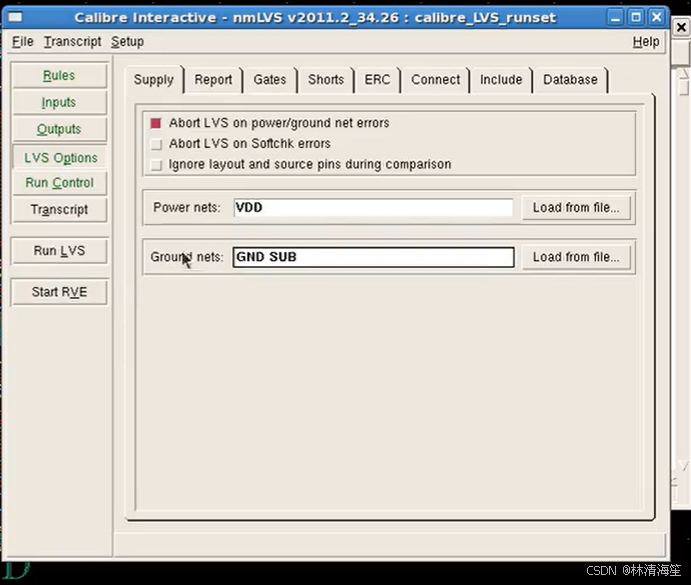

2. LVS检查

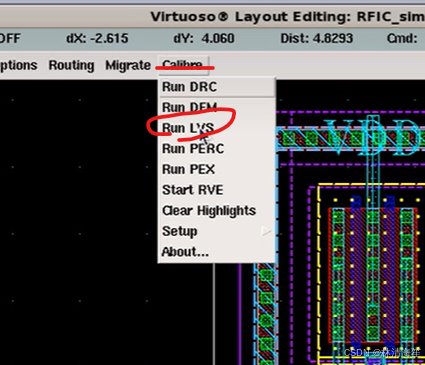

选择Calibre——Run LVS

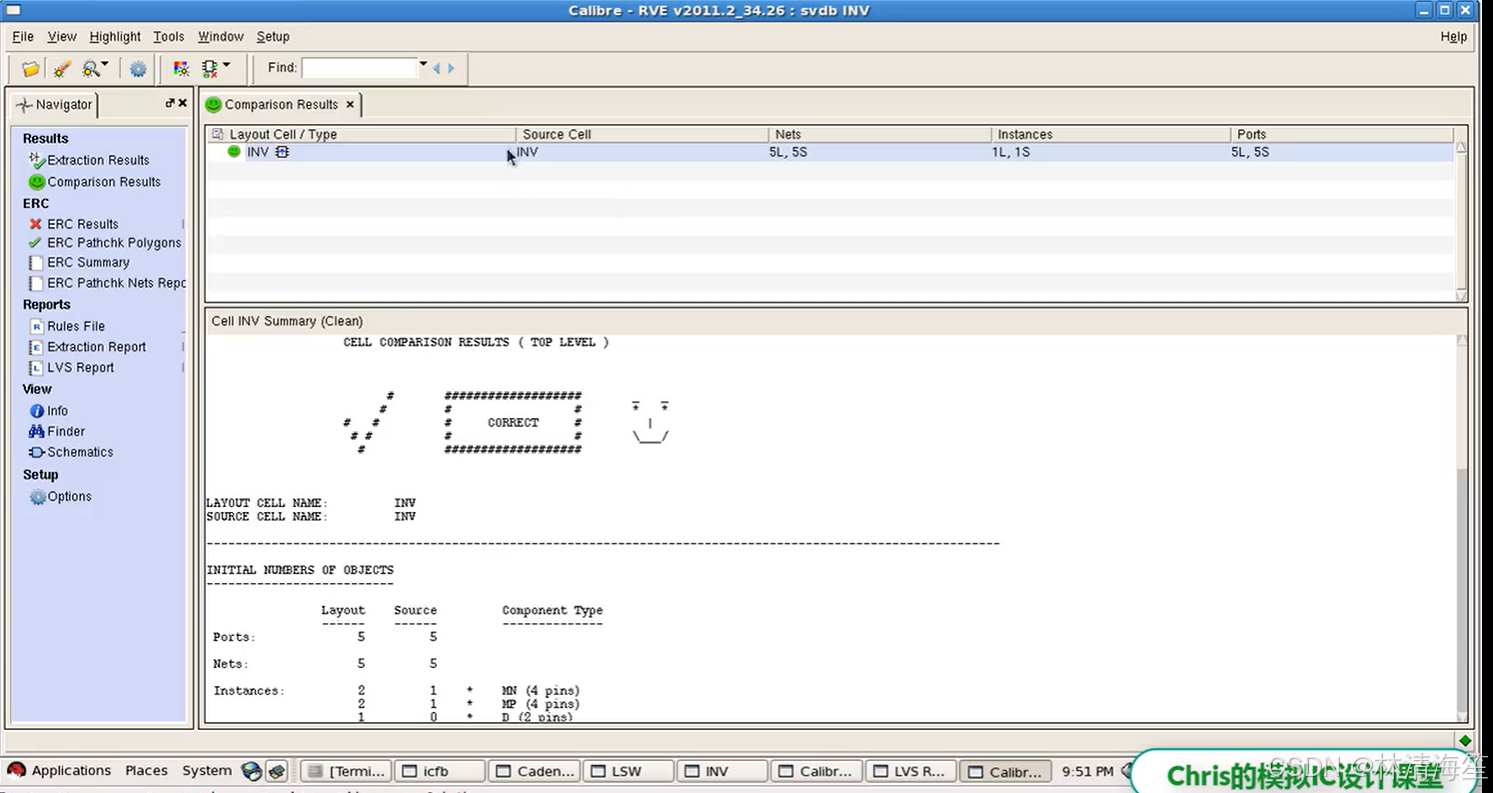

运行完成后弹出LVS的结果

绿色标志标识LVS是通过的

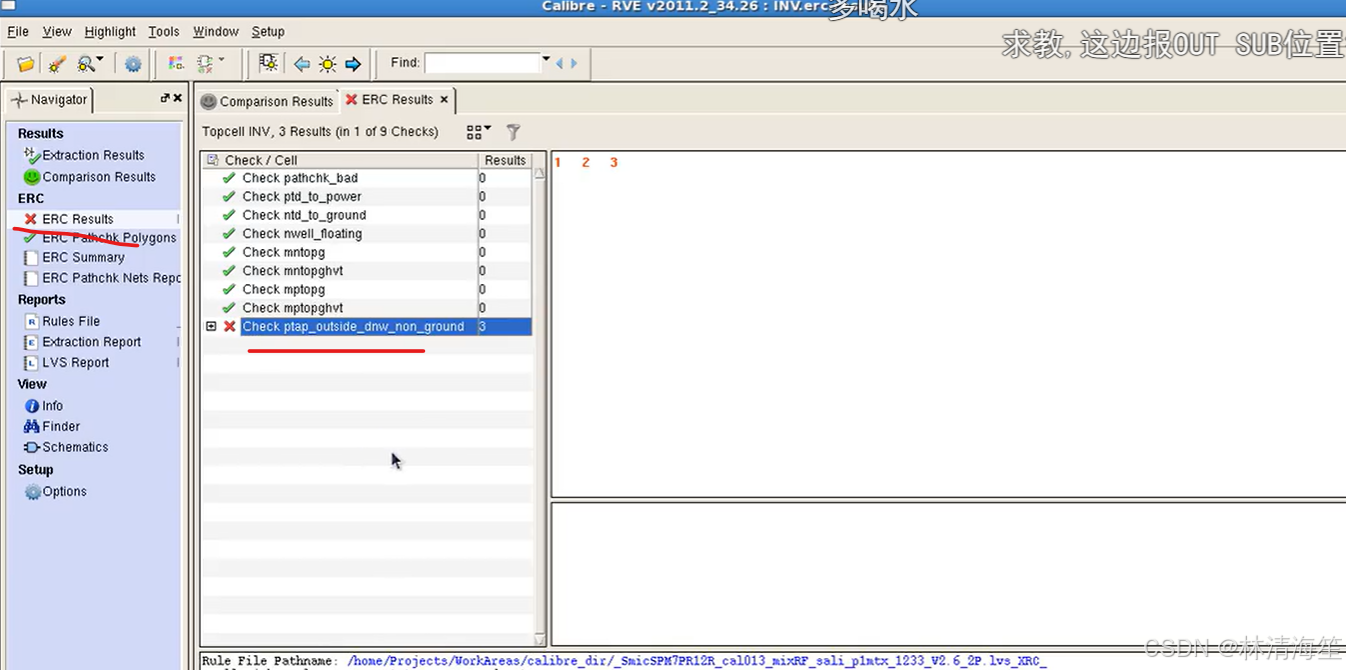

再去查看ERC结果,发现有一个错误,Pwell没有连接到地网络。

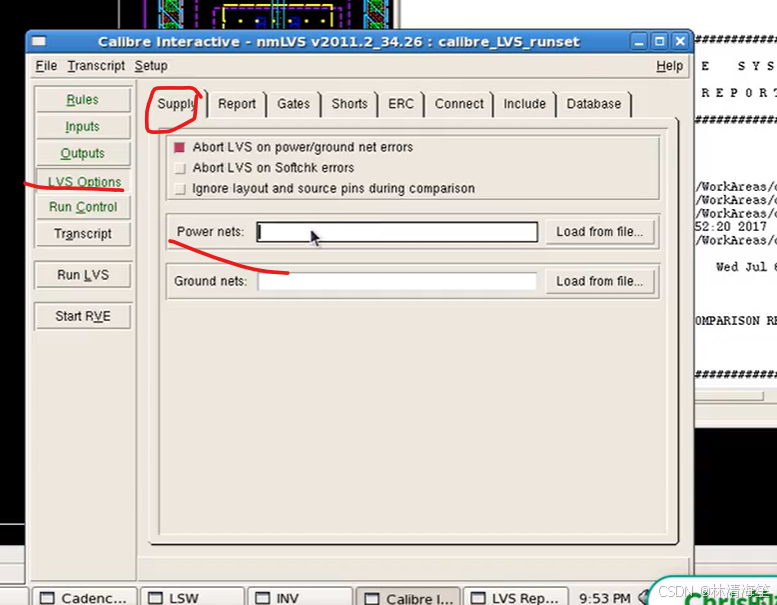

我们返回到LVS中,添加电源网络

Ground和SUB都填为地网络

这时候再去跑LVS

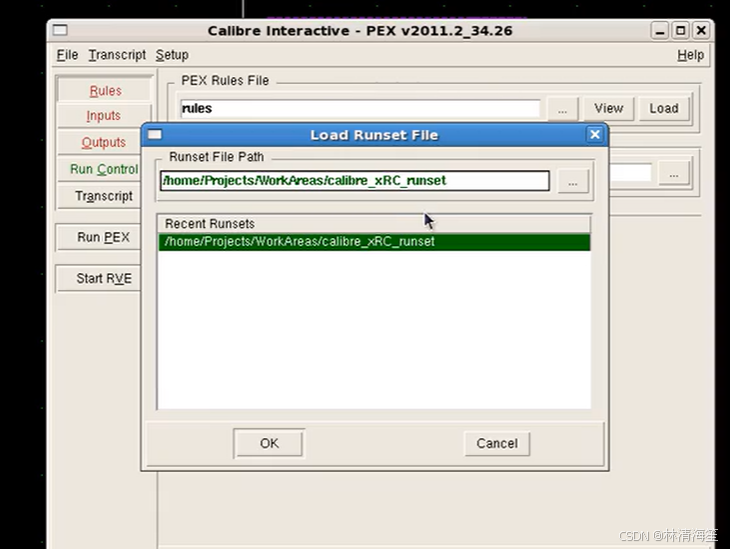

3.提取寄生参数——后仿真

选择Calibre——Run PEX

这里选择xRC——runset文件

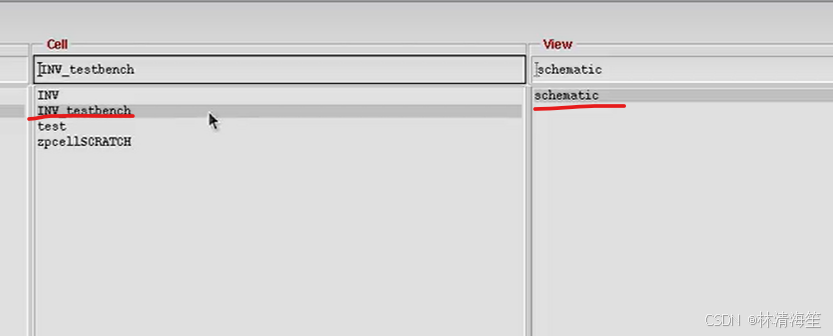

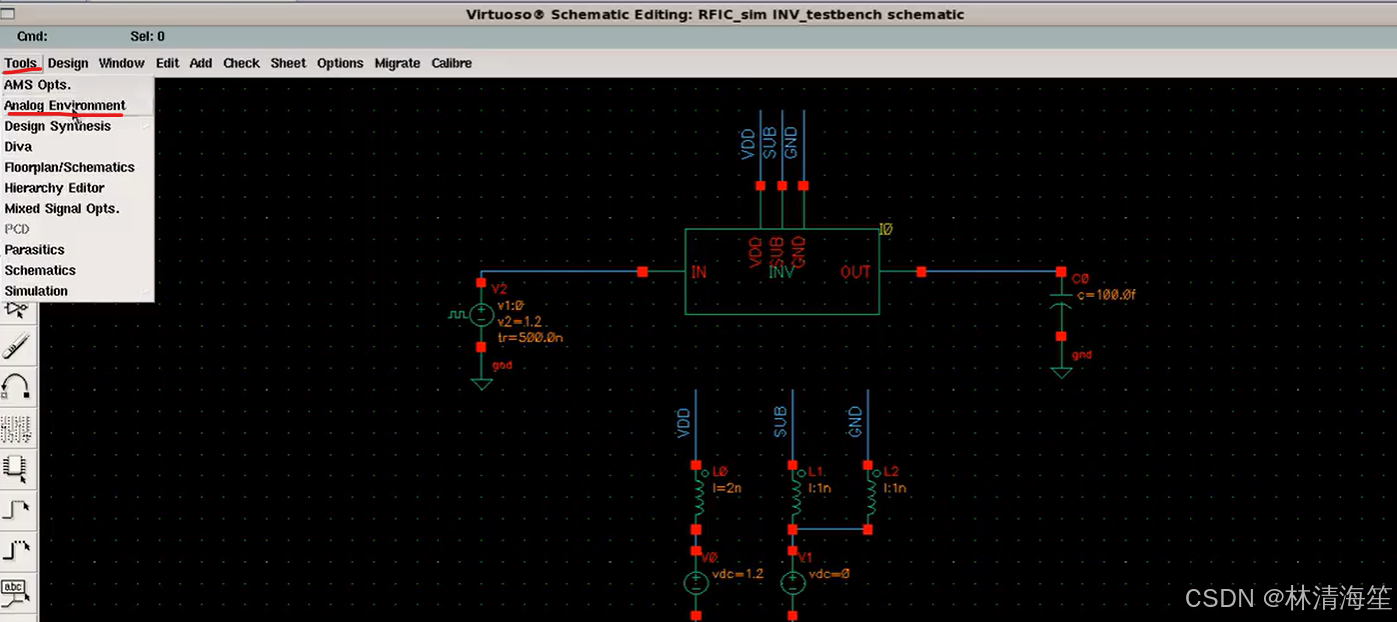

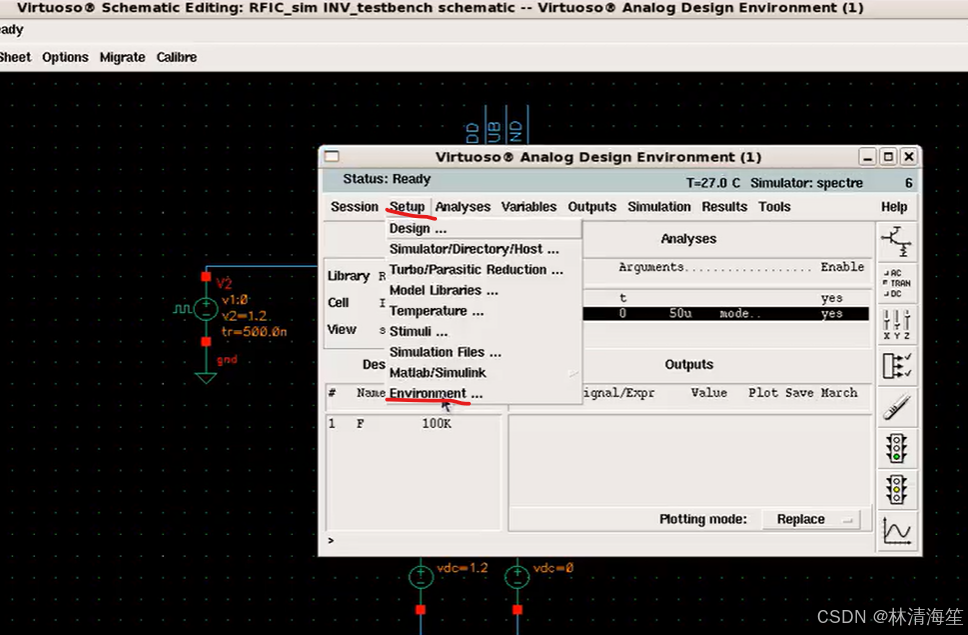

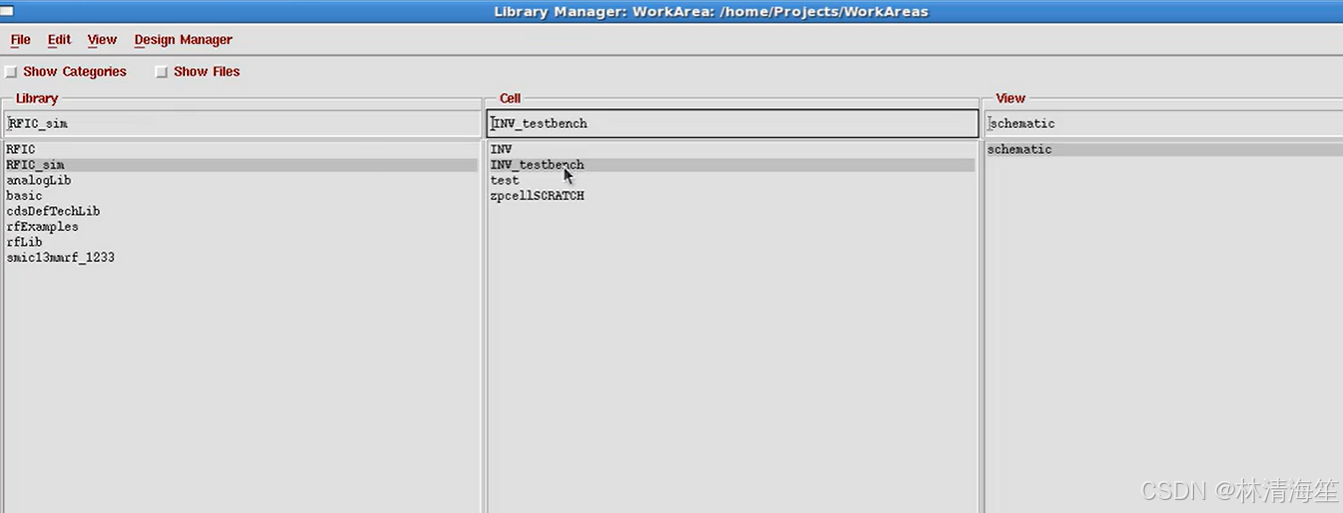

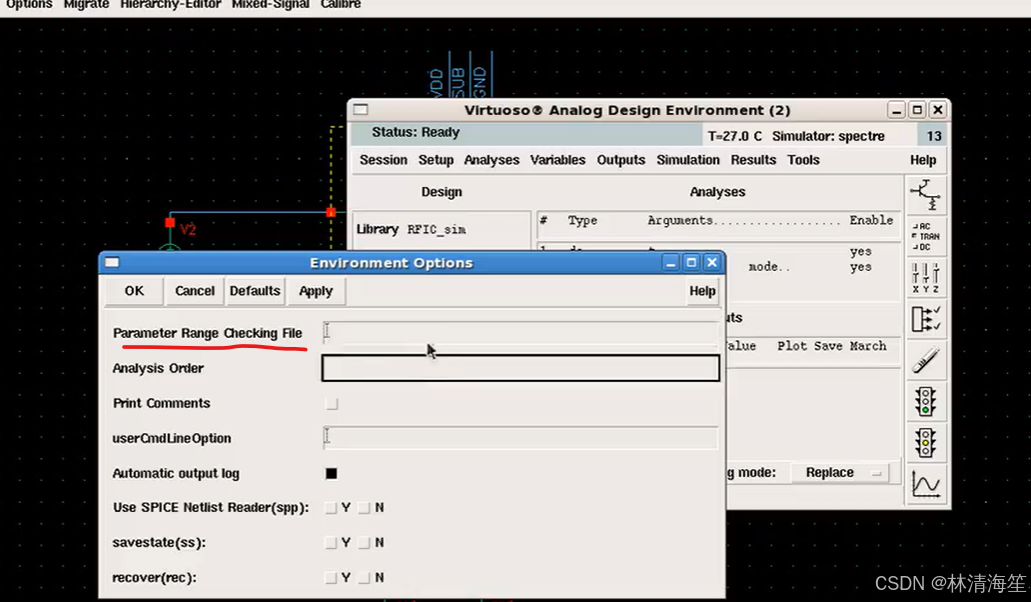

现在打开仿真用的test_bench

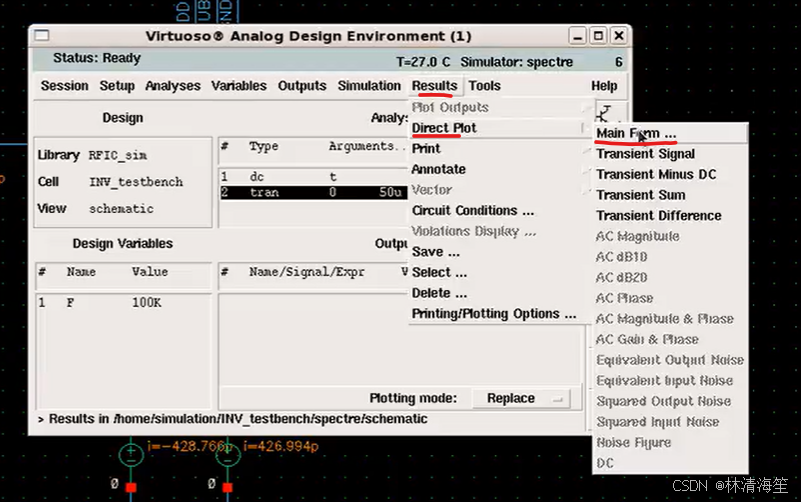

打开模拟仿真环境Tools——Analog Environment

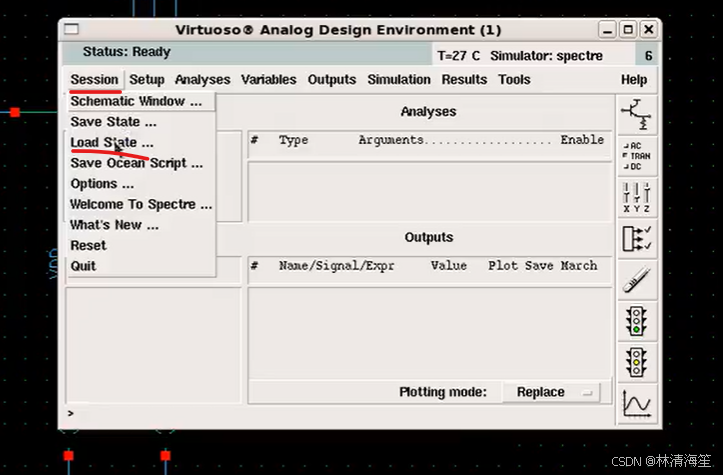

调入之前保存下面的state

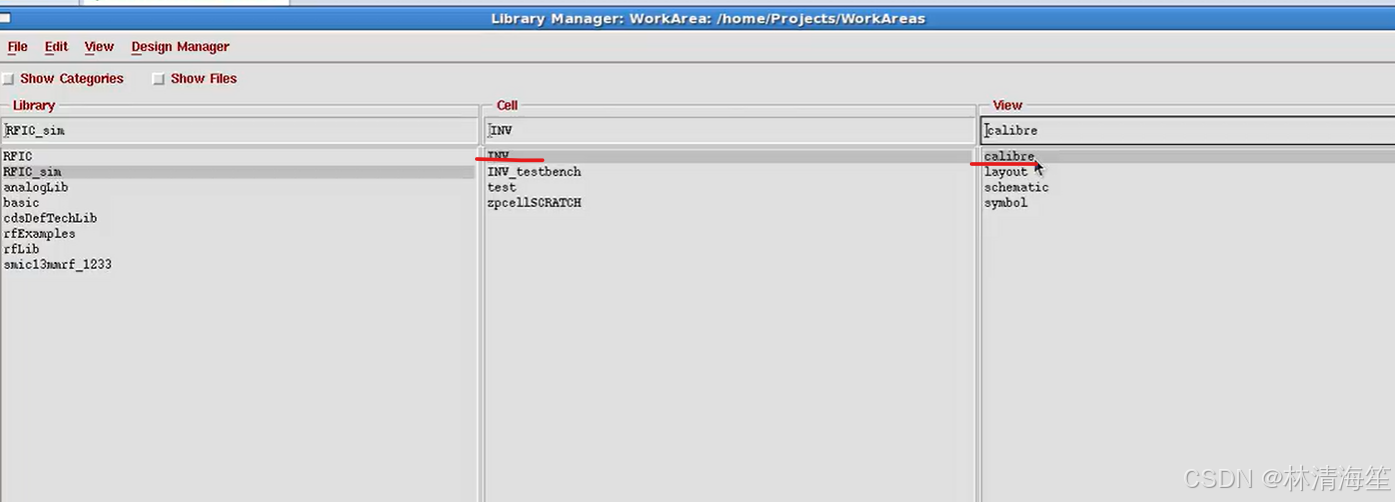

然后返回到liarary,发现在INV下又多了Calibre文件,这个就是提取出来寄生参数的文件了,包括本身的电路,和提取出来的寄生参数

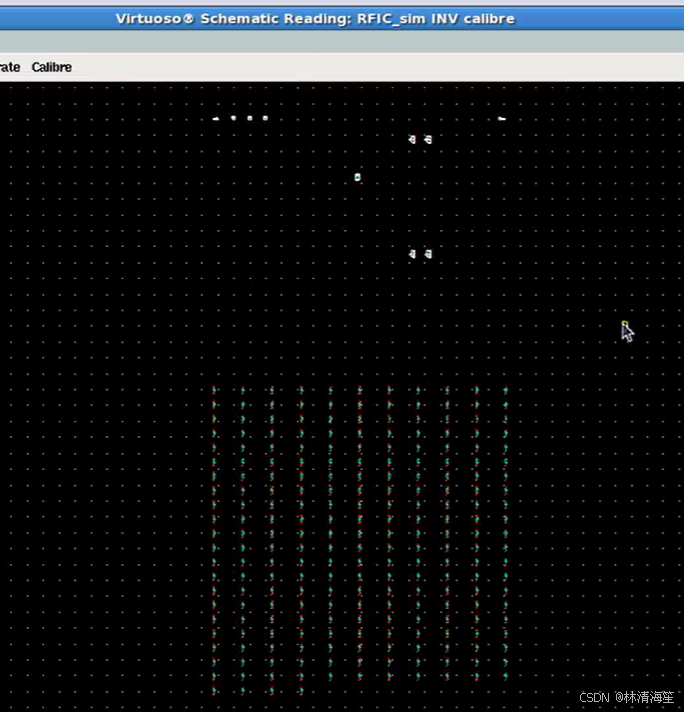

打开后发现,上面部分是原来的原理图元器件及端口的设置,下面的部分就是提取出来的寄生电阻和寄生电容。

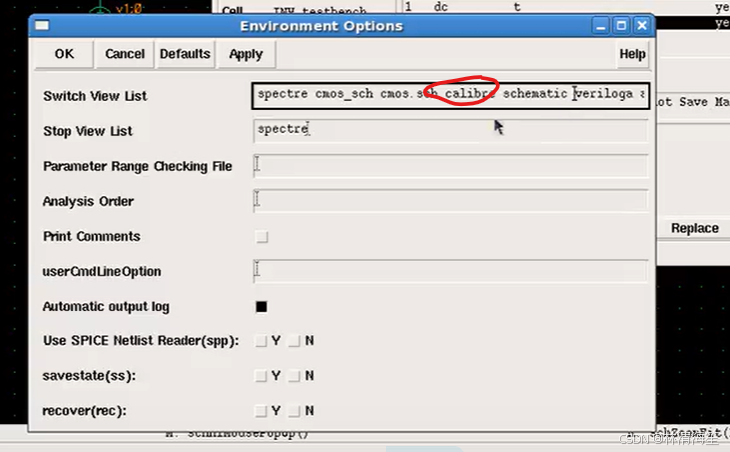

进行后仿真的第一种方法

我们在窗口网表中,schematic前面加上calibre。这样就可以先调用子电路的calibre进行仿真,而不会去调用原理图进行仿真了。这样就能实现后仿真的功能。

然后点击运行。

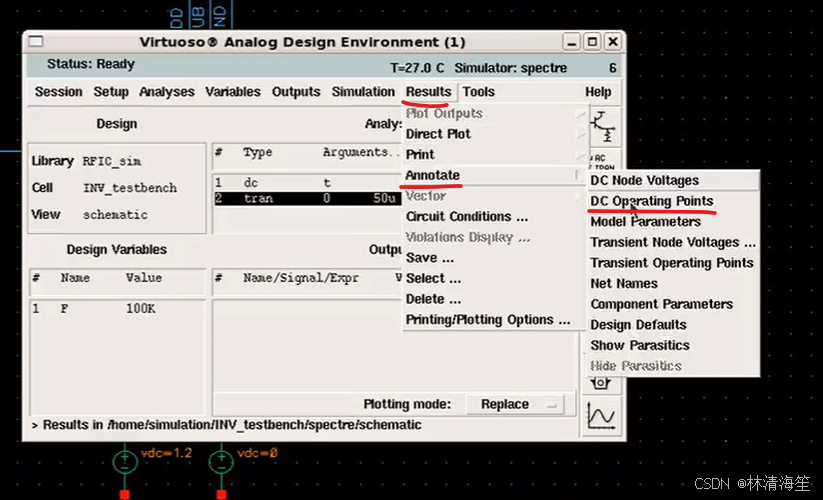

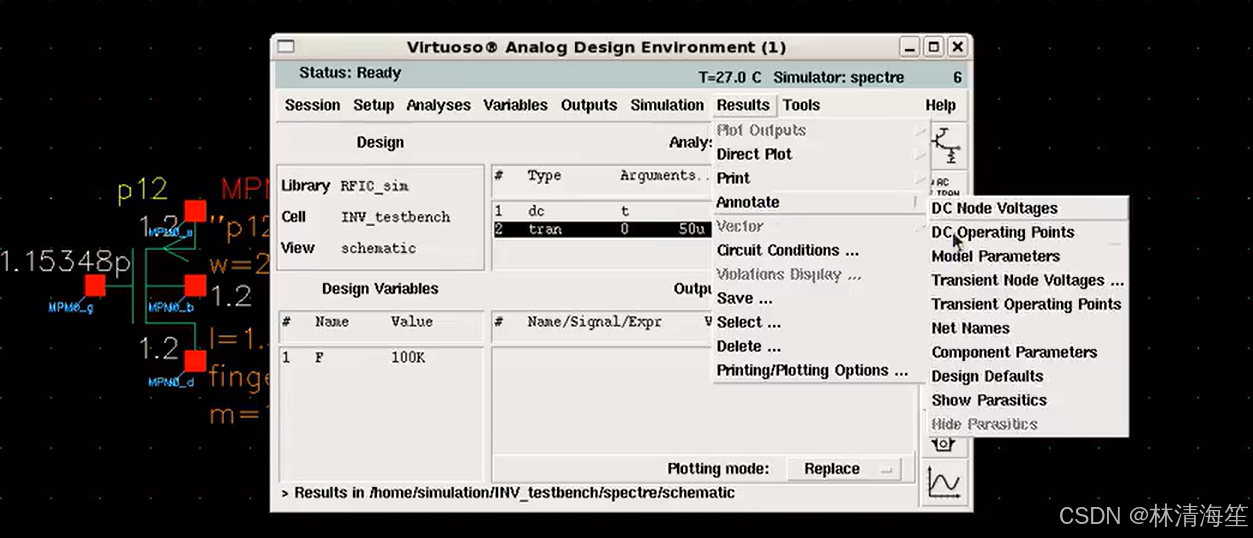

运行完成后先查看直流工作点,然后再查看直流工作电压。

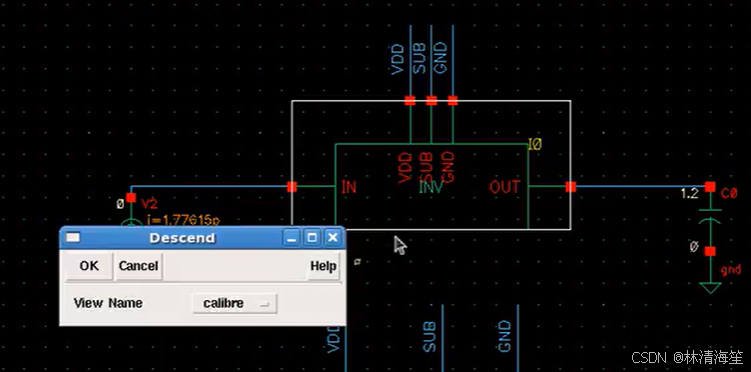

这时候我们进入到calibre view中查看。

我们按住键盘上的E键,进入到

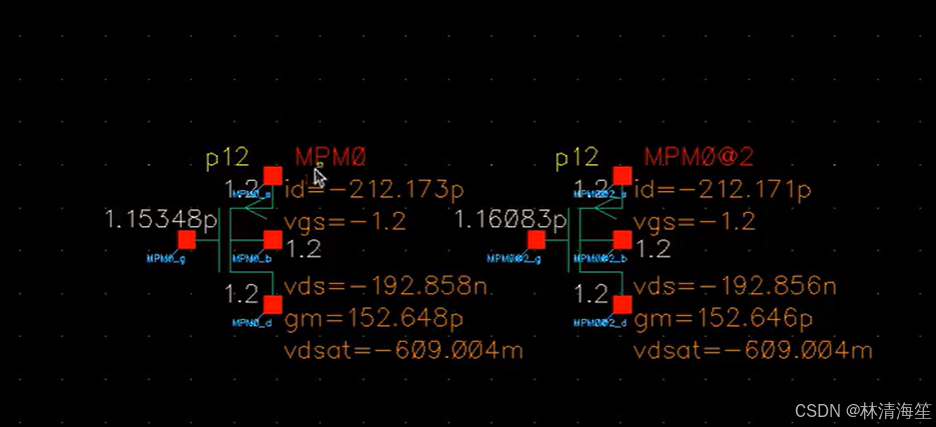

这时候我们查看放大后的晶体管,能够看到每个晶体管端口的电压是多少

然后查看直流工作点,

这时候每个点的电流都是能显示出来的。

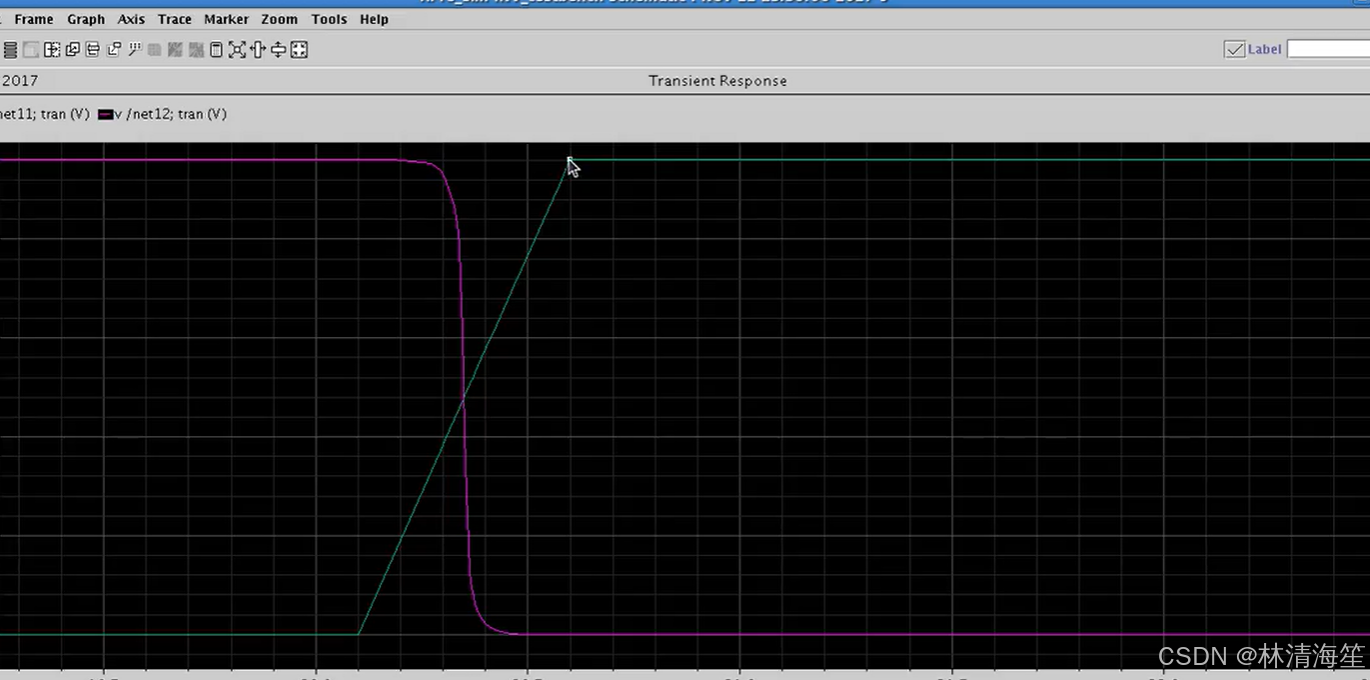

然后我们再查看瞬态的波形,将波形画出来看下

能够看到跟前仿真时差不多的

第二种方法(简单电路)

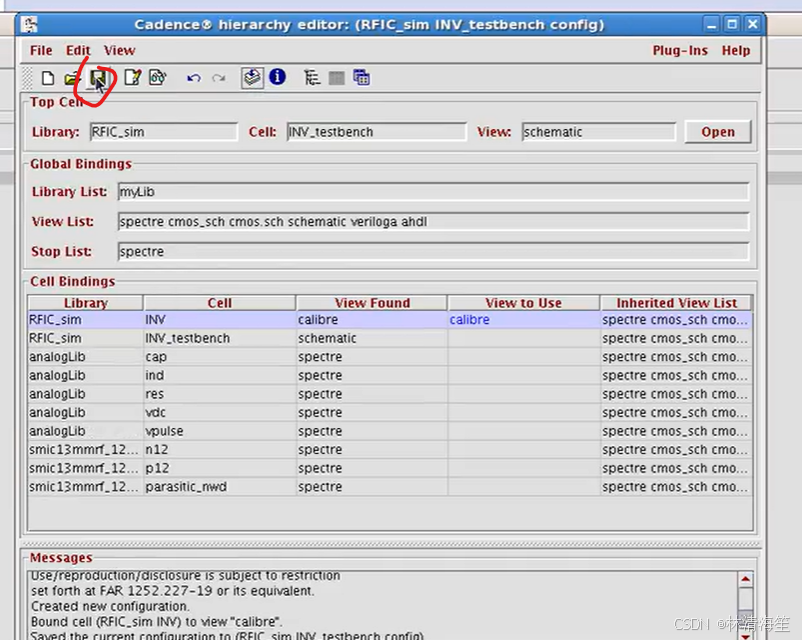

就是用config文件,是层级仿真的配置文件

首先选中要加载文件的config

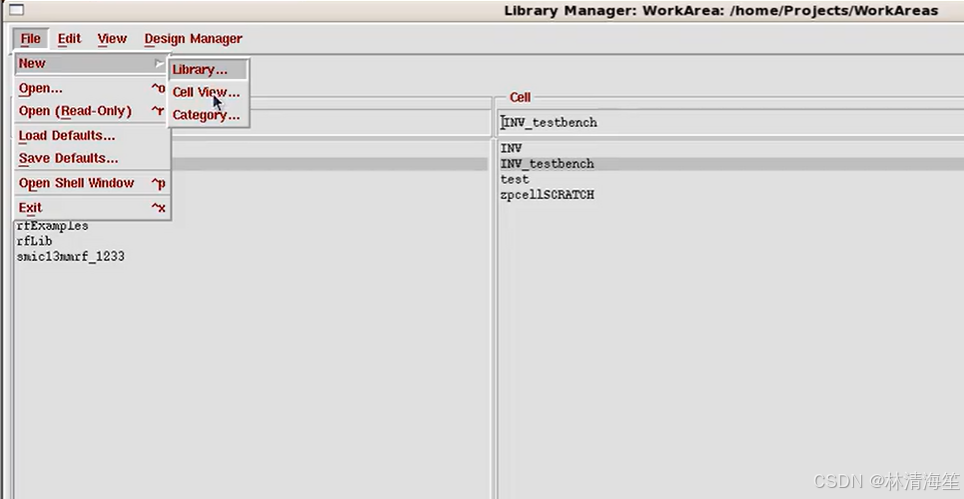

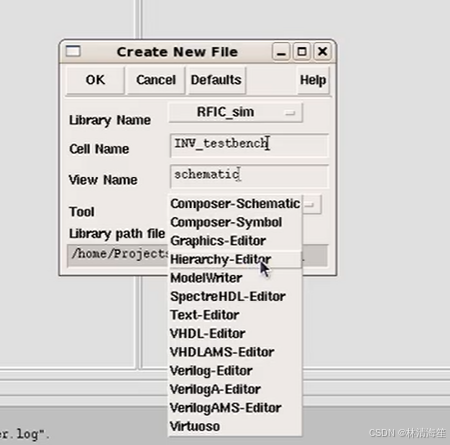

点击file——new——cell view

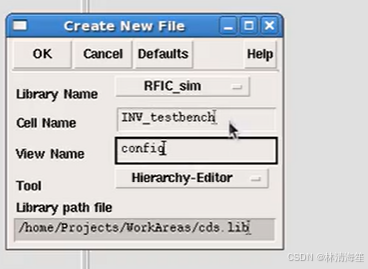

然后选择层级编辑器hierachy editor

然后view name就会变成config

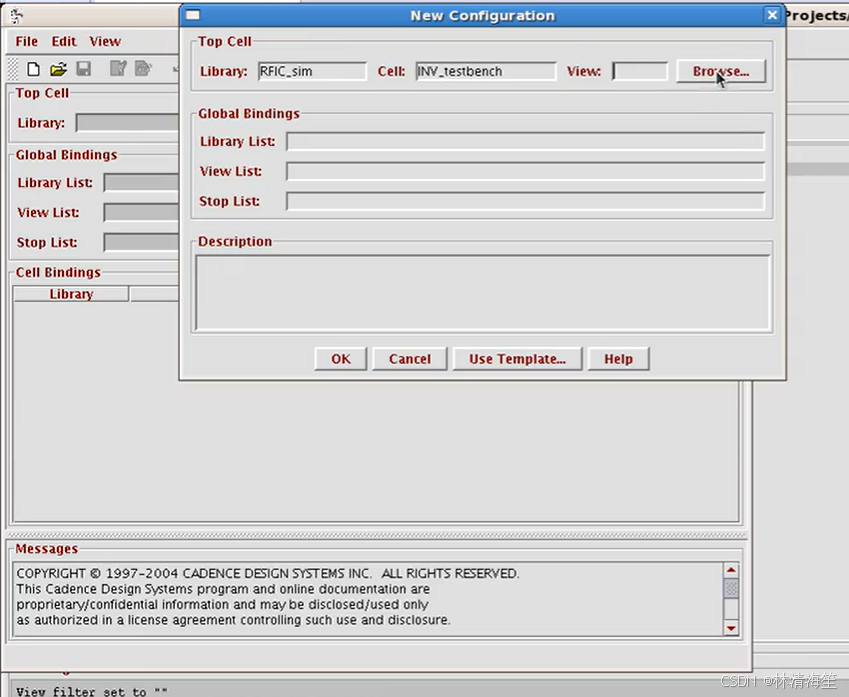

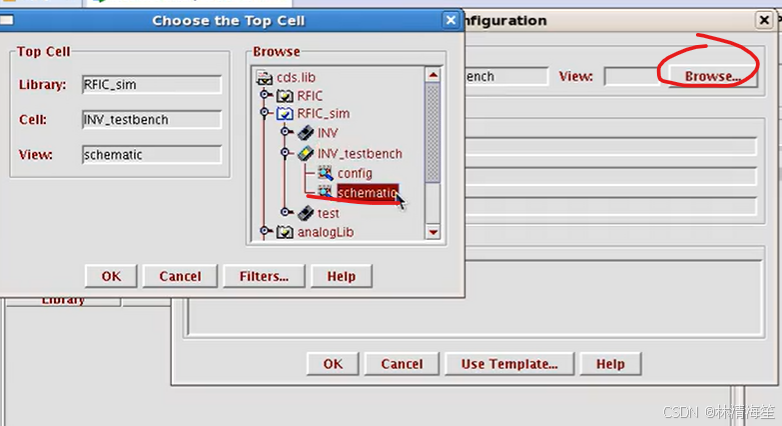

然后回弹出对话框

这时候我们选择browse,选择电路原理图schematic

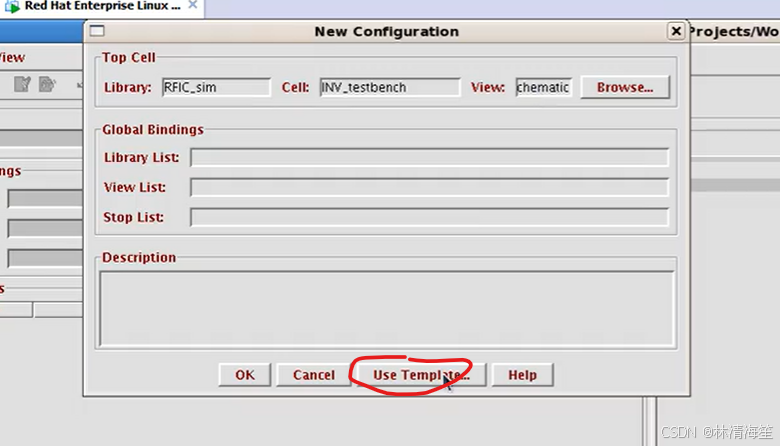

选择完电路后选择use template,即模板

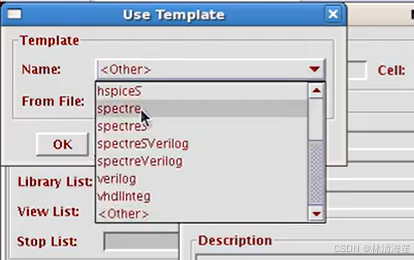

Name我们选择spectre,

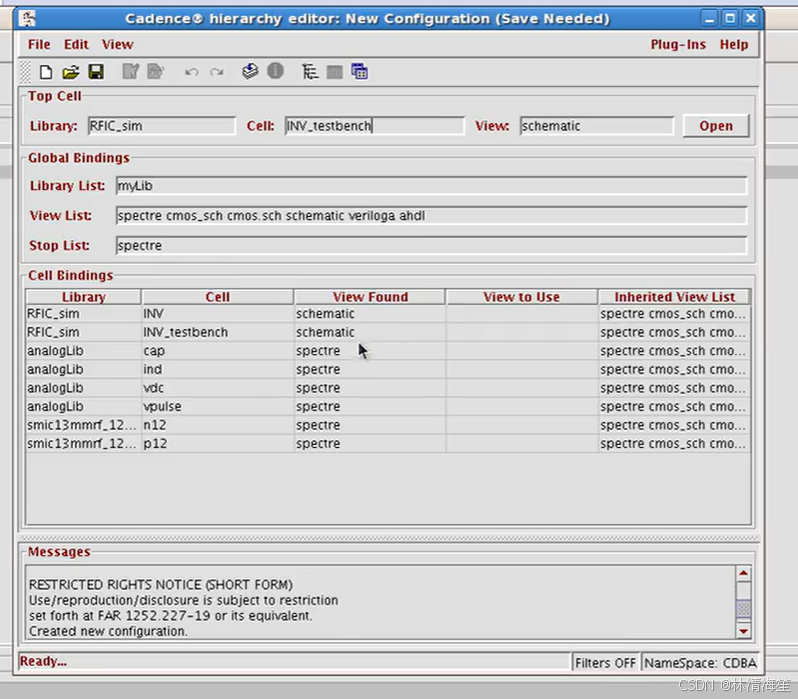

然后都惦记ok

然后全部的config配置就全部都调入进来了

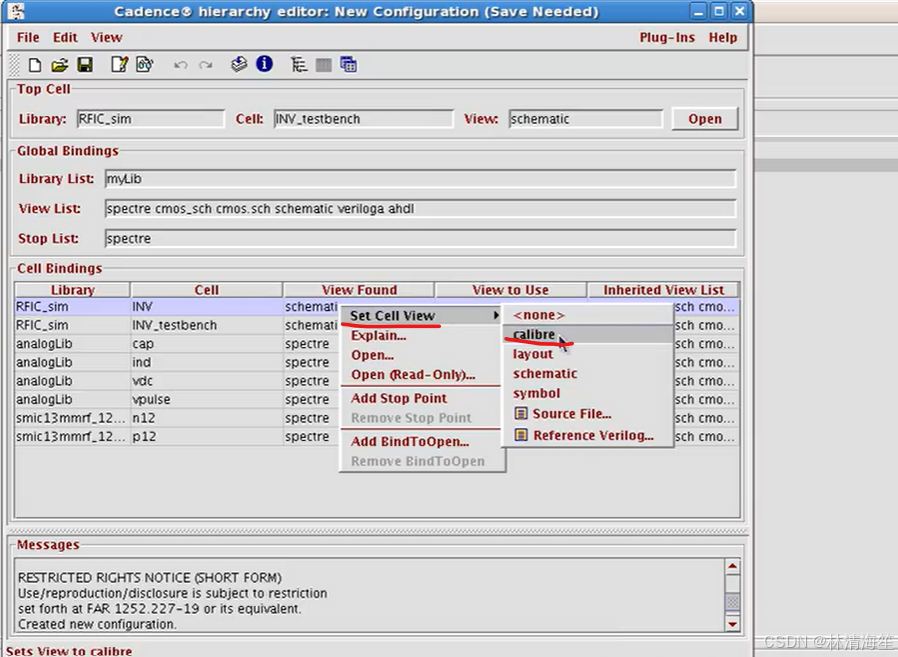

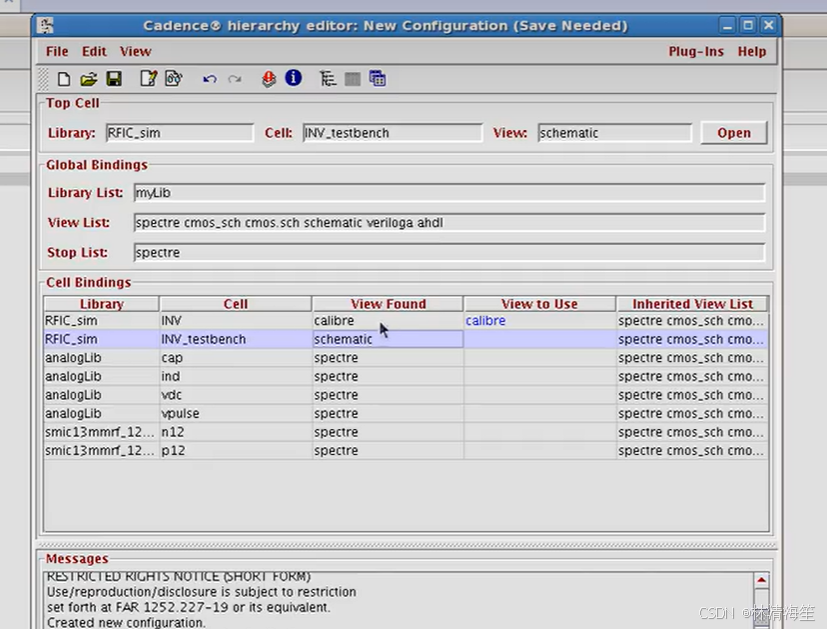

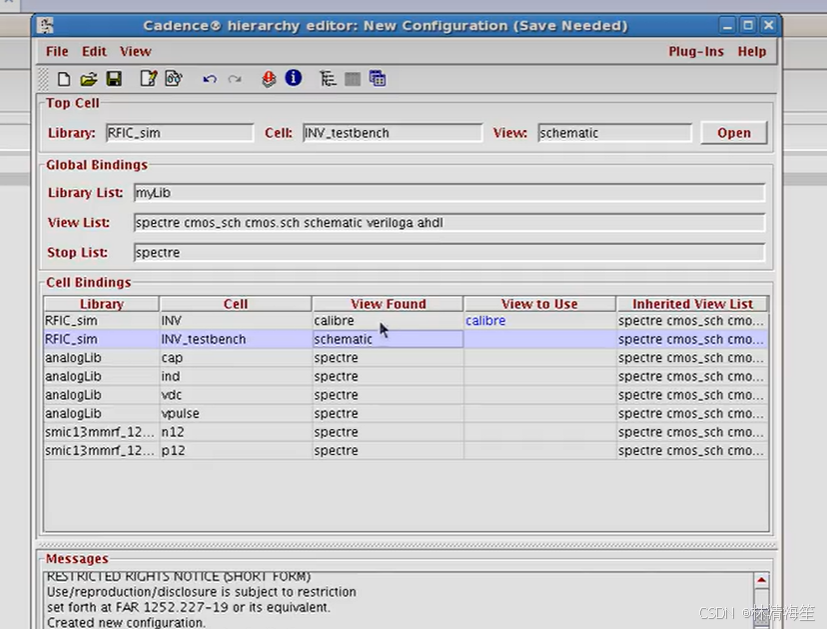

首先选择INV的子电路,鼠标右键选择schematic,选择calibre

这时候电路在仿真的时候,就会调入calibre文件。

这样做的好处是,假如test bech包含有很多子电路的话,有的电路需要采用原理图的方式,有的电路可以采用calibre方式,通过不同的组合,能够进行后仿真的验证

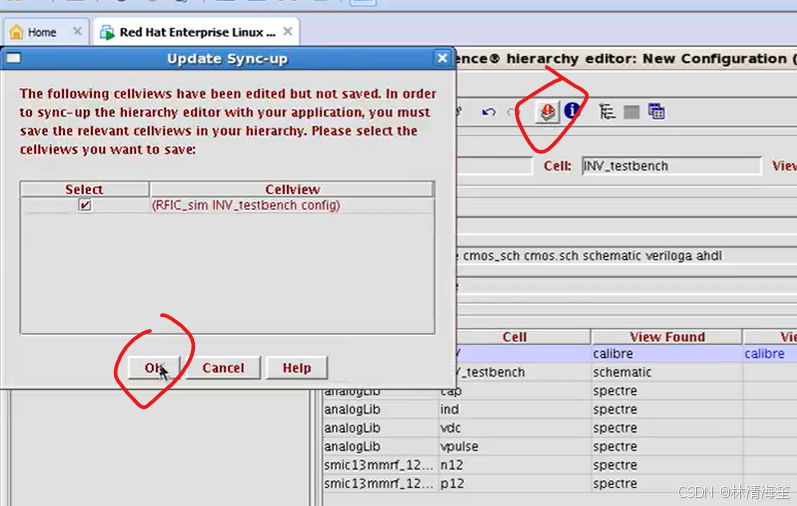

设置完成后点击保存

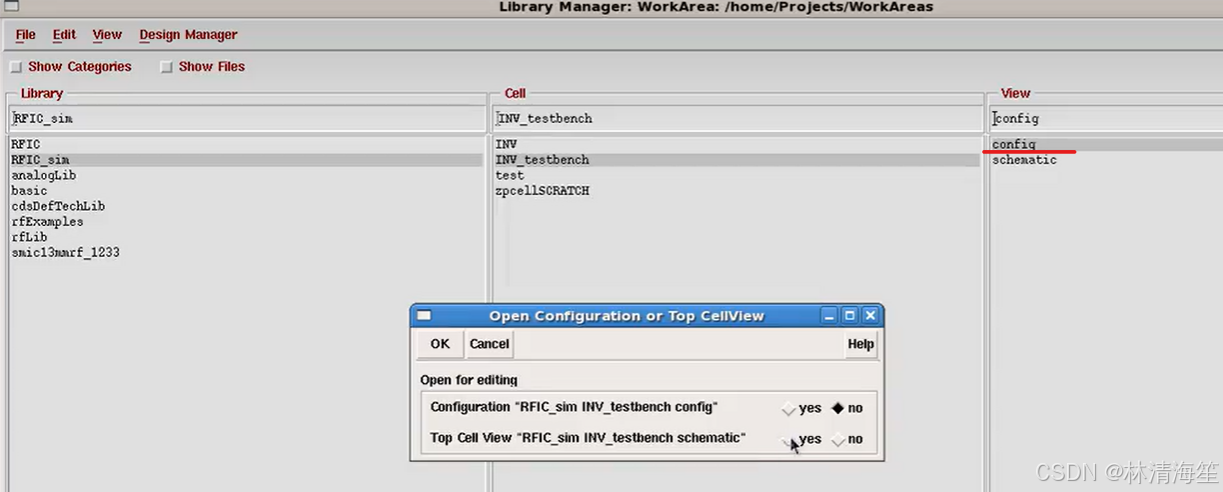

然后退出打开config文件,这里选择不打开配置文件,只打开原理图

后面的操作跟方法一是一样的

只是在调入文件的时候是空的

4681

4681

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?