过去了几天,在搞一些别的事情,就把这个耽搁了,也因为是初学者,这个版图也是自己根据原理图绘制的,版图画的不是非常美观。

2023/2/22,将版图重新绘制,在下方。

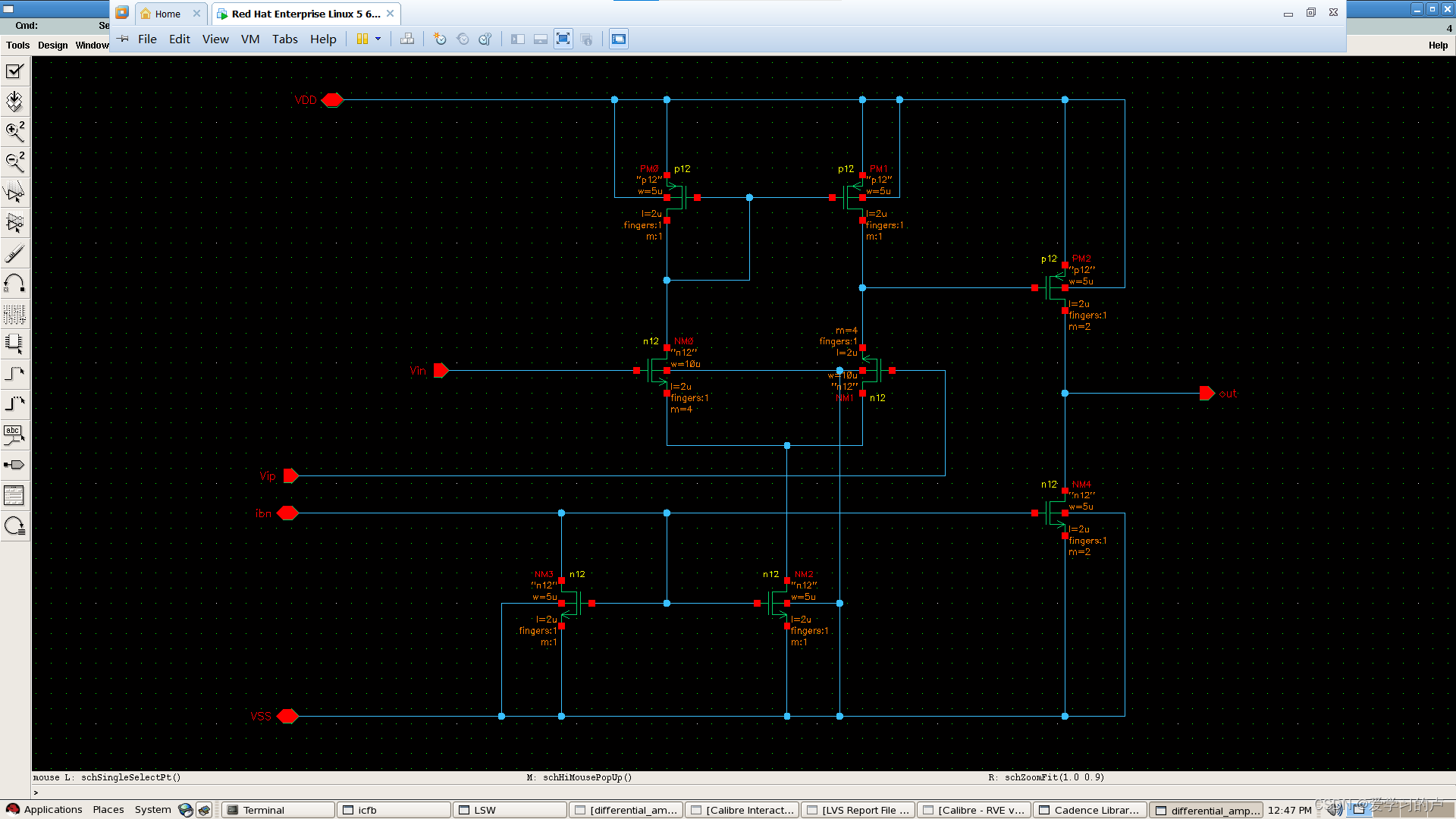

首先仍然是绘制原理图:

check and save检测是否有端口没有衔接好。

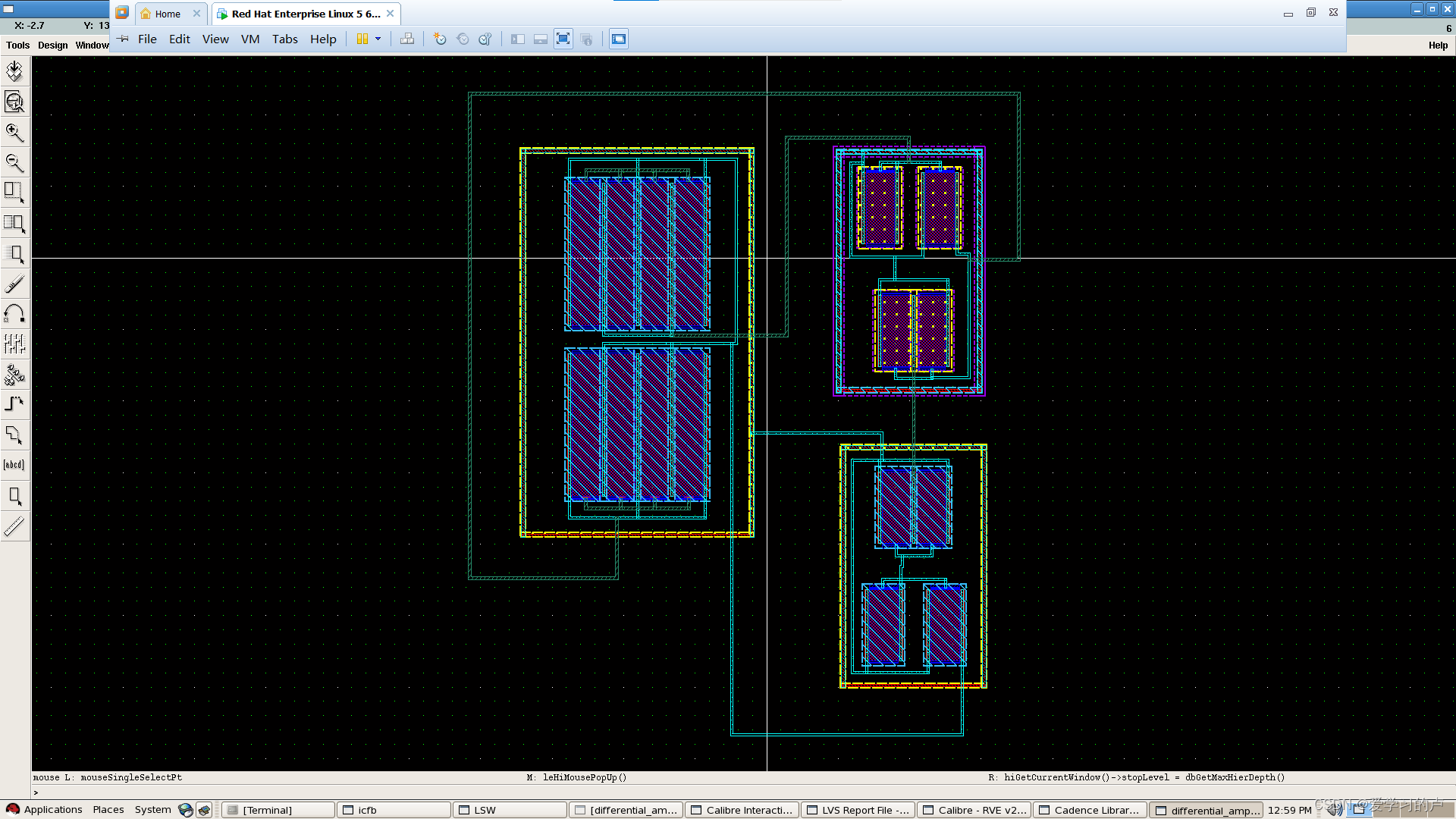

开始绘制版图:

线画的不太规整,这里我是将两个m为4的NMOS放在一起并用隔离环隔离,将上方的PMOS放在一起也用隔离环隔离,最后将下方的NMOS放在一起用隔离环隔离,首先要将m不为1的管子相互交叉,共用一端;然后将源端和源端连上线,这里我默认的是左源右漏。接下来就是连线,这里我用了M1与M2金属线,所有接口都是通过M2金属线接出去,M1线用来连接各自的源漏端,按照原理图一个一个连接起来,注意的是隔离环是有M1接触孔的,所以可以用M2接出去,或者从下面绕出去。

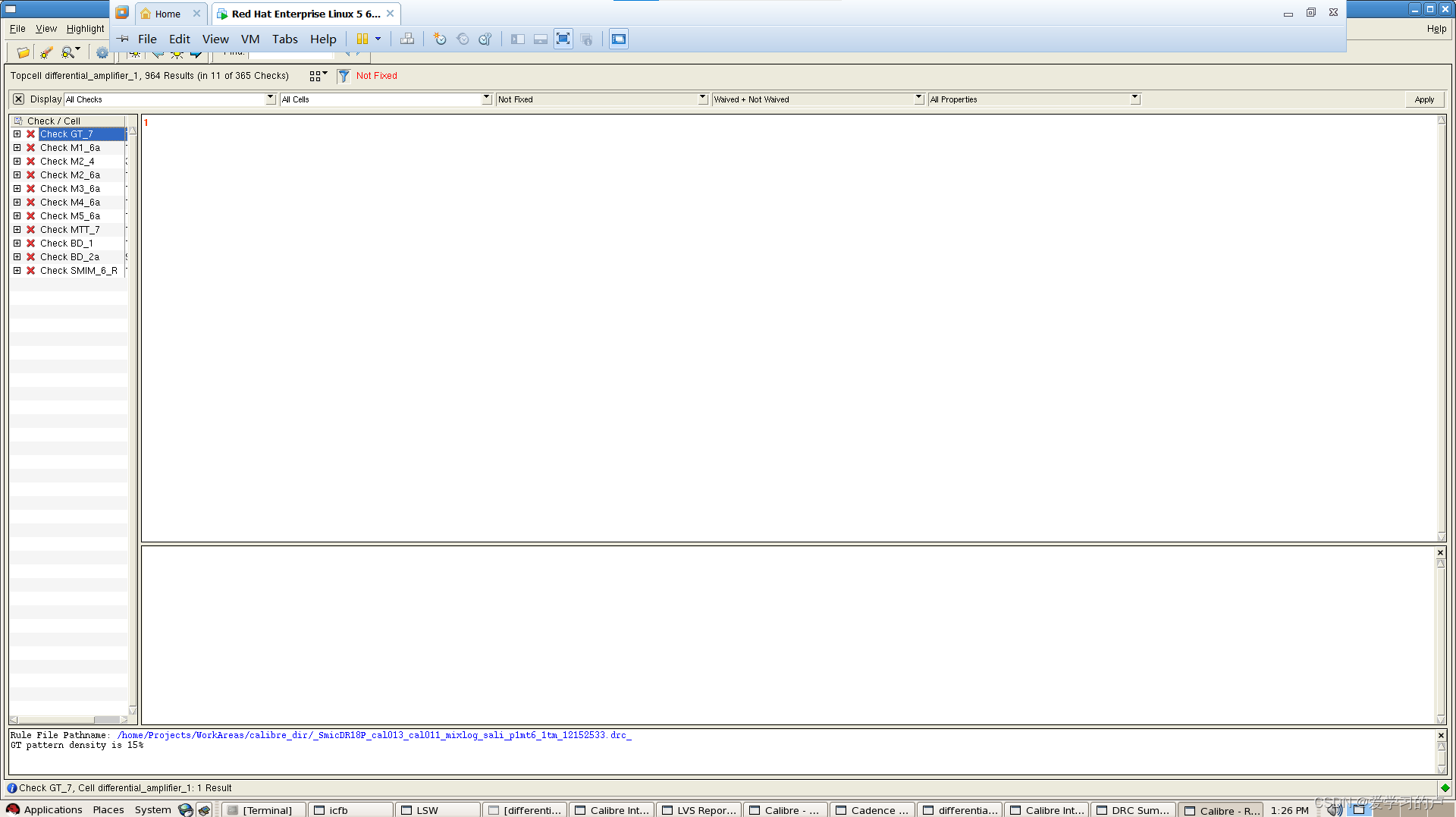

DRC验证:

经检查,都是面积与密度问题。

LV

作者作为初学者,重新绘制了电路版图,采用更规整的方式布局NMOS和PMOS,使用隔离环并优化金属线连接。经过DRC和LVS验证,新版图面积更小,仅用3层金属,且满足差分对和电流镜的匹配要求,解决了之前的连接问题。

作者作为初学者,重新绘制了电路版图,采用更规整的方式布局NMOS和PMOS,使用隔离环并优化金属线连接。经过DRC和LVS验证,新版图面积更小,仅用3层金属,且满足差分对和电流镜的匹配要求,解决了之前的连接问题。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1473

1473

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?