之前绘制过差分放大电路的版图,前几个月又进一步的学习绘制了进阶篇的差分放大电路(因为这几个月在搞毕业设计,没时间发布所以就挪到了今天发布一下,记录学习的过程吧

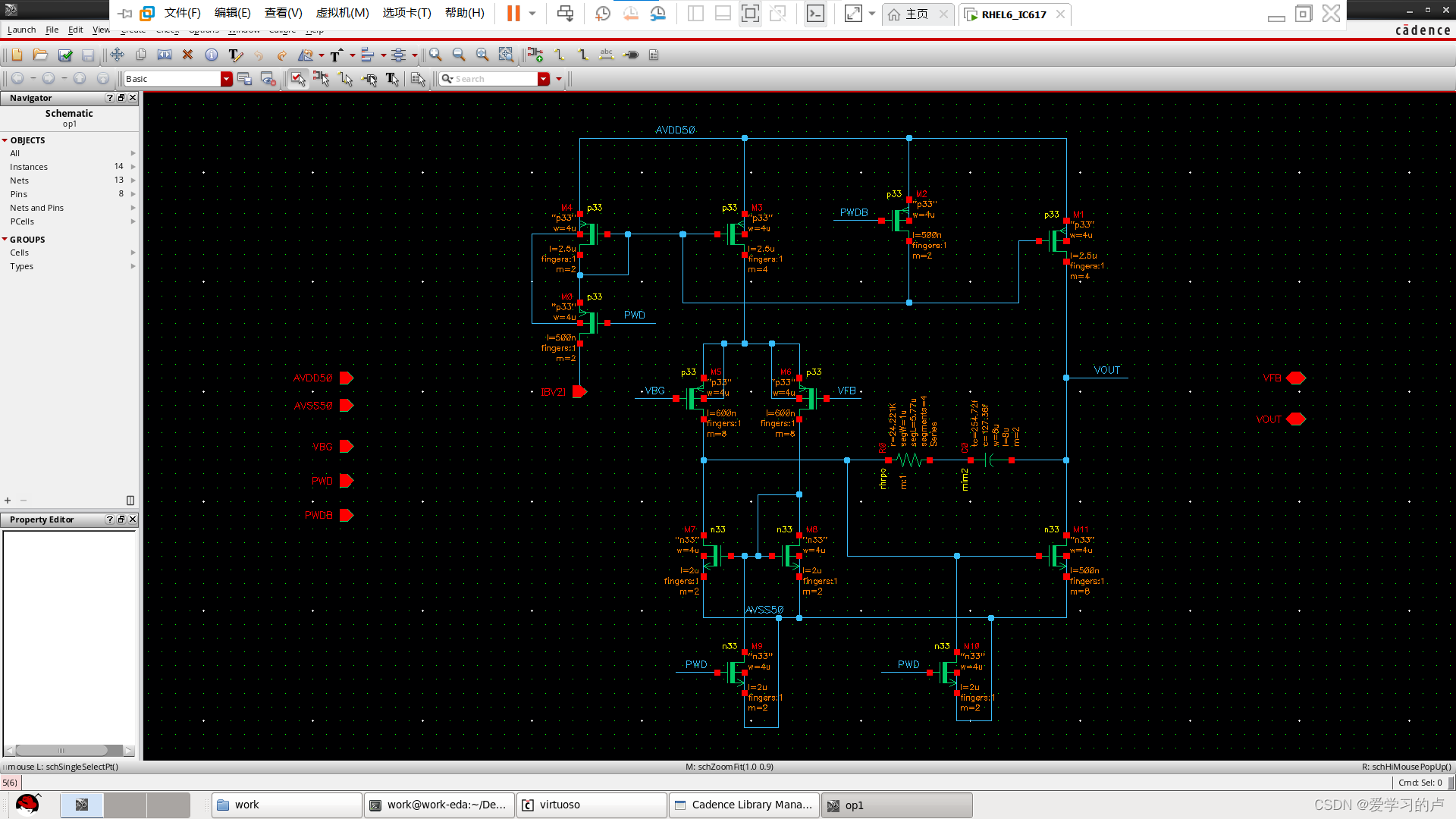

首先是电路原理图的绘制:

这个原理图较上一次的差分放大器复杂,毕竟是进阶篇嘛,其中包含了RC串联电路,这对于版图来说基本上所有的器件都集中在这一个原理图中了,这里的串联电阻目的是电阻起阻尼作用, 电阻消耗过电压的能量,从而抑制电路的振荡;电容的作用就是防止电压的突变,这里我也不太了解,如果说的不对欢迎在评论区下方指出。

接着说原理图部分,绘制版图时需要知道什么和什么放在一起,这里的话我将M1;M3;M4放在一起,因为首先他们是共源级接法,其次他们的栅极接在同一个地方,绘制版图的时候将其放在一起排列方式按照ABBA方式排列,并用GuardRing围在一起;然后就是剩下的M2和M0两个PMOS器件,把这两个也用一个GuardRing围起来,这样的话上面的电流镜部分就绘制完成,下面的NMOS也采取这种画法。

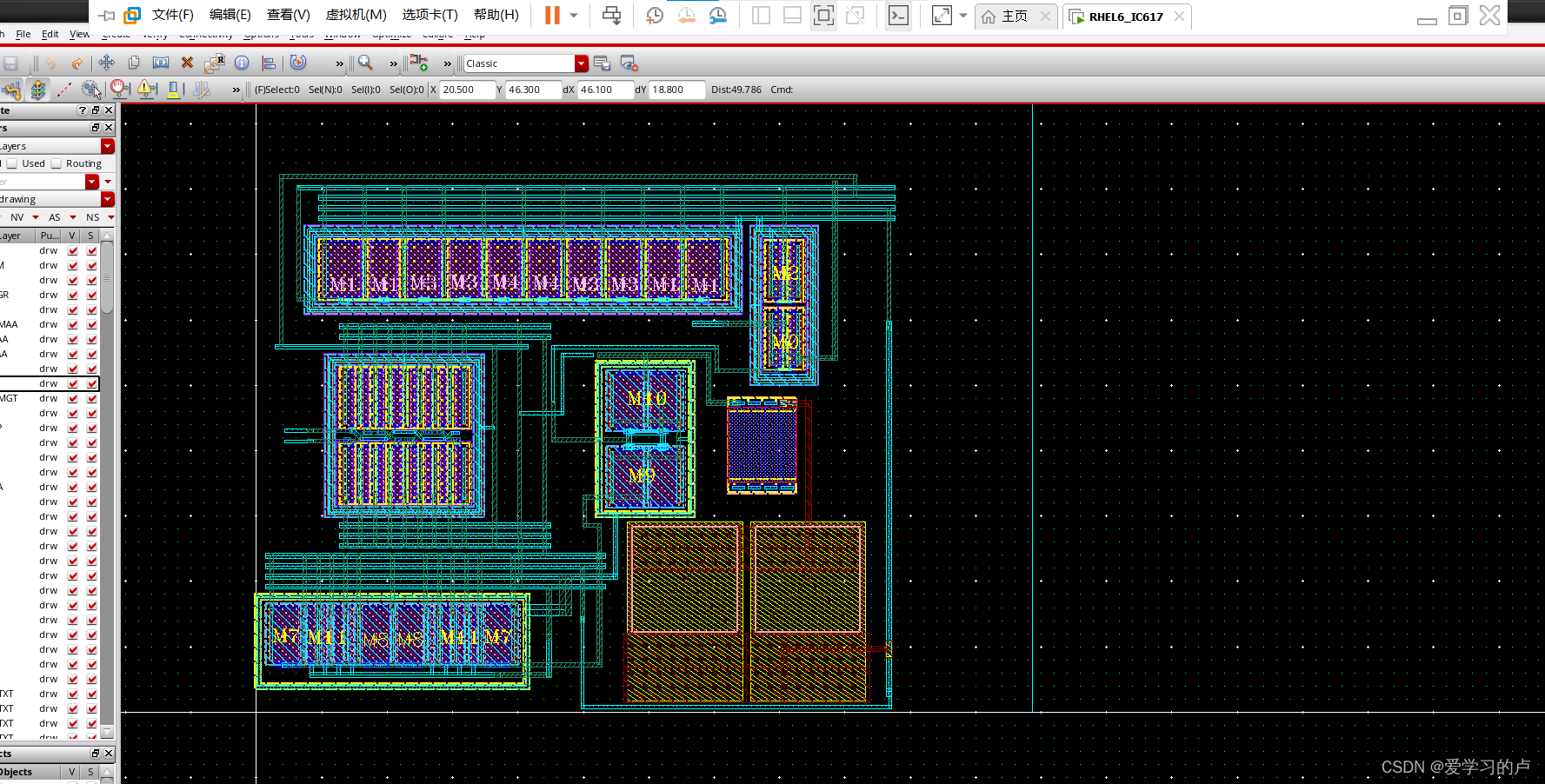

接下来就是差分对的匹配,和上一节一样采取ABBA;BAAB的匹配方式,这里就不过多进行介绍,注意的是走线方式采取的交叉走线,这里就需要注意DRC是否能够通过,走线通过F3调diagonal用斜走线的方式。

与上一节不同的是因为GuardRing是M1层金属,所以我直接通过M2打孔走线,使得GuardRing围的环足够小,大大节约了版图的面积,还有一个好处是引出来的线更容易的进行走线以及打孔。

最后便是电阻电容的走线,因为这里我用的是IC617,也是第一次在这里画版图,之前都是在老版本IC5141上画,所以对于电容版图我不确定是几层金属绘制,所以我将原有的电容版图进行一个打散的操作,发现其电容是M5和M6层金属叠加而成,所以从电阻走出来的线通过反复打孔最后到达M5层与电容进行连线。版图便绘制完成。

成品如下:

这里我将所用到的器件进行了高金属层命名,方便读者观看。并且排版布局贴近正方形,观看更加舒适。

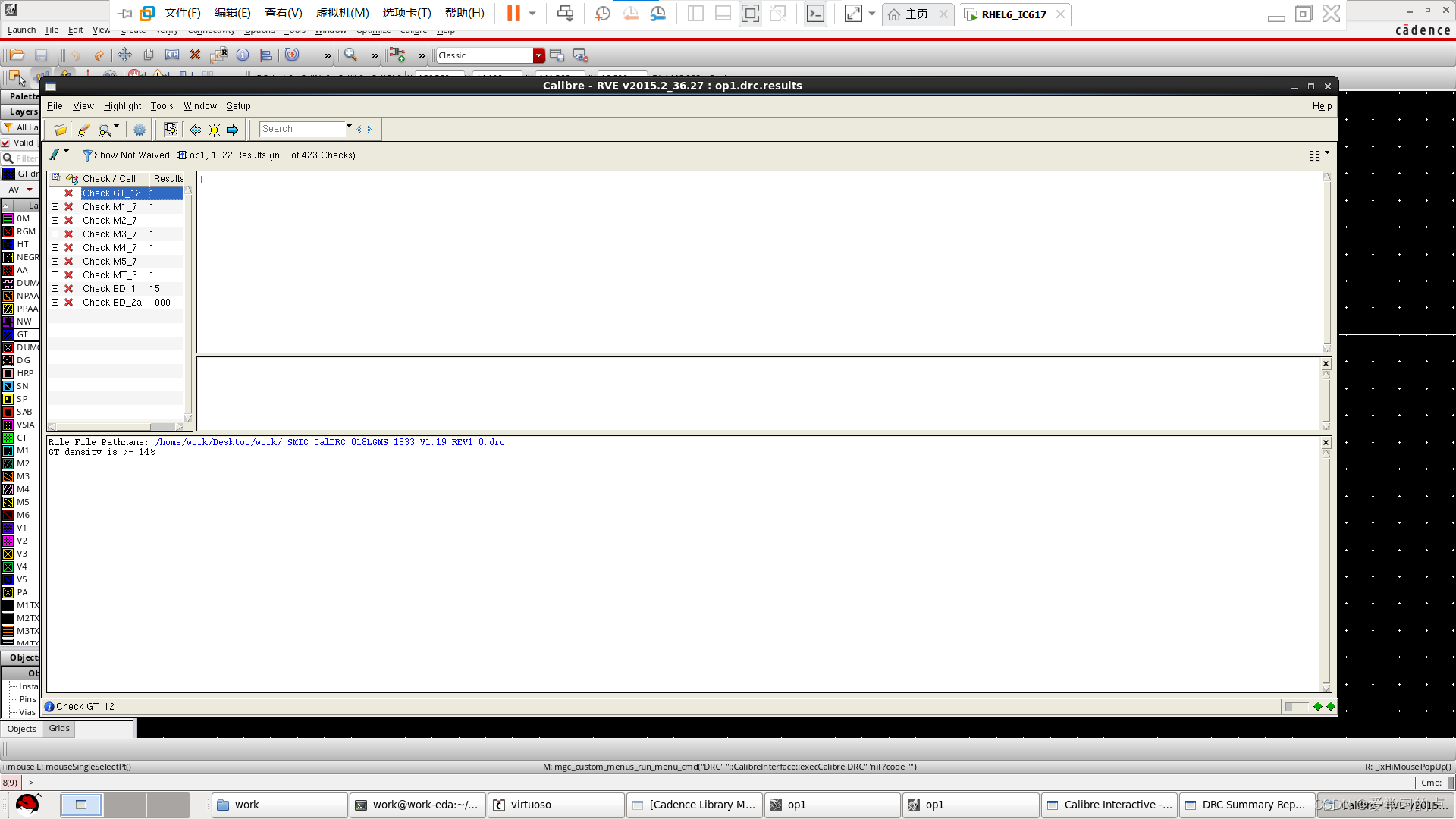

DRC:顺利通过,密度以及面积错误 LVS:出现笑脸

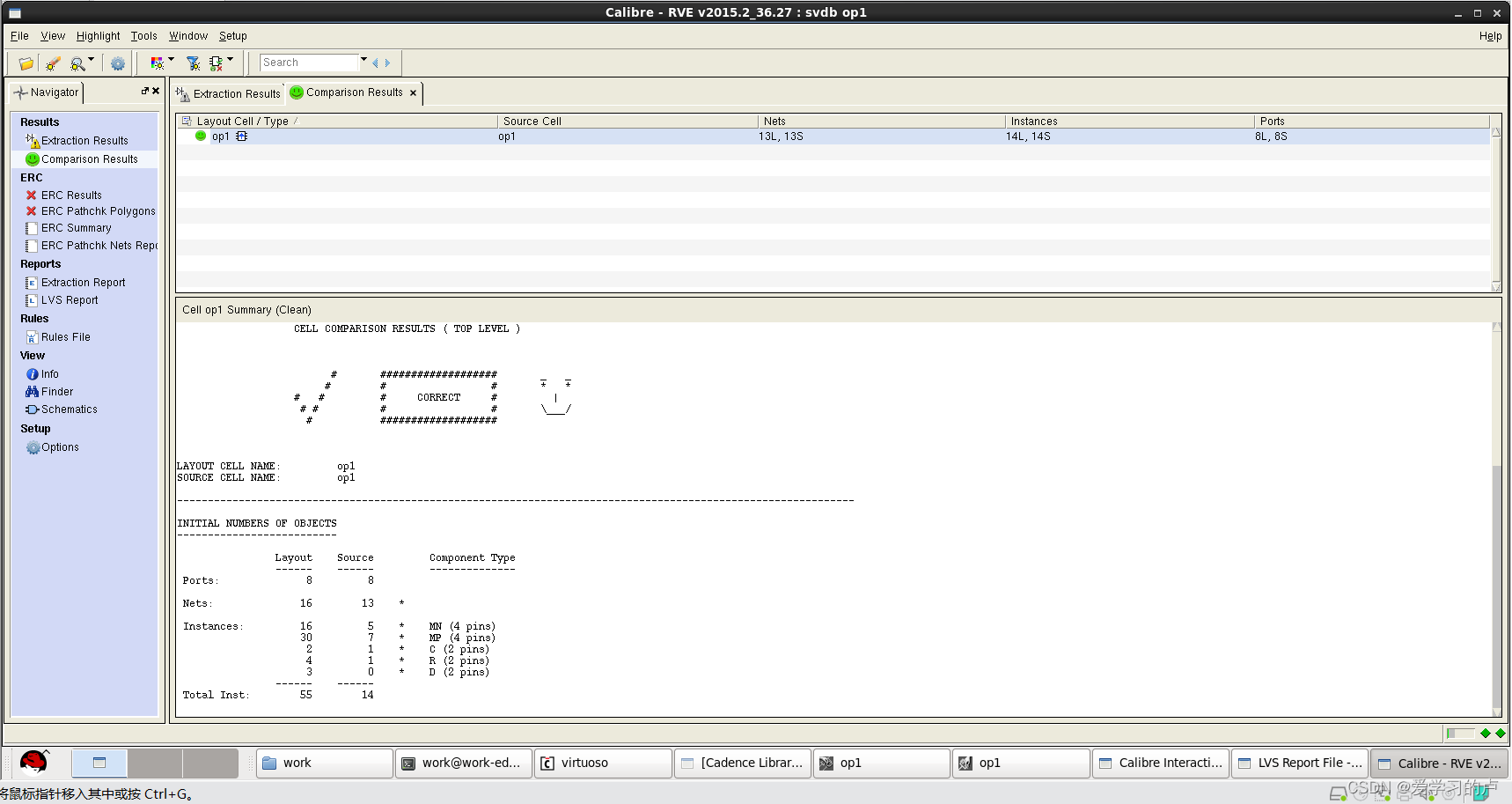

LVS:出现笑脸 到此差分放大器电路完成绘制。(后面的话有时间我想把毕业设计也发布上来,不是为了别的哈,只是想着做一个纪念,以后可以长时间翻阅,毕业设计做的是LDO方向)

到此差分放大器电路完成绘制。(后面的话有时间我想把毕业设计也发布上来,不是为了别的哈,只是想着做一个纪念,以后可以长时间翻阅,毕业设计做的是LDO方向)

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?