数电模电基础知识

模拟电路:工作在模拟信号下的电子电路

数字电路:工作在数字信号下的电子电路

模拟信号在时间和数量上的变化都是“连续”的。

数字信号在时间和数量上的变化都是“离散”的。

迄今为止,大多数的大规模和超大规模集成电路都属于数字电路。

可编程的逻辑器件

早期生产的数字集成电路逻辑功能都是固定不变的。

要想改变它的逻辑功能,就必须改变内部各单元之间的连接,而这种连接在集成电路制作过程中已经固定下来了。

因此,允许用户自行修改内部连接的集成电路称为可编程逻辑器件。

PLD内部的电路结构可以通过写入编程数据来设置;写入PLD的编程数据还可以擦除重写;PLD的逻辑功能可以由使用者通过编程来设定。

常用的可编程逻辑器件:

CPLD:

复杂可编程逻辑器件(Complex Programmable Logic Device)

FPGA:

现场可编程门阵列(Field Programmable Gate Array)

本质差异:电路结构不同。

GPLD:基于“乘积表”的与或逻辑阵列

FPGA:基于“查找表”的CLB阵列

注:CLB是输入、输出模块和可编程模块互联总线组成的一个产品。

FPGA基础知识

FPGA是一种可编程来修改其逻辑功能的数字集成电路(芯片)

与单片机的区别?

对单片机编程并不改变其电路的内部连接结构,只要根据要求实现的功能来编写运行的程序(指令)。

HDL

HDL:指的是硬件描述语言(Hardware Description Language),用于描述数字电路结构和功能的语言。

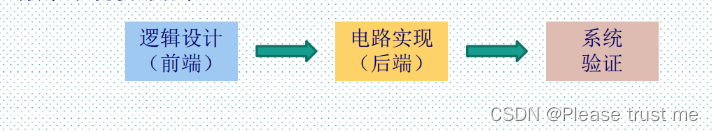

数字系统设计流程

逻辑设计(前端):HDL可以在不同的层次对数字电路的结构、功能和行为进行描述

电路实现(后端):HDL所描述的电路可以通过综合工具将其转换为门级电路网表,然后将其与某种工艺的基本元件逐一对应起来,再通过布局布线工具转换为电路布线结构。

常见的硬件描述语言:

Verilog HDL和VHDL

美国的逻辑电路设计和制造厂家大都以Verilog HDL为主,在中国很多高效和集成电路设计公司也都采用Verilog HDL。因此我们主要学习Verilog进行开发。

Verilog简介

Verilog语言最初是于1983年由Gateway Design AutoMation公司为其模拟器产品开发的硬件建模语言。

Verilog语言于1995年称为IEEE标准,称为IEEE Std 1364-1994,也就是通常所说的Verilog-95.Verilog-2001是对Verilog-95的一个重大改进版本。

原理图输入法

在FPGA设计中,还有一种原理图输入法。这种方式能够很直观的看到电路结构并快速理解。

但是随着电路设计规模的不断增加,电路原理图也越来越复杂,而对逻辑路及系统的设计时间要求却越来越短。因此这种设计方式已经不能满足实际的目前需求了。

目前Verilog设计方式已经在FPGA开发/IC设计领域占据绝对的主导地位。

Verilog与C的区别

Verilog是硬件描述语言,在编译下载到FPGA之后,会生成电路,所以Verilog是并行运行的;

C语言是软件编程语言,编译下载到单片机后,是存储器中的一组指令而单片机处理软件指令需要取指、译码、执行这个过程是串行执行的。

Verilog和C的区别也是FPGA和单片机/CPU的区别。FPGA由于全并行处理,处理速度非常快,这个是FPGA的最大优势,这一点是单片机/CPU替代不了的。

学习方法

着重理解并行特征就行

640

640

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?