【FPGA基础篇】Verilog语法基础

一、Verilog简介

1、Verilog用途

在FPGA设计里面,对于设计的方式一般有原理图设计方式和硬件描述语言编写等方式;刚开始许多工程师喜欢使用原理图设计,这种输入方式可以直观的看到电路结构并且快速理解,随着电路设计规模不断增加,逻辑电路设计也越来越复杂;原理图输入已经无法满足实际项目需求;这时Verilog就取代了原理图输入。目前,Verilog已经在FPGA开发/IC设计领域占据绝对的领导地位。

2、Verilog与VHDL

这两种语言都是用于数字电路系统设计的硬件描述语言,并且都已经是IEEE标准。两者共同点:

- 能形式化的抽象表示电路的行为和结构;

- 支持逻辑设计中的层次与范围的描述;

- 可借用高级语言的精巧结构来简化电路行为和结构;

- 支持电路描述由高层到低层的综合转换;

- 硬件描述语言和实现工艺无关。

3、Verilog与C区别

Verilog是硬件描述语言,在编译下载到FPGA后,FPGA会生成电路,Verilog全是并行处理与运行的;

C语言是软件描述语言,编译下载到单片机【CPU】之后,还是软件指令,不会根据代码程序生成对应的硬件电路,而单片机【CPU】处理软件需要取址、译码、执行,是串行执行的;FPGA的处理速度非常快,这也是其优势。

二、Verilog基础知识

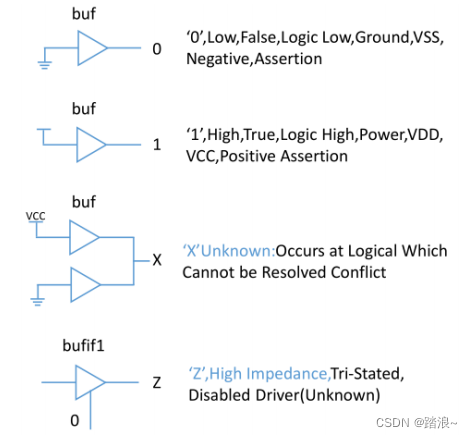

1、Verilog的逻辑值

- 逻辑0:表示低电平,对应电路【GND】;

- 逻辑1:表示高电平,对应电路【VCC】;

- 逻辑X:表示未知,可能是高电平,也或者是低电平;

- 逻辑Z:表示高阻态,外部没有激励信号,是一个悬空状态。

标识符:用于定义模块名,端口名和信号名等;可以是任意一组字母、数字、$和【下划线】的符号组合,但是标识符的第一个字符必须是字母或者下划线,且区分大小写。

2、Verilog的数据类型

在Verilog语法中,主要有三大数据类型:寄存器类型、线网类型和参数类型。

1、寄存器类型

寄存器类型表示一个抽象的数据存储单元,只能在always语句和initial语句中被赋值,并且它的值从一个赋值到另一个赋值过程中被保存下来,如果该过程语句描述的时序逻辑,即always语句带有时钟信号,则该寄存器变量对应为寄存器;如果该过程语句描述的是组合逻辑,即always语句不带有时钟信号,则该寄存器对应为硬件连线。【寄存器类型的缺省值是X【未知态】】

寄存器数据类型有很多种,如 reg、integer、real 等,其中最常用的就是 reg 类型,它的使用方法如下:

//reg define

reg [31:0] delay_cnt; //延时计数器

reg key_flag ; //按键标志

2、线网类型

线网表示 Verilog 结构化元件间的物理连线。它的值由驱动元件的值决定,例如连续赋值或门的输出。如果没有驱动元件连接到线网,线网的缺省值为 z(高阻态)。线网类型同寄存器类型一样也是有很多种,如 tri 和 wire 等,其中最常用的就是 wire 类型,它的使用方法如下:

//wire define

wire data_en; //数据使能信号

wire [7:0] data ; //数据

3、参数类型

参数其实就是一个常量,常被用于定义状态机的状态、数据位宽和延迟大小等,由于它可以在编译时修改参数的值,因此它又常被用于一些参数可调的模块中,使用户在实例化模块时,可以根据需要配置参数。在定义参数时,可以一次定义多个参数,参数与参数之间需要用逗号隔开。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

653

653

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?