一、基本结构

- 实体说明(entity):描述所设计的系统的外部接口部分

- 结构体(architecture):描述系统内部的结构和行为

- 程序包(package):存放各设计模块都能共享的数据类型、常数和子程序等

- 库(library):存放已经编译的实体、结构体、包集合和配置

- 配置:从库中选取所需要的单元组成系统设计的不同版本

二、常用格式

2.1实体说明

实体(ENTITY)是VHDL设计中最基本的组成部分之一。实体用于定义电路的输入/输出引脚,但并不描述电路的具体构造和实现的功能即描述实体的外部接口情况以及实体内的类属参数等。

2.1.1实体说明格式:

entity <实体名> is

[generic(常数名 : 数据类型:设定值)] --类属参数说明,“[]”表示可省略;

port( 端口名1 : 端口方向 端口类型;

端口名2 : 端口方向 端口类型;

...

端口名n : 端口方向 端口类型 -- 最后一个没有分号

);

end [entity] <实体名>;

注:

1)参数说明主要为设计实体指定参数,如端口宽度、器件延迟时间等;

2)端口说明描述的是设计实体和外部的接口,具体说就是对端口名称、端口模式和端口数据类型进行说明。

(1)端口名称:输入输出信号的名称,在实体中必须是唯一的。

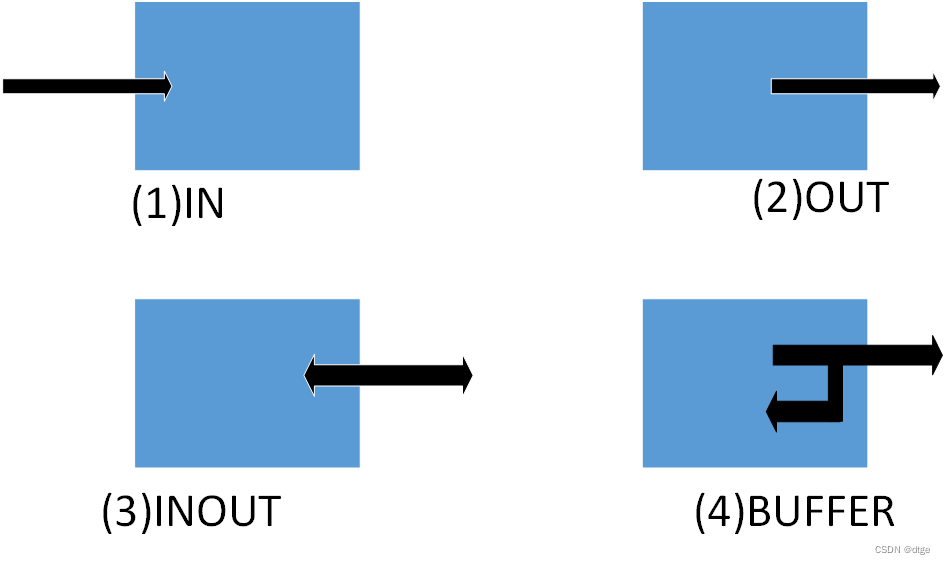

(2)端口模式:说明信号的方向,有以下几种模式:

| 端口模式 | 意义 |

|---|---|

| in | 输入信号 |

| out | 输出信号 |

| inout | 双向信号 |

| buffer | 输出信号 ,但可在内部反馈使用(缓冲) |

注: buffer是inout的子集,但作输入用时,信号不是由外部驱动,而是 从输出反馈得到。

(3)端口数据类型:端口信号的取值类

明确地指定和严格地定义端口信号的取值类型是VHDL的重要特点

VHDL中常见的数据类型有以下几种:

| 数据类型 | 简要说明 |

|---|---|

| bit | 位类型,取值0、1 ,用于逻辑运算 |

| bit_vector | 位向量类型,是BIT的组合,用于逻辑运算 |

| integer | 整数类型,可用作循环的指针或常数 |

| boolean | 布尔类型,取值FALSE(假)、TRUE(真) |

| std_logic | 工业标准的逻辑类型,取值0、1、X、Z等 |

| std_logic_vector | 工业标准的逻辑向量类型,是STD_ LOGIC的组合 |

注:std_logic和std_logic_vector是ieee的预定义数据类型,使用时必须先打开ieee库。即:library ieee; use ieee.std_logic_1164.all;

std_logic是一个9值的逻辑:

| U | 未初始化状态 |

|---|---|

| X | 不定态 |

| 0 | 逻辑0 |

| 1 | 逻辑1 |

| Z | 高阻态 |

| W | 弱不定态 |

| L | 弱0 |

| H | 弱1 |

| - | 无关态 |

2.1.2实体说明案例:

下面以RS触发器为例:

entity example is

port(set: in bit;

reset: in bit;

q,qb: buffer bit

);

end example;

注:

- 实体名要与文件名一致(使用软件时)

- 端口说明括号中最后一句没有分号“;”

2.2结构体

结构体(Architecture )描述的是实体内部的逻辑功能。在电路上相当于器件的内部电路结构。

2.2.1结构体的基本格式:

ARCHITECTURE <结构体名> OF <实体名> IS

[结构体说明部分]

BEGIN

<功能描述语句>

END [ARCHITECTURE] <结构体名>

注:

- OF后的实体名应与实体说明中的实体名一致

- 功能描述语句是结构体中的主要部分,用于描述所实现实体的功能四种不同类型的并行语句:

(1)进程语句

(2)信号赋值语句

(3)信号赋值语句

(4)元件例化语句 - 说明语句是对结构体的功能描述语句中将要用到的信号、数据类型、常数、元件、函数和过程等加以说明

2.2.2结构体的描述方式:

在VHDL中,允许设计人员采用不同的描述风格来进行设计实体中结构体的书写,结构体的描述方式通常有三种:行为描述方式、数据流描述方式和结构描述方式。

4. 行为描述方式

5. 对设计实体的数学模型的描述,其抽象程度最高。

6. 类似于高级编程语言,无需知道电路的具体结构。

7. 优点是只需描述输入与输出的行为,不关注具体的电路实现。

8. 数据流描述方式

9. 从信号到信号的数据流动的路径形式进行描述。

10. 设计人员对设计实体的功能实现要有一定的了解,有时还需对电路的具体结构有清楚的认识。

11. 优点是易于进行逻辑综合,综合效率较高。

12. 结构描述方式

13. 指在多层次的设计中,通过调用库中的元件或是已设计好的模块来完成实体功能的描述。

14. 结构描述方式只表示元件(或模块)和元件(或模块)之间的互连,就像网表一样。

15. 优点是可以将已有的设计成果用到当前的设计中去,因而大大提高设

计效率,对于可分解的大型设计,结构描述方式是首选方案。

注:也可以使用上述三种描述方式的组合来进行结构

体的描述,即混合描述方式

2.2.3结构体例子:

同样以RS触发器为例:

行为描述方式:

library ieee;

use ieee.std_logic_1164.all;

entity example is

port(set: in bit;

reset: in bit;

q,qb: buffer bit

);

end example;

architecture behave of example is

begin

process(set,reset)

variable last_state:bit;

begin

if set-'1' and reset='1' then

last_state:=last_state;

elsif set-'0' and reset='1' then

last_state:='1';

elsif set-'1' and reset='0' then

last_state:='0';

end if;

q<=last_state;

qb<=not(last_state);

end process;

end behave;

注:

- 进程语句PROCESS: PROCESS(set, reset)

- 括号中的set, reset信号称为敏感信号,是该进程的激活条件。

- 只要set和reset信号有一个发生变化,该进程中的语句就会被顺序地执行一遍。

- 进程中的语句是顺序语句,它们之间不是并行关系,执行时是按书写的先后次序顺序执行的。

- 行为描述方式描述的是与硬件电路结构无关的算法关系,所以应该按算法的流程顺序执行。

数据流描述方式:

library ieee;

use ieee.std_logic_1164.all;

entity example is

port(set: in bit;

reset: in bit;

q,qb: buffer bit

);

end example;

architecture behave of example is

begin

q <= not(qb and set);

qb <= not(q and reset);

end behave;

注:q和qb两句信号赋值语句之间是并行的关系,即只要输人set和reset发生了变化,这两个语句就会同时被执行,产生相应的输出。

结构描述方式:

library ieee;

use ieee.std_logic_1164.all;

entity example is

port(set: in bit;

reset: in bit;

q,qb: buffer bit

);

end example;

architecture behave of example is

component example

port(a: in bit;

b: in bit;

c: out bit

);

end component;

begin

u1:example port map(a=>set,b=>qb,c=>q);

u2:example port map(a => reset, b => q, c => qb);

end behave;

2.3库

VHDL的基本结构由前述的实体和结构体组成,但实际中的VHDL程序除上述两个基本部分以外通常还包括另外三个部分:库、程序包和配置。

2.3.1 库的定义

库:主要用来存放已经编译的实体、结构体、程序包等;

VHDL库中的各个设计单元(实体、结构体、程序包和配置)都可以用作其他设计的资源,一个设计可以使用多个库中的设计单元。

2.3.2库的使用格式

(1)库说明语句格式:

library <库名>;

以library 开头,后面紧跟着设计中要使用的库的名字。库说明语句使该库对于设计可见。

(2)USE子句格式:

use <库名>.<程序包名>.all;

- 库名是前面库说明语句中说明的库。

- 程序包名是设计中要使用的库中的设计单元。

- all表示使用程序包中的所有项目。

2.3.2库的例子

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

2.4程序包

程序包:主要用来存放各个设计都能共享的数据类型、子程序、常数和元件等;

在VHDL中,设计的实体说明和结构体中定义的数据类型、子程序说明、属性说明和元件说明等部分只能在该设计实体中使用,而对于其他设计实体是不可见的。为减少重复定义工作,VHDL提出了程序包的概念,用来存放能够共享的数据类型、子程序说明、属性说明和元件说明等。

2.4.1程序包的组成

(1)程序包说明部分:

主要对数据类型、子程序、常量和元件等进行说明。

PACKAGE 程序包名 IS

程序包说明语句

END 程序包名;

(2)程序包体部分:

用来规定程序包的实际功能。

PACKAGE BODY 程序包名 IS -- 程序包体

程序包体说明语句以及包体内容

END 程序包名;

2.4.2程序包案例

程序包说明

PACKAGE example IS

TYPE alu_op IS (add, sub, mul, div, eq, gt, lt);

CONSTANT pi: REAL := 3.14159265;

delay1: TIME;

COMPONENT nand2

PORT (a,b:in bit; c: out bit);

END COMPONENT;

FUNCTION mean (a,b,c: real) RETURN REAL;

END example;

程序包体

PACKAGE BODY example IS

CONSTANT delay1: TIME:= 15ns;

FUNCTION mean (a,b,c: real) RETURN real IS

BEGIN

RETURN (a + b +c )/3.0;

END mean;

END example;

2.5 配置

当对实体进行仿真时可为同一实体配置不同的结构体以比较其差别;为例化的各元件实体配置指定的结构体,从而形成一个所希望的例化元件层次构成的设计实体。

配置语句的一般格式

CONFIGURATION <配置名> OF <实体名> IS

FOR <选配结构体名>

END FOR;

END [<配置名>]

1811

1811

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?