目录

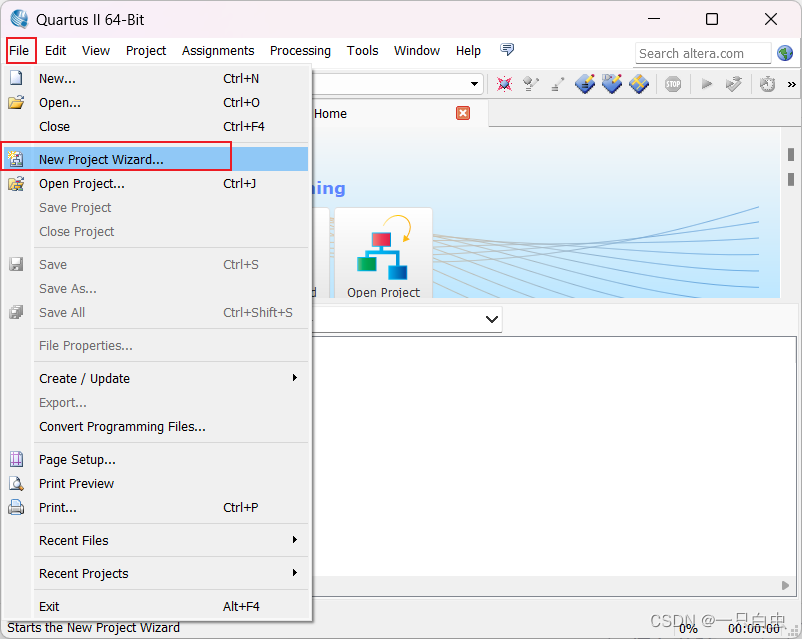

创建项目

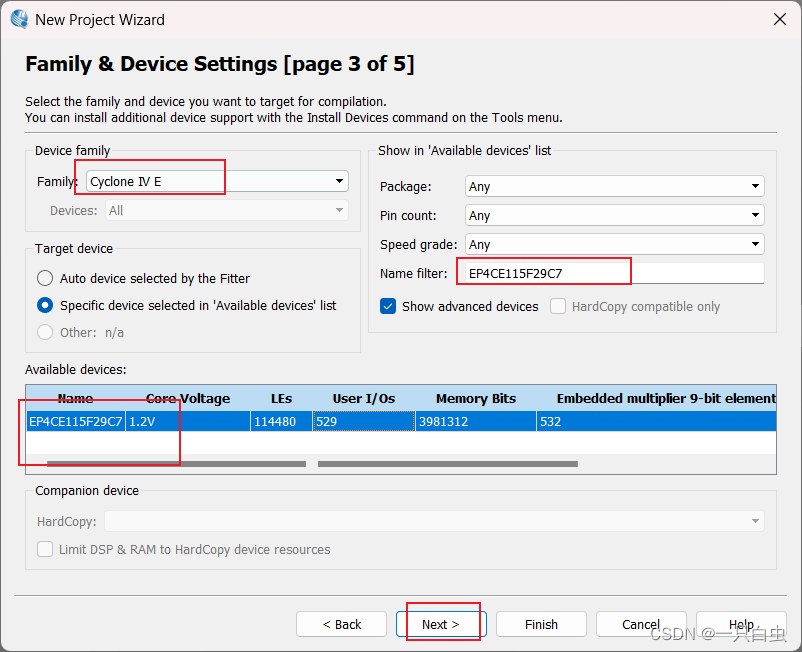

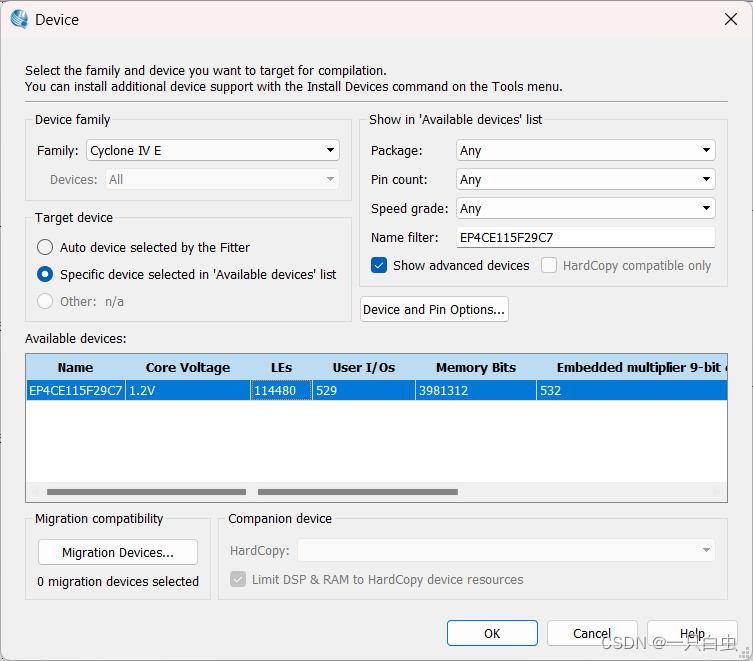

选择目标芯片:cycloneIVE系列的EP4CE115F29C7

完成半加器创建

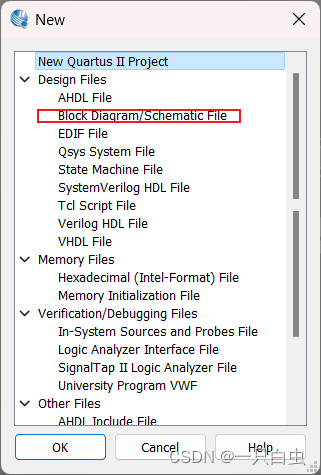

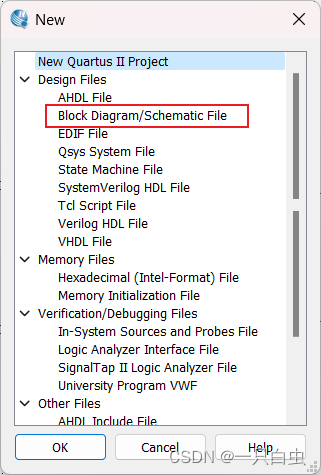

新建原理图

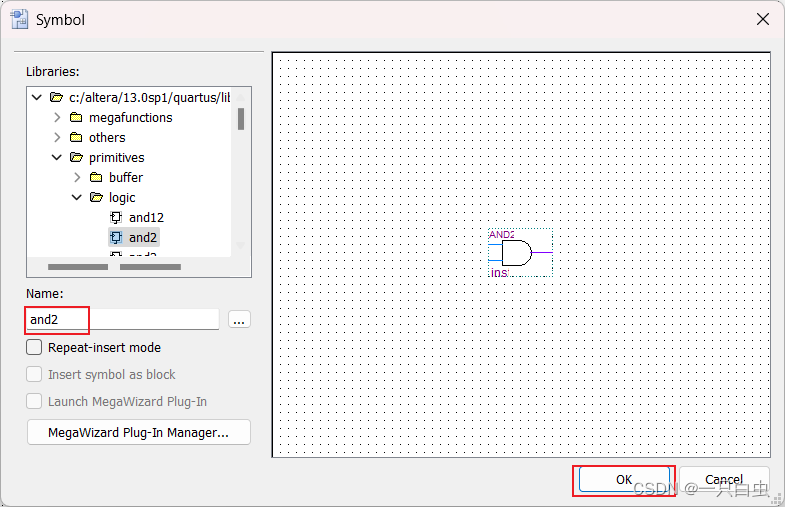

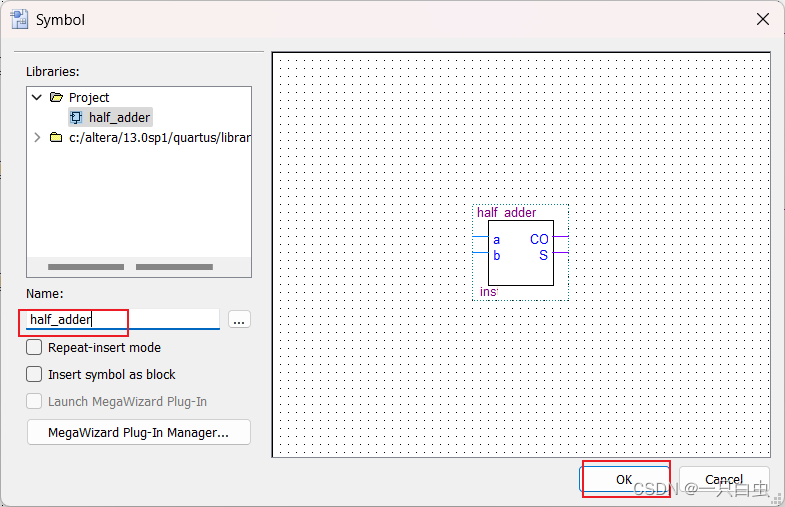

接双击原理图空白处,从“ Symbol”窗中选择需要的符号,或者直接在“name”文本框中键入元件名,添加元件

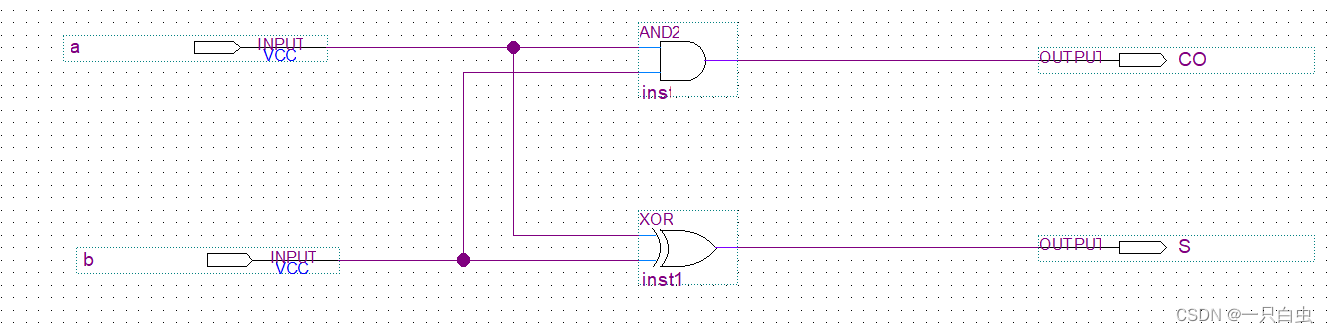

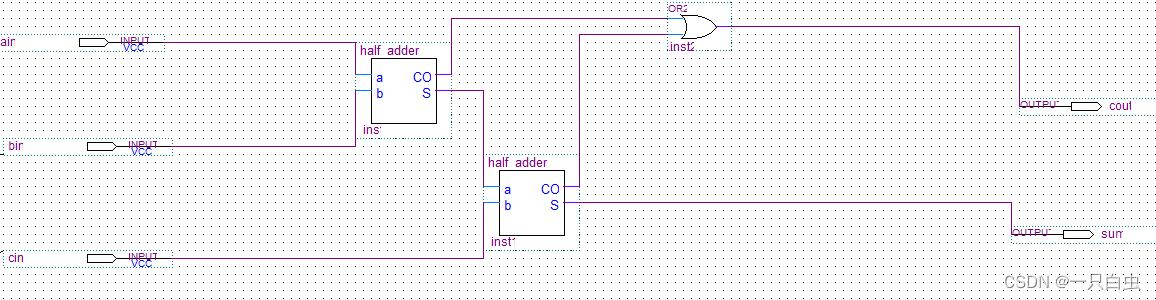

半加器原理图

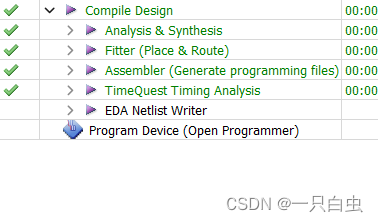

保存,编译

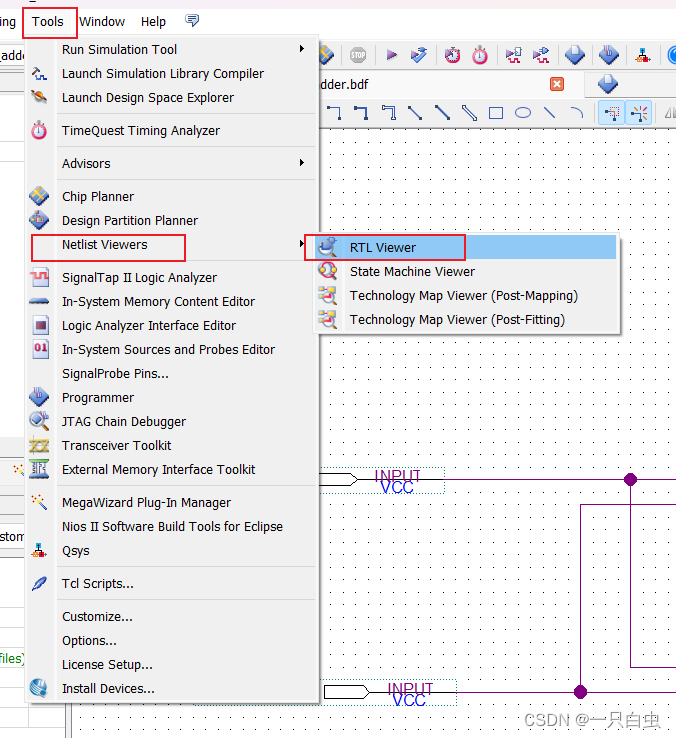

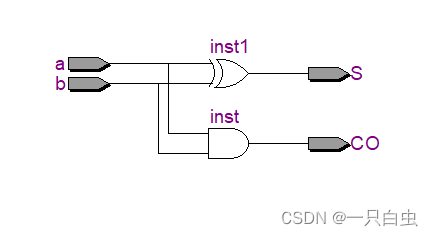

查看原理图

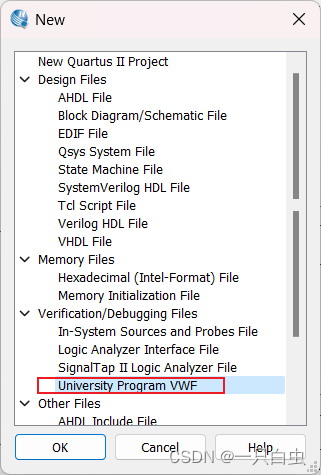

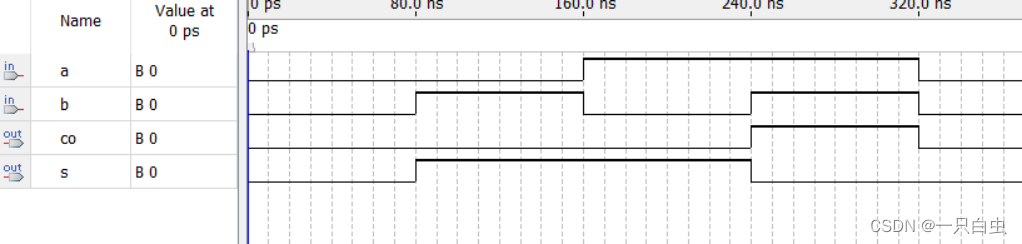

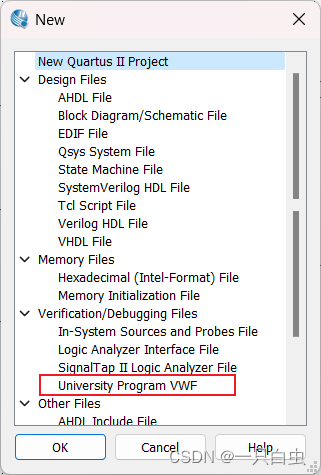

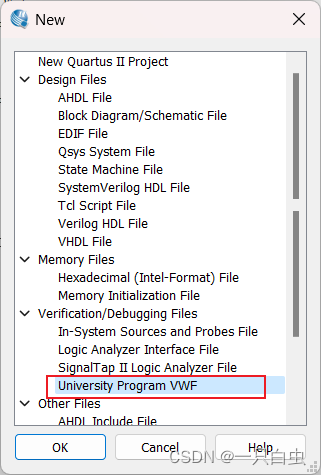

仿真

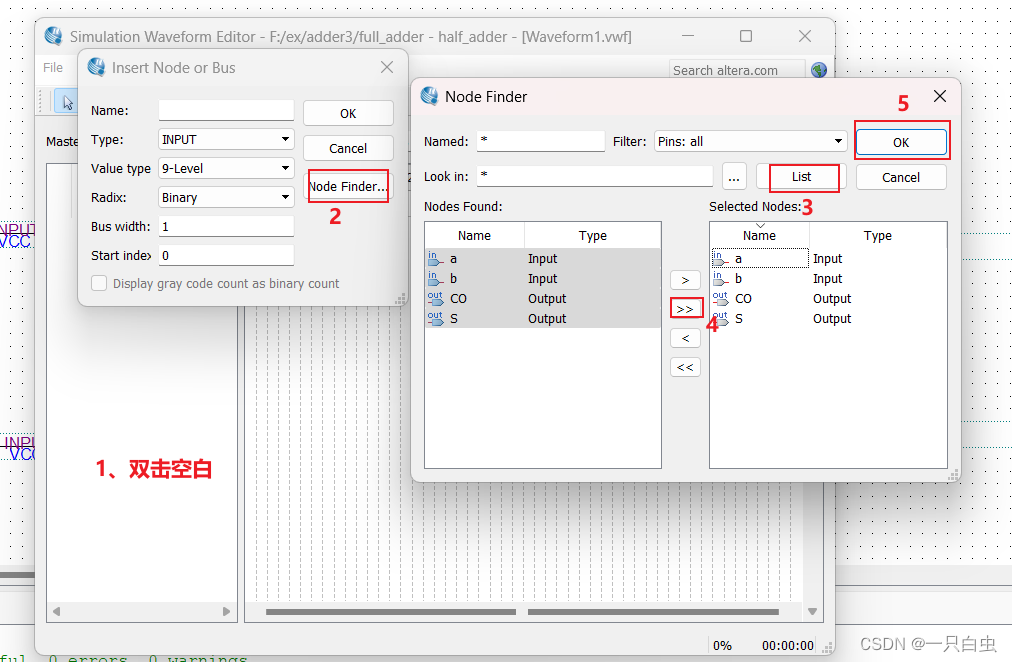

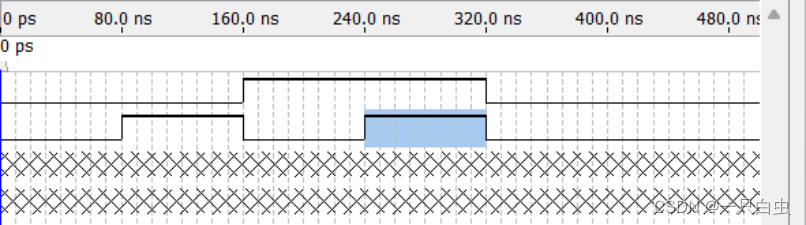

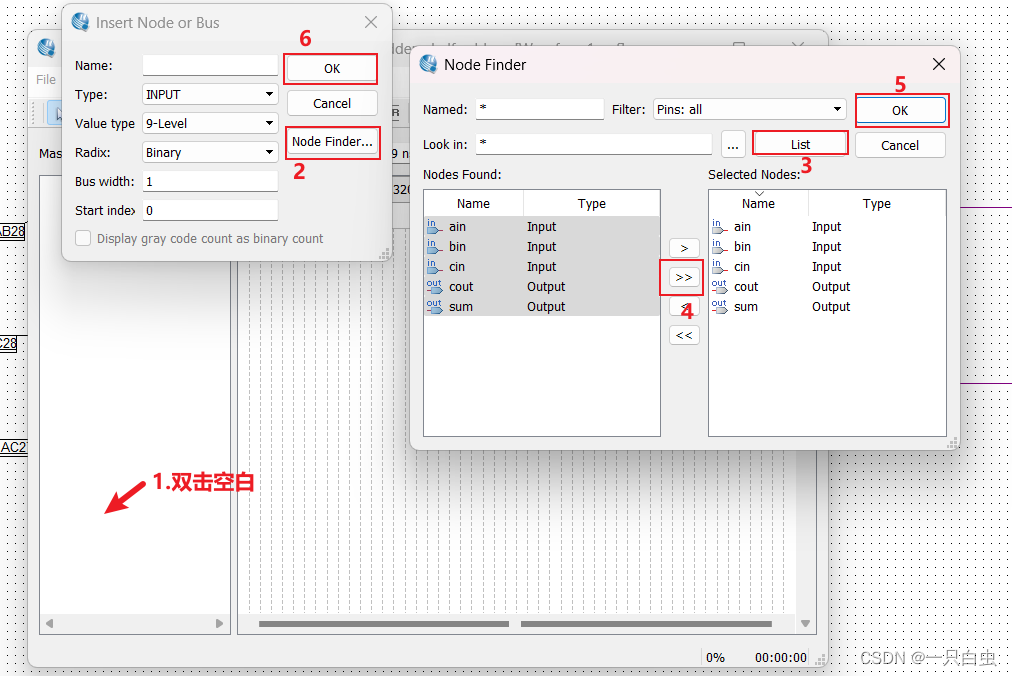

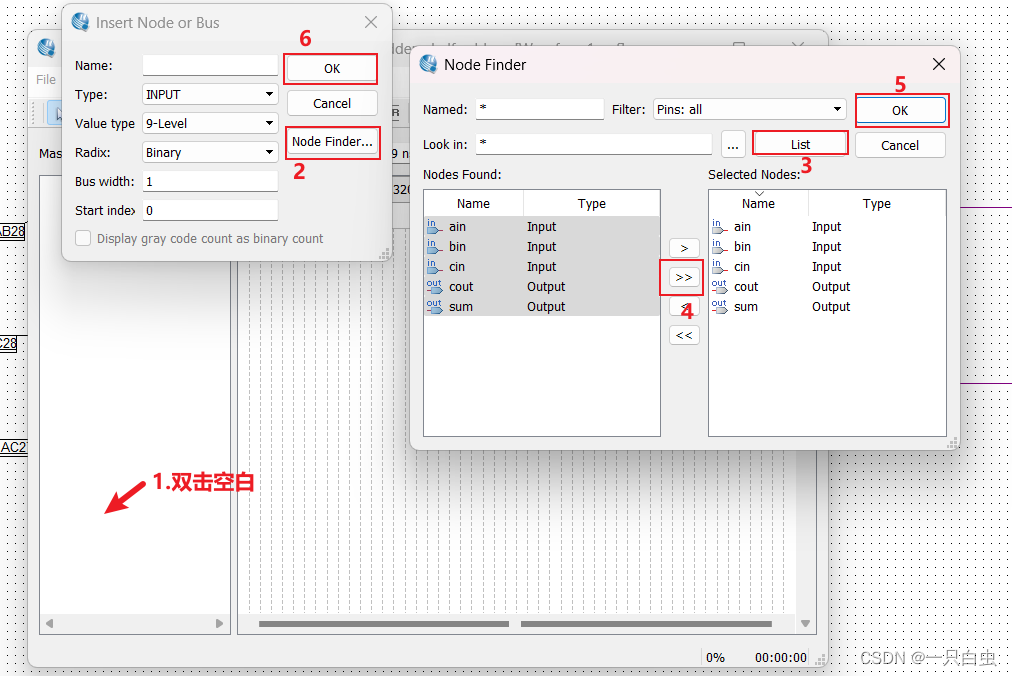

编辑信号

编辑信号

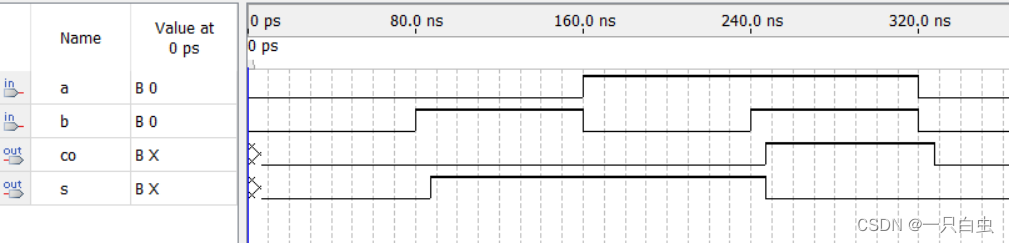

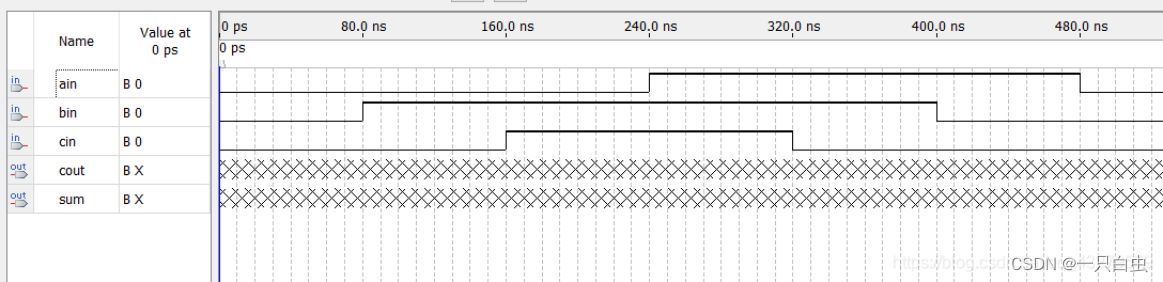

时序仿真

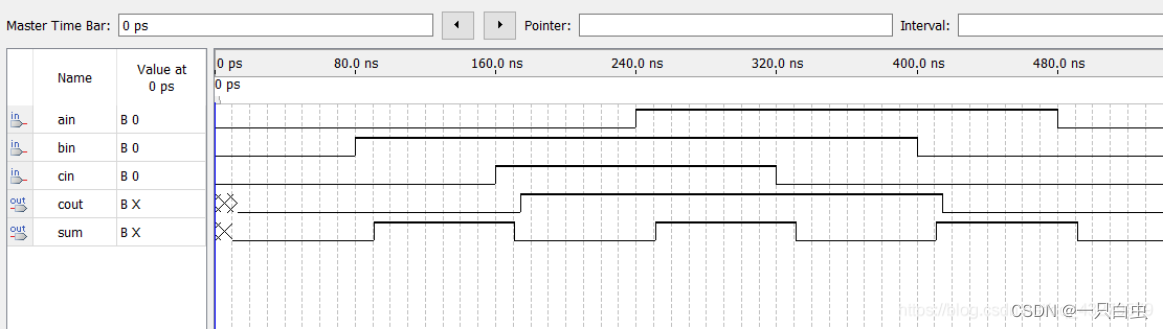

功能仿真

完成全加器创建

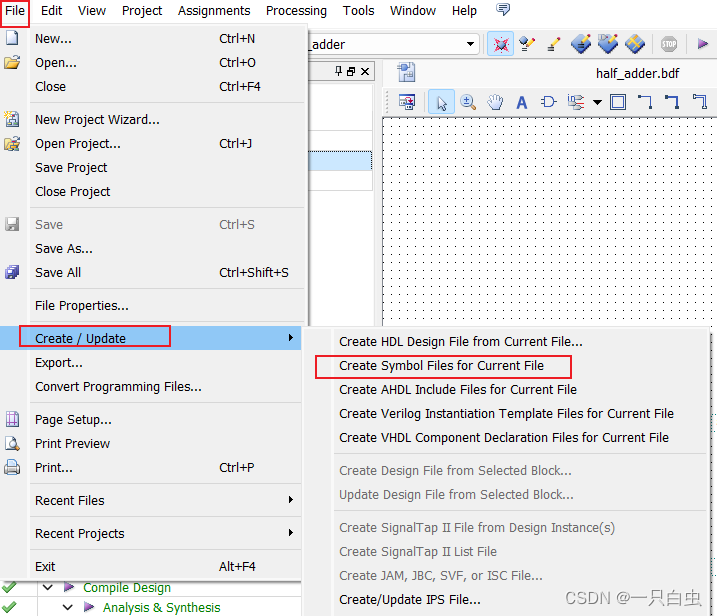

将半加器设置成可调用文件

完成全加器原理图创建

双击空白区域添加刚刚完成的半加器

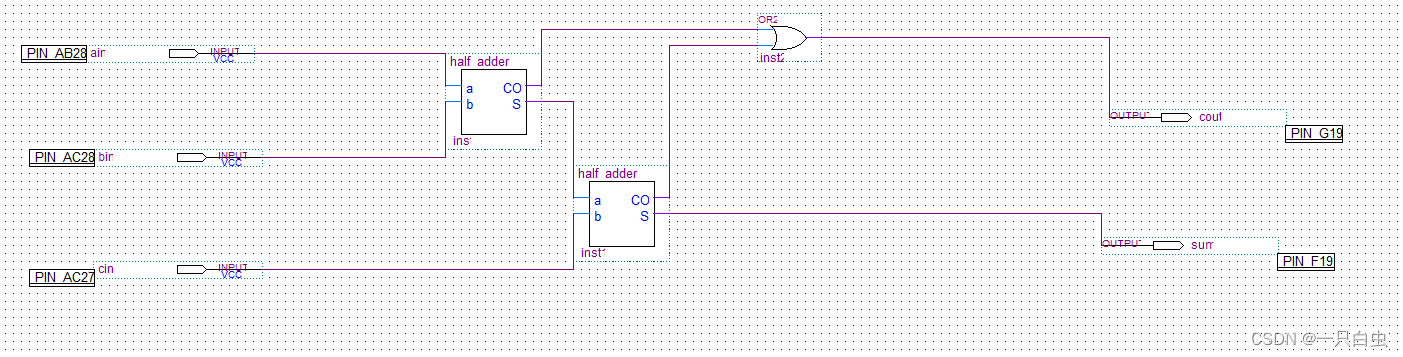

原理图

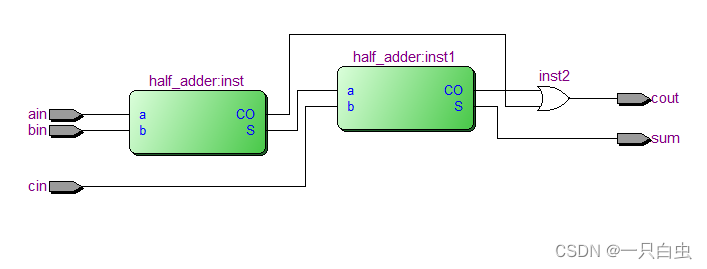

保存并编译后查看电路图

完成仿真

添加信号

编辑信号

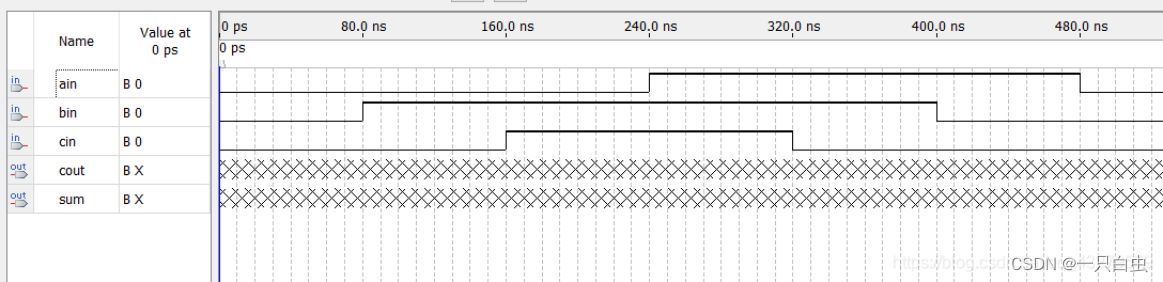

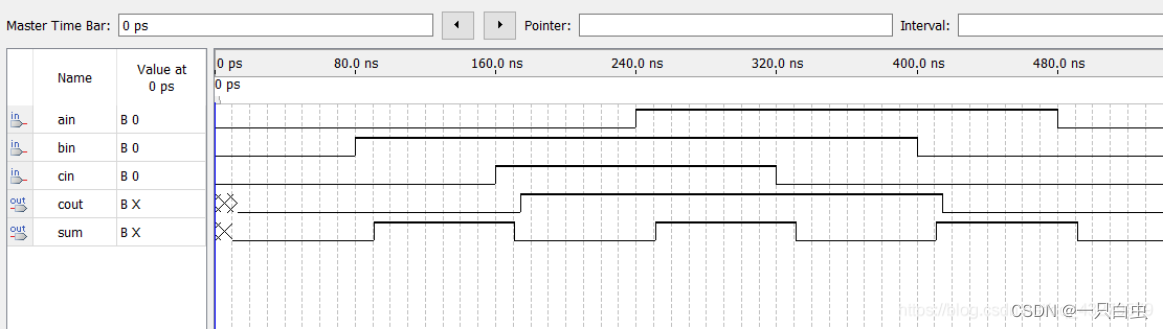

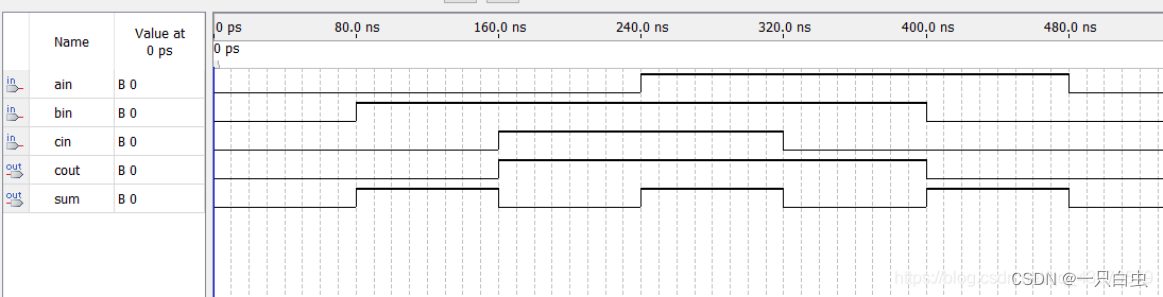

时序仿真

功能仿真

verilog实现全加器

创建文件

添加代码,保存并编译

module full_adder(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

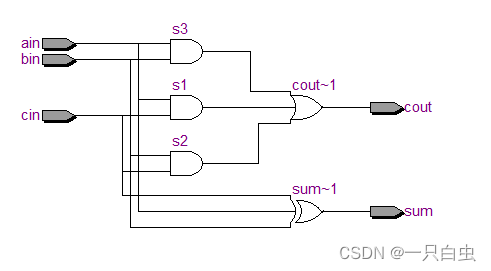

查看电路图

完成仿真

编辑信号

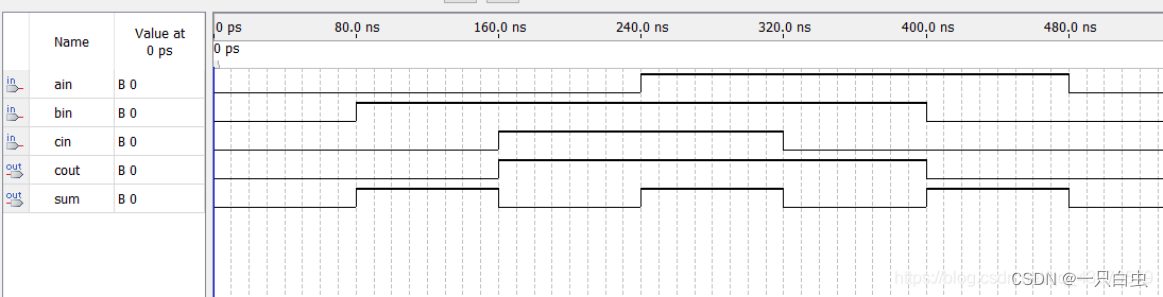

时序仿真

功能仿真

经过对比发现输出结果与真值表一致,且与原理图实现方式结果一致

下载测试

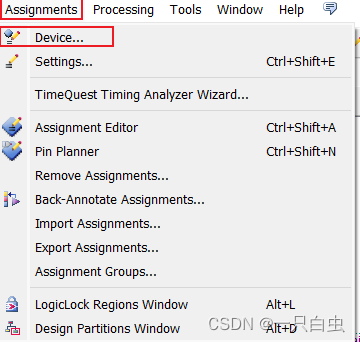

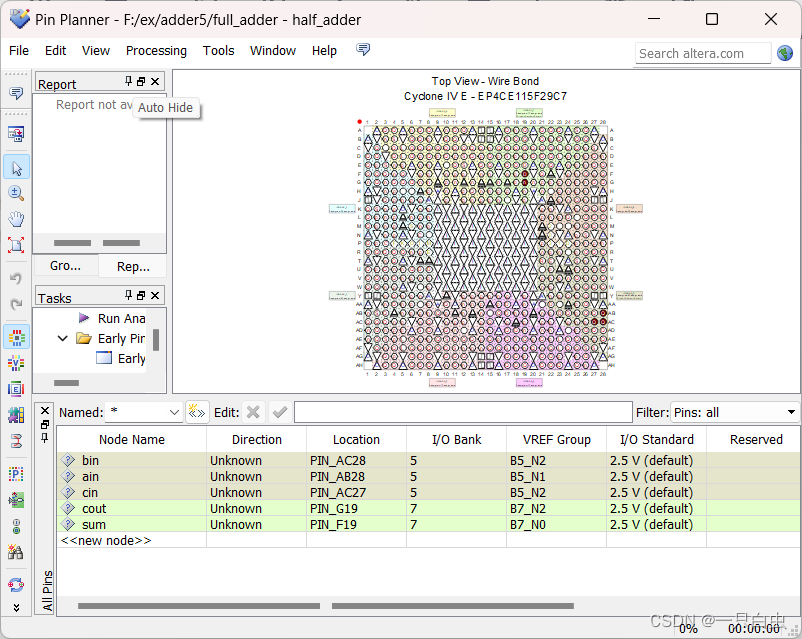

选中EP4CE115F29C7

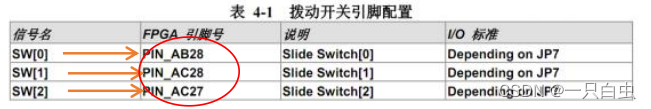

引脚图

引脚绑定

配置如下

选定了引脚之后原理图文件一定要再编译一次,才能真正把引脚绑定上。

下载测试后发现结果与理想一致

通过拨动SW,观察LED的亮灭的效果,发现SW开表示1,关表示0,LED亮表示1,灭表示0

2328

2328

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?