一、任务说明

1.主要任务

运算器实验

2.目的与意义

基本要求

- 熟悉proteus仿真系统;

- 设计并验证4位算数逻辑单元的功能。

扩展要求

- 实现ALU输入输出锁存

- 实现8位算数逻辑运算单元

思考内容

- 思考单总线,双总线和三总线结构在设计上的异同。

二、设计思路

1.电路功能分析

主要器件:74LS283、DIPSWC、RESPACK、7SEG-BCD、若干条线;

要实现4位算数逻辑功能,得需要两个四位二进制的数,因此,需要一个74LS285来实现,需要一个控制开关来实现我们数字的变化,所以需要一个控制开关DIPSWC器件,当有一个开关后,在实际生活中需要一个电阻来防止电脑过载导致短路的现象,所以需要一个RESPACK来接到电路中,当接到电路中的时候需要一个激励源来将电路带动起来,所以需要一个POWER,当输出的时候为了,可以清楚的知道我们输入的数字以及输出的结果,我们需要7SEG-BCD来实现对这个数字的显示;这里的进位位为1;这是实现加法运算的话就可以;但是,如果想要实现减法运算就不是如此简单,就需要用到反码,需要用到的器件NOT,在进行减法计算的时候,我们仍然用加法的思想来进行设计,一个数减另一个数,用计算机组成原理的思想是一个数加另一个数的补码,这样就可以实现对减法计算;当进行减法计算的时候,CO进位位为0,与加法计算器的方法不一样;前面两个计算器就是单纯的实现两个数字的加法和减法,为了实现4位算数逻辑单元的功能,研究真值表之后,我们需要用到的器件为:74LS181,控制开关DIPSWC、RESPACK、7SEG-BCD;可以从真值表中看出来当M为1时,是进行逻辑运算;当M为0时,进行算术运算(CN=1无进位,CN=0,有进位),

2.电路状态分析

加法运算器:当你按动开关的时候,你可以将两个数字转化为二进制数来进行加法运算,所以,A为一个加数,B为一个加数,在进行加法时,你需要控制开关来控制你输入的数字;然后显示在屏幕上结果,在这里进位位为1;

加法运算器:你需要输入一个减数和一个被减数,操作过程和加法一样,在这里进位位为0;

逻辑运算:你需要根据真值表来进行运算,但你进行逻辑运算的时候,你需要将M调到1,当你进行算术运算时,你就需要将M调到0;在进行算术运算的时候,你又需要分为有进位和无进位位;

三、具体实现

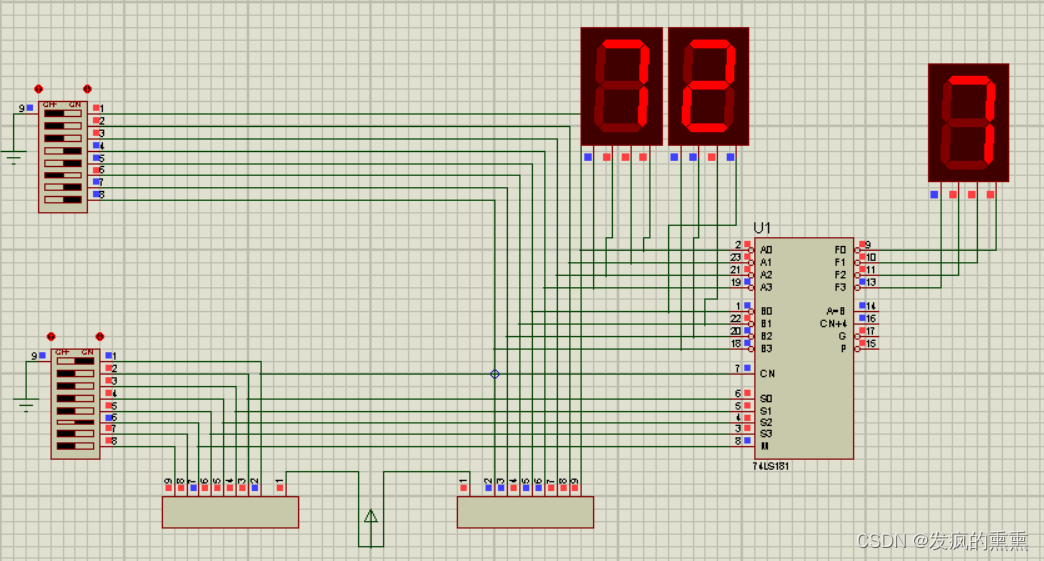

1.整体设计

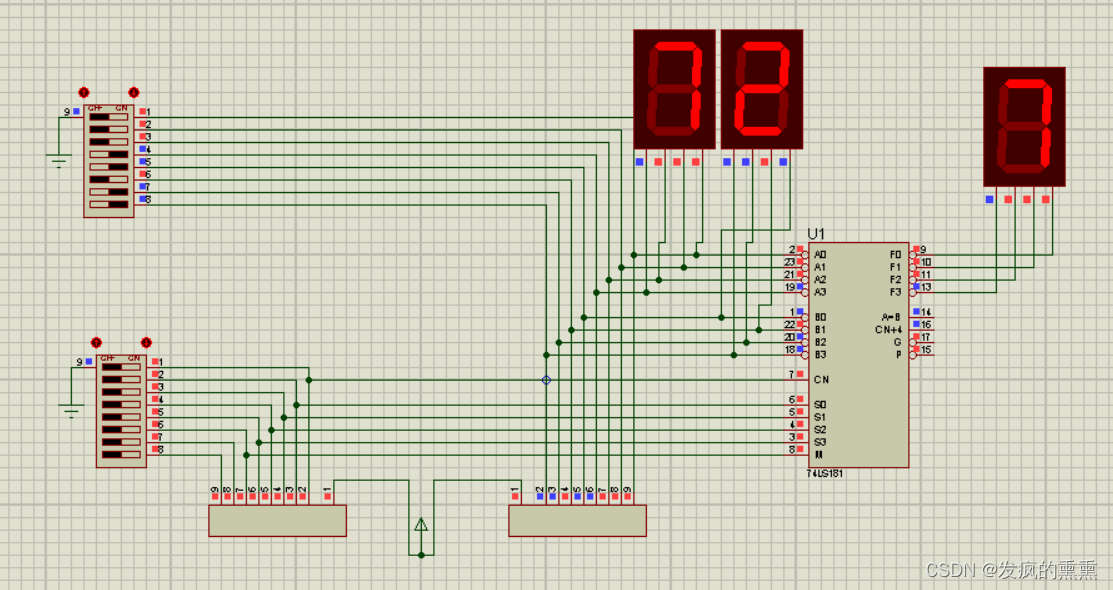

实验电路总共有三个模块:输入模块、运算模块和显示模块。输入模块主要由八个开关组成,主要以八位二进制的形式实现不同的数据输入;显示模块主要由三个数码管构成,主要负责以十六进制的形式显示两个输入的数据和一个运算输出;运算模块主要由一块74LS181N芯片组成,主要实现两个四位二进制数的算术运算和逻辑运算,并将结果输出

2.功能模块1设计及电路图

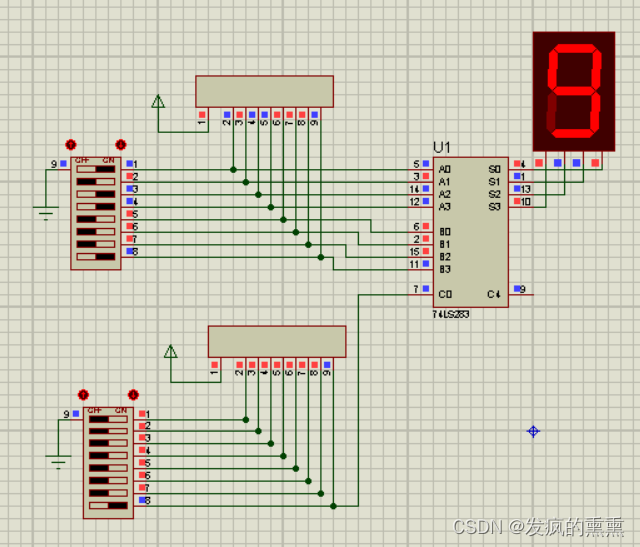

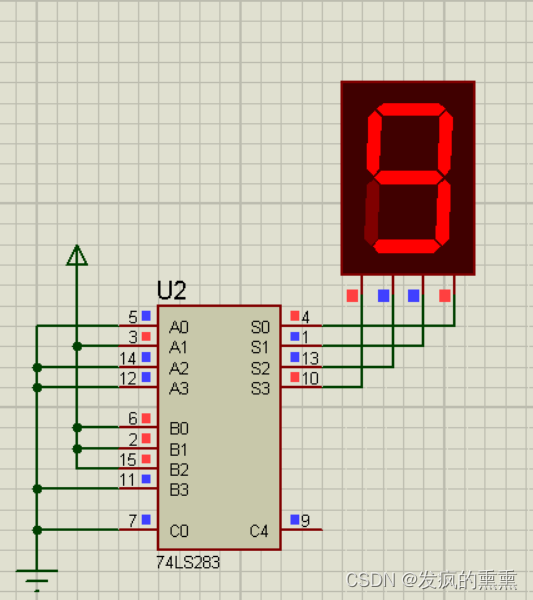

设计:加法运算器的实现

用一个74LS283芯片实现四位二进制的加法运算,C0为进位位,用一个DIPSWC来作为一个开关,分别控制8个信号,拨到OFF为关断,反之就是接通;在这个器件中9要接地,在这里用了一个RESPACK是并排电阻,1端为公共端接VCC或者地,其他接口就可以看自己的操作;通过7SEG-BCD来输出自己要验证的结果;主要器件:74LS283、DIPSWC、RESPACK、7SEG-BCD、若干条线;

电路图为:

进位位为0;

我计算的是A=0111(7),B=0010(2),最终结果为S=1001(9);

下面是自己想不靠那些复杂电路然后设计出来的,是用2+7=9;

3.功能模块2设计

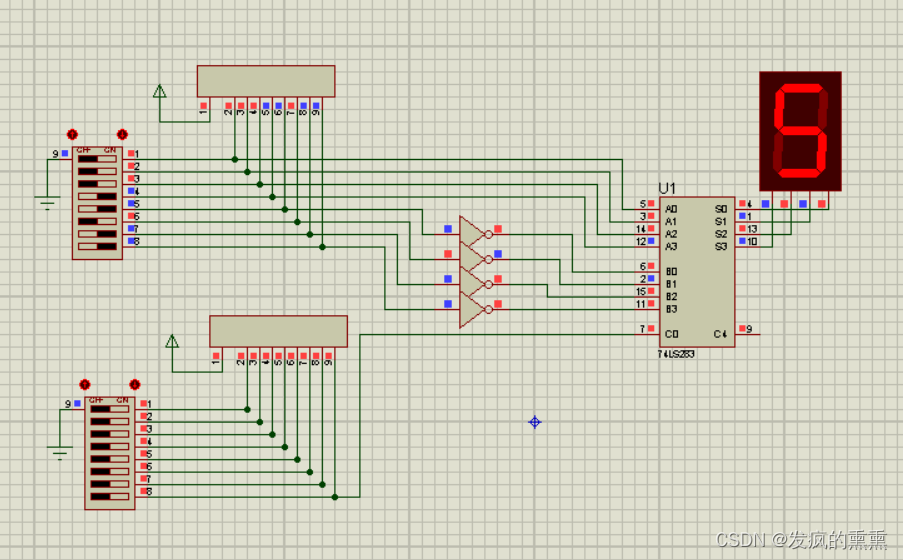

设计:减法运算器的实现

在加法运算的基础上,改变对减数的计算,在一个数减另一个数的时候,对另一个数进行补码计算,这样就可以达到对两个数的减法计算,在减法实验中,除了减数的变化,另一个变化就是进位位是与加法不一样哒,注意要把这里的开关改变,否则就会造成错误;

电路图为:

进位位为1;我计算的是A=0111(7),B=0010(2),最终结果为S=0101(5);

四、仿真测试方案设计

1.信号源设置

电源(POWER)、74LS283、DIPSWC、RESPACK、7SEG-BCD、若干条线

2.仿真测试结果

(1)加法计算器进位位为0;

我计算的是A=0111(7),B=0010(2),最终结果为S=1001(9);

(2)减法计算器进位位为1;

我计算的是A=0111(7),B=0010(2),最终结果为S=0101(5);

四位逻辑运算结果:

M=0,CN=0(有进位)时,S3S2S1S0为1111时,结果为:A

M=0,CN=1(无进位)时,S3S2S1S0为1111时,结果为:A减1;

M=1,S3S2S1S0为1111时,结果为:/A

五、设计总结

通过本次实验学会了四位二进制的逻辑运算,在实际电路中,可以增加电阻的大小来控制电流的大小,在这次实验中收获还是比较大哒,会很快运用元器件了,速度有所提高,在做第一个加法运算的时候还是有点慢,但是在做最后一个四位逻辑运算的时候,明显感觉比之前好多了;

附1.元器件及真值表

RESPACK 7SEG-BCD

DIPSWC POWER

![]()

74LS181

真值表:

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?