1.概述

本文档主要针对7 series FPGAs Transceivers Wizard IP核,为XILINX FPGA GTX收发器的使用。主要是对实际应用过程及IP核使用过程中的配置项进行了整理,结合整个研发过程,对IP核的介绍和使用做出总结。

2.硬件分配

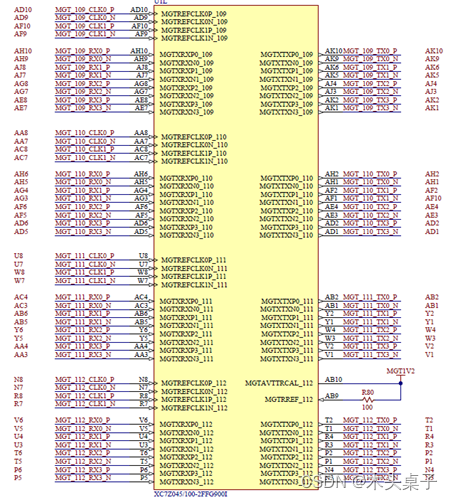

结合原理图,明确 FPGA GTX资源分配情况,以米联客XZ7Z100开发板为例。

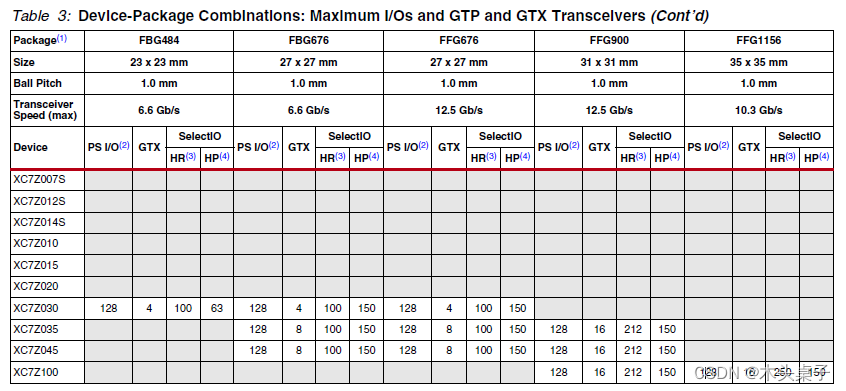

手册中关于器件GTX资源的分配见下图

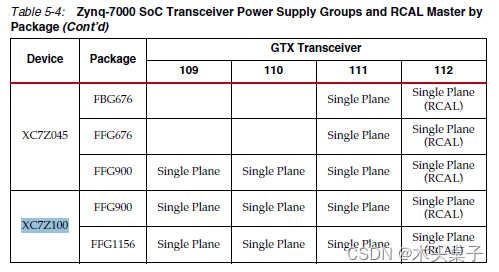

XC7Z100 FFG900封装的型号有16组GTX资源。Bank分布如下:

占用bank109-bank112。

根据原理设计各GTX资源分配如下:

Bank109----SATA1和SATA2

Bank110----光口SPFA-SPFD

Bank111、Bank112----PCIE X8

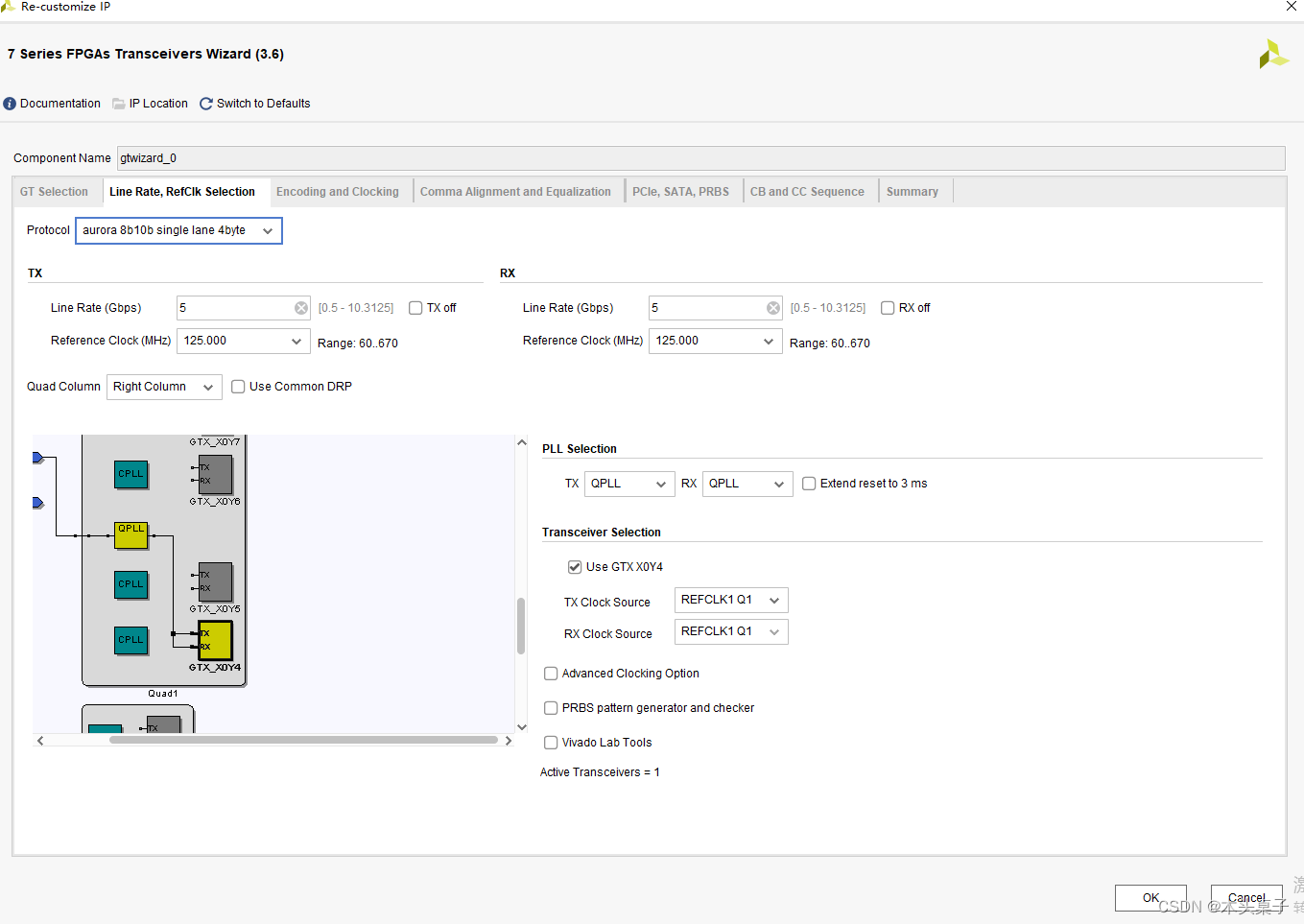

3.根据硬件配置IP核

IP手册参考pg168《7 Series FPGAs Transceivers Wizard v3.6》。

Ug476《ug476_7Series_Transceivers》

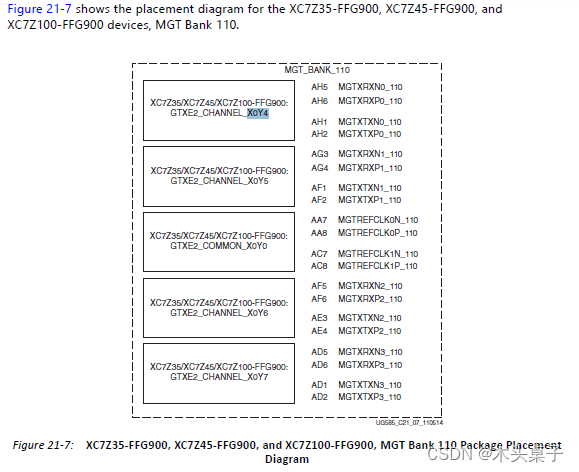

因为bank109和bank111、bank112已经具体分配为其它接口,我们使用光纤来测试bank110连通性,所以只配置bank110即可(X0Y4、X0Y5、X0Y6、X0Y7)。

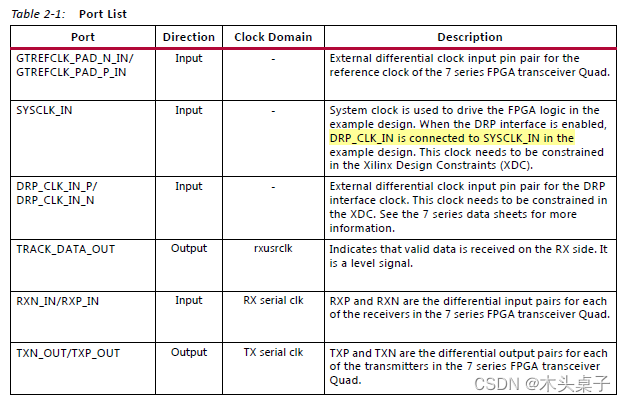

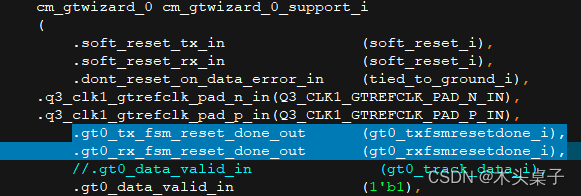

引脚描述:

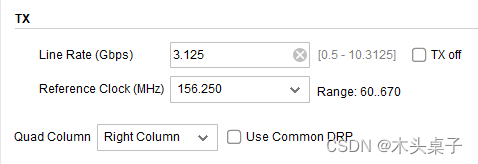

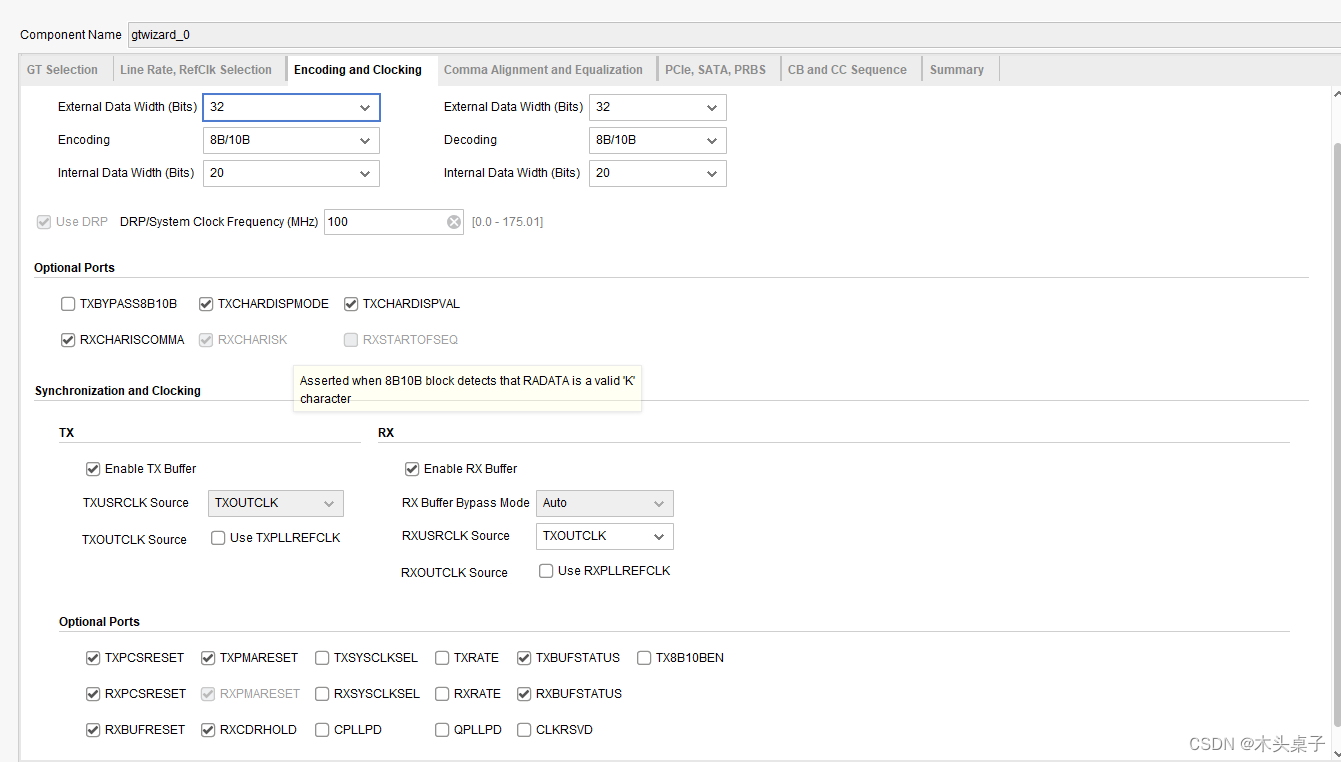

注意,在实际的example工程中DRP_CLK_IN时钟被皆在了SYSCLK_IN上,实际上IP中没有看到DRP_CLK的输入端口,但是在IP中有配置,如下图:

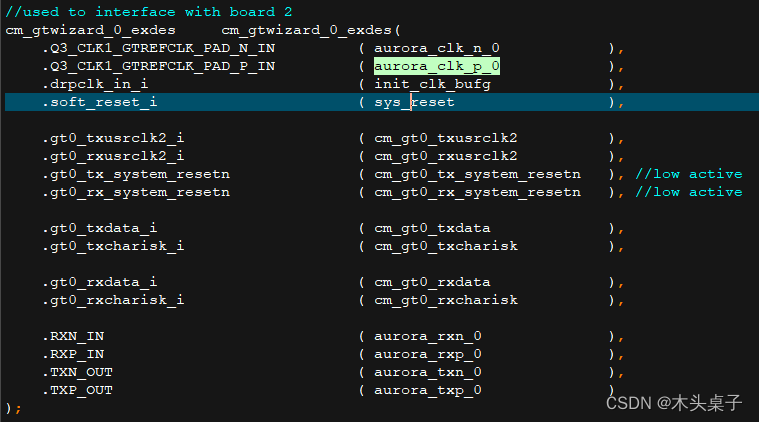

实际上使用该IP核需要引出并驱动的管脚还需要有复位信号等,所有引脚如下:

上图中,

Txusrclk2,发送端的用户时钟,

Rxusrclk2,接收端的用户时钟,

用户可以用两者分别作为发送和接收端的时钟来用

Tx_system_resetn,发送端复位信号,输出,低电平有效。

Rx_system_resetn,接收端复位信号,输出,低电平有效。

Txdata_i,(输入信号)

Rxdata_i(实际为输出信号)

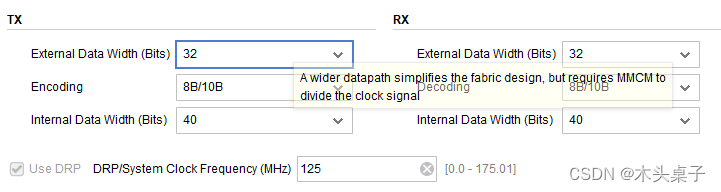

在IP核中的配置及位宽如下:

gt0_txcharisk_i,发送逗号检测

gt0_rxcharisk_i,接收逗号检测

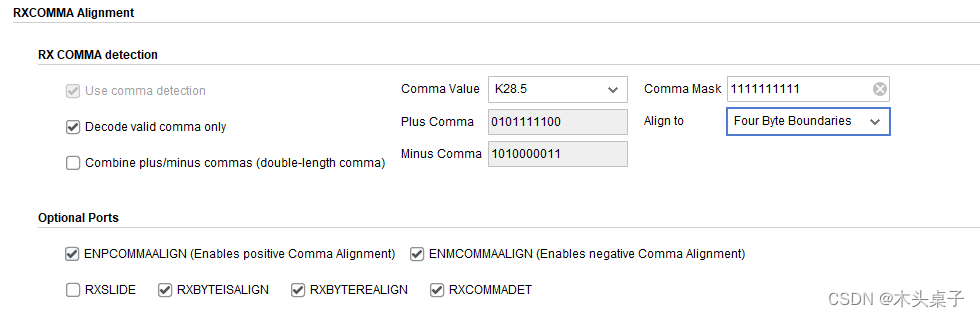

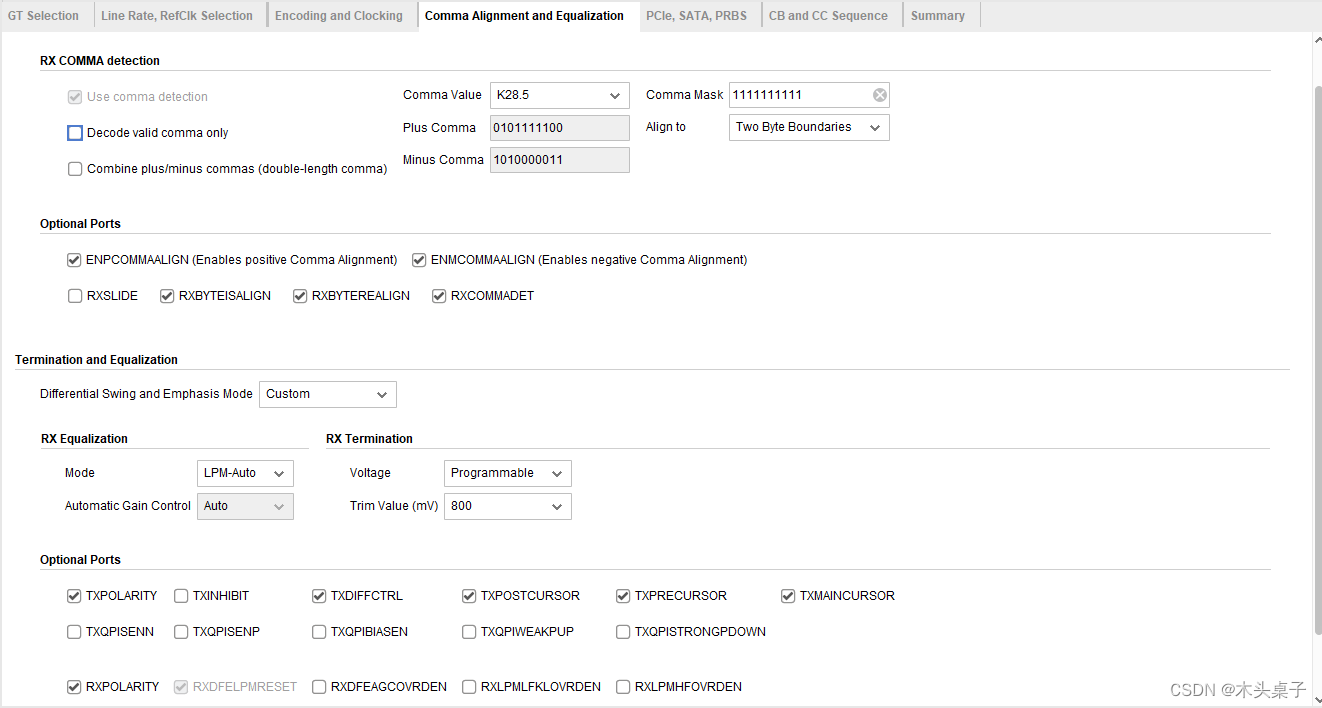

发送端和接收端与FPGA的接口除之前定义的32位数据之外还有4个1bit组成的4bit CHARISK数据。TXCHARISK端口用于指示TXDATA上的数据是K个字符(这里的K个字符即Comma Value K28.5)还是常规数据。8B/10B编码器检查接收到的TXDATA字节,以匹配任何K字符,如果对应的TXCHARISK位驱动为高,编码器就把该数据编码为逗号,否则编码器编码为普通数据。

当接收端检测到逗号码的时候,对应RXCHARISK会拉高。来辅助接收端把数据进行对齐,当勾选了IP核中的RXSLIDE,就需要手动产生RXCHARISK。

IP核配置页面

6656

6656

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?