目录

题目要求:

(1)利用6位数码管显示时钟分钟秒钟;

(2)具备启停功能;

(3)具备按键消抖功能;

(4)具备按键时间修改功能。

单单做一个时钟显示就显得十分简单,仅仅是一个进制的设计,秒钟低位满9进1,秒钟高位满5进1等等。

秒钟低位想要1秒加一下就需要一个1hz的时钟信号,通过系统时钟分频得到。

增加启停功能,有两个位置可以进行控制,一个是控制1hz时钟的产生,只要暂停了1hz信号,那么根据1hz信号进行改变的值全部都暂停了,二是在每一个时钟增加暂停动作。前者在没有时间修改或者其他操作的时候适合采用,可以使代码极其简洁,后者更适合在停止过程中有特殊要求,因为时钟没有停止,程序方便处理特殊要求。

无论是按键的启停还是时间修改都需要对按键进行消抖处理。

按键消抖程序![]() https://blog.csdn.net/m0_59487432/article/details/124872245?spm=1001.2014.3001.5502

https://blog.csdn.net/m0_59487432/article/details/124872245?spm=1001.2014.3001.5502

用两个按键进行时间的修改,一个用来选择修改哪一个时钟位,另一个用来对当前时钟位进行修改,当然用最简单的逻辑可以选择多个按键,一个按键控制一个时钟位,但是这样浪费硬件资源,这里不采纳。

时钟部分程序如下:

module watch(

input clk,

input clk_1hz,

input rstn,

input shape_stop,

input [2:0]choice,

input [3:0]amend,

output reg [3:0] clk_miaol,

output reg [3:0] clk_miaoh,

output reg [3:0] clk_fenl,

output reg [3:0] clk_fenh,

output reg [3:0] clk_shil,

output reg [3:0] clk_shih

);

reg [3:0]miaol,miaoh,fenl,fenh,shil,shih;

reg [3:0]regmiaol,regmiaoh,regfenl,regfenh,regshil,regshih;

always@(posedge clk or negedge rstn)

begin

if(!rstn)

begin

clk_miaol<=0;

clk_miaoh<=0;

clk_fenl<=0;

clk_fenh<=0;

clk_shil<=0;

clk_shih<=0;

regmiaol<=0;

regmiaoh<=0;

regfenl<=0;

regfenh<=0;

regshil<=0;

regshih<=0;

end

else if(!shape_stop)

case(choice)

0:begin clk_shih<=amend;regshih<=amend;end

1:begin clk_shil<=amend;regshil<=amend;end

2:begin clk_fenh<=amend;regfenh<=amend;end

3:begin clk_fenl<=amend;regfenl<=amend;end

4:begin clk_miaoh<=amend;regmiaoh<=amend;end

5:begin clk_miaol<=amend;regmiaol<=amend;end

endcase

else

begin

clk_miaol<=miaol;

clk_miaoh<=miaoh;

clk_fenl<=fenl;

clk_fenh<=fenh;

clk_shil<=shil;

clk_shih<=shih;

regmiaol<=miaol;

regmiaoh<=miaoh;

regfenl<=fenl;

regfenh<=fenh;

regshil<=shil;

regshih<=shih;

end

end

always@(posedge clk_1hz or negedge rstn)

begin

if(!rstn)

miaol<=0;

else if(!shape_stop)

miaol<=regmiaol;

else if(miaol<9)

miaol<=miaol+1;

else

miaol<=0;

end

always@(posedge clk_1hz or negedge rstn)

begin

if(!rstn)

miaoh<=0;

else if(!shape_stop)

miaoh<=regmiaoh;

else if(miaoh<5&&miaol==9)

miaoh<=miaoh+1;

else if(miaol==9)

miaoh<=0;

end

always@(posedge clk_1hz or negedge rstn)

begin

if(!rstn)

fenl<=0;

else if(!shape_stop)

fenl<=regfenl;

else if(fenl<9&&miaoh==5&&miaol==9)

fenl<=fenl+1;

else if(fenl==9&&miaoh==5&&miaol==9)

fenl<=0;

end

always@(posedge clk_1hz or negedge rstn)

begin

if(!rstn)

fenh<=0;

else if(!shape_stop)

fenh<=regfenh;

else if(fenh<5&&fenl==9&&miaoh==5&&miaol==9)

fenh<=fenh+1;

else if(fenh==5&&fenl==9&&miaoh==5&&miaol==9)

fenh<=0;

end

always@(posedge clk_1hz or negedge rstn)

begin

if(!rstn)

shil<=0;

else if(!shape_stop)

shil<=regshil;

else if(shih==2&&shil>=3&&fenh==5&&fenl==9&&miaoh==5&&miaol==9)

shil<=0;

else if(shil<9&&fenh==5&&fenl==9&&miaoh==5&&miaol==9)

shil<=shil+1;

else if(shil==9&&fenh==5&&fenl==9&&miaoh==5&&miaol==9)

shil<=0;

end

always@(posedge clk_1hz or negedge rstn)

begin

if(!rstn)

shih<=0;

else if(!shape_stop)

shih<=regshih;

else if(shih==2&&shil>=3&&fenh==5&&fenl==9&&miaoh==5&&miaol==9)

shih<=0;

else if(shih<2&&shil==9&&fenh==5&&fenl==9&&miaoh==5&&miaol==9)

shih<=shih+1;

end

endmodule

工程.v文件资源![]() https://download.csdn.net/download/m0_59487432/85685001?spm=1001.2014.3001.5503

https://download.csdn.net/download/m0_59487432/85685001?spm=1001.2014.3001.5503

需要帮助加QQ:2943115420

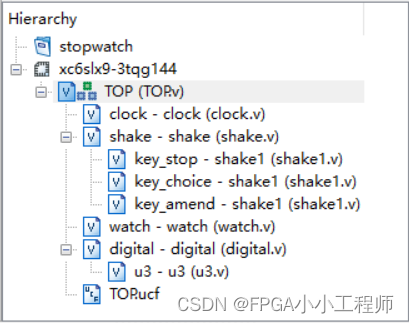

工程RTL原理图

全部模块图

4663

4663

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?