前言:结合之前的数字&模拟电路知识,了解时序逻辑电路概述,计数器,寄存器

目录

一、什么是时序逻辑电路?

组合电路:

电路的输出只与当前的输入有关,而与以前的输入无关。

结构:由门电路构成。

时序电路:

电路在某一给定时刻的输出,不仅取决于该时刻电路的输入,还取决于前一时刻电路的状态。

结构:组合电路+存储电路(触发器)。

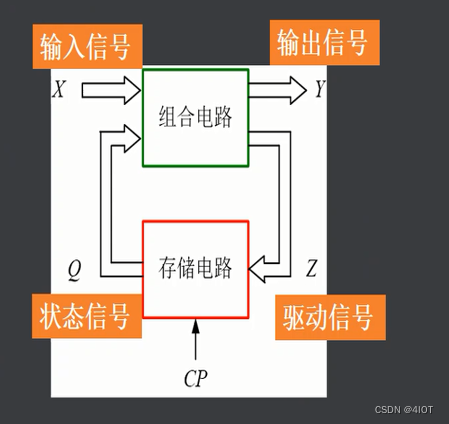

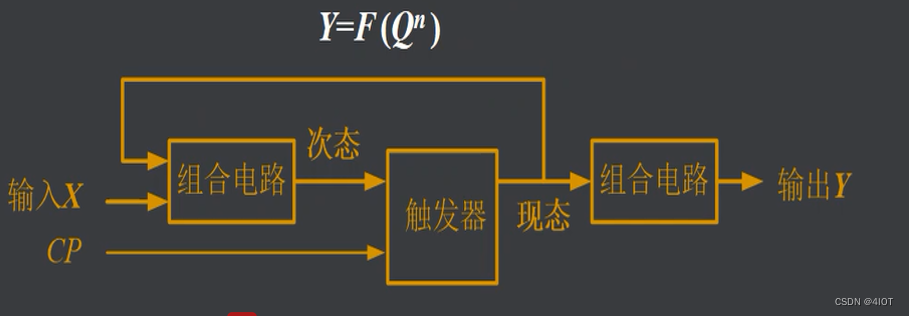

二、时序电路的模型

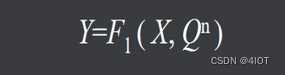

输出方程:

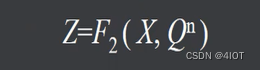

驱动方程:

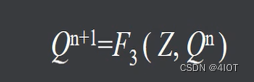

状态方程:

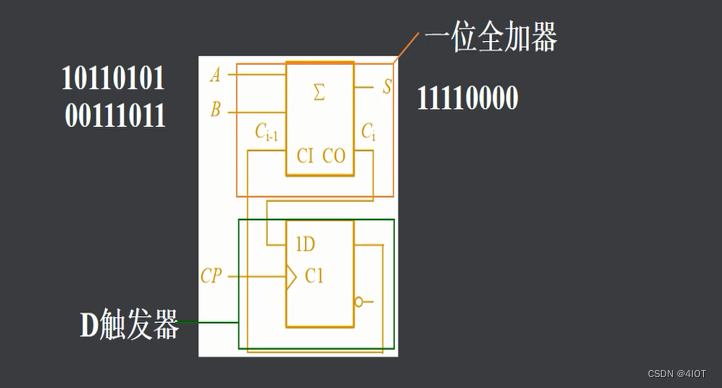

例:时序逻辑电路举例——串行加法器

上方电路是一个加法器,下方电路是D触发器,串联在一起组成了一个一位全加器。

10110101+00111011=11110000

三、时序逻辑电路的分类

1.同步时序逻辑电路和异步时序逻辑电路

同步时序电路:所有触发器由同一时钟脉冲源控制

异步时序电路:没有统一的时钟脉冲

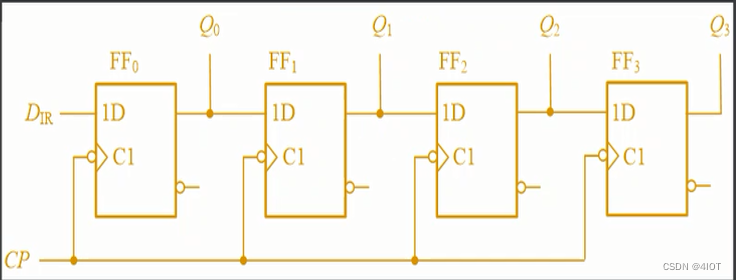

例如:SPI、UART、IIC,下图属于同步时序电路

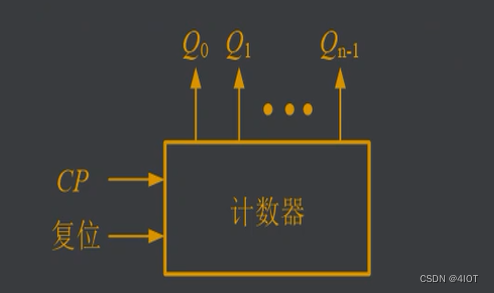

2、计数器

(1)计数器:

没有输入变量X,它仅仅在时钟控制下自动地改变状态,一般直接以触发器的状态作为输出。

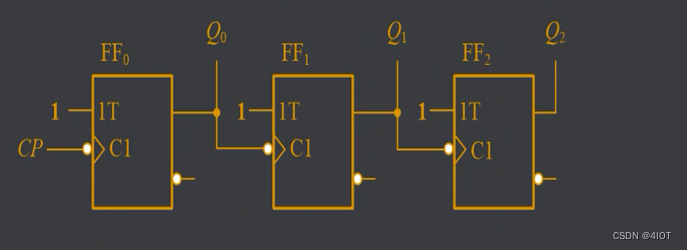

例:T反触发器

(2)计数器的分类

按计数脉冲引入方式,分为异步和同步计数器

按进位制,分为二进制、十进制和N进制计数器

按逻辑功能,分为加法、减法和可逆计数器

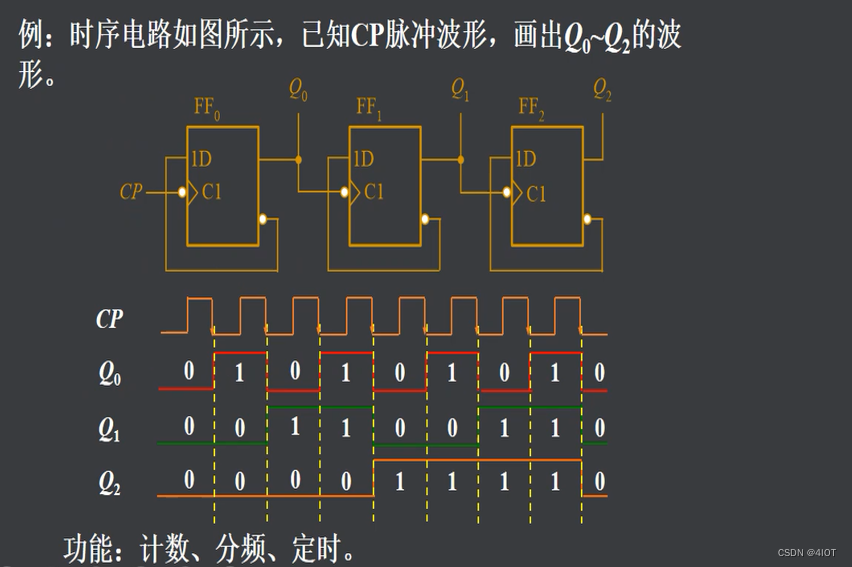

(3)计数器举例

上图案例便是T反触发器,一个脉冲实现一个反转。

分析:

CP低电平,下降沿触发,通过D触发器反转,Q0变为高电平

Q0下降沿触发,通过D触发线,又导致Q1变为高电平

Q1下降沿触发,需要等待Q0下降沿触发,带动Q1下降沿触发,带动Q2低电平变为高电平

从而实现了计数、分配、定时的功能。

(4)异步二进制加法计数器的构成规律

- 用T'触发器构成;

- 若触发器要求用上升沿触发,则应用前级Q作为下级的CP,若触发器要求用下降沿触发,则应用前级的Q反作为下级的CP。

(5)异步二进制减法计数器的构成规律

- 用T’触发器构成;

- 若触发器要求用上升沿触发,则应用前级Q作为下级的CP,若触发器要求用下降沿触发,则应用前级的Q反作为下级的CP。

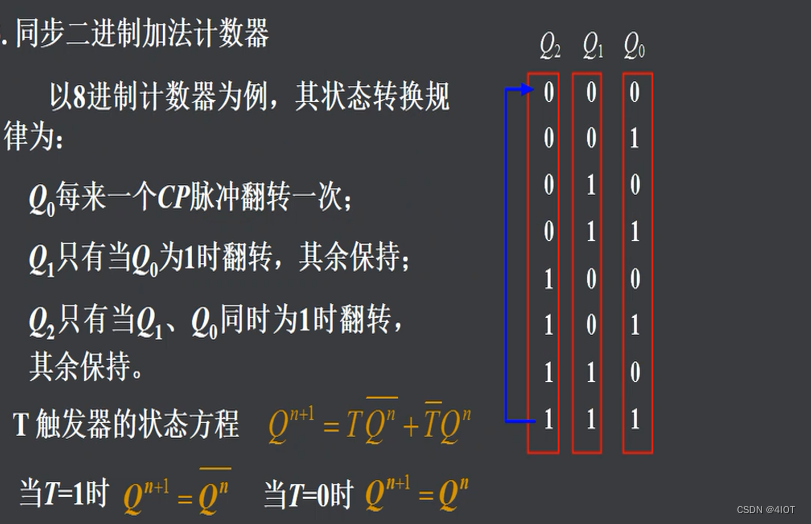

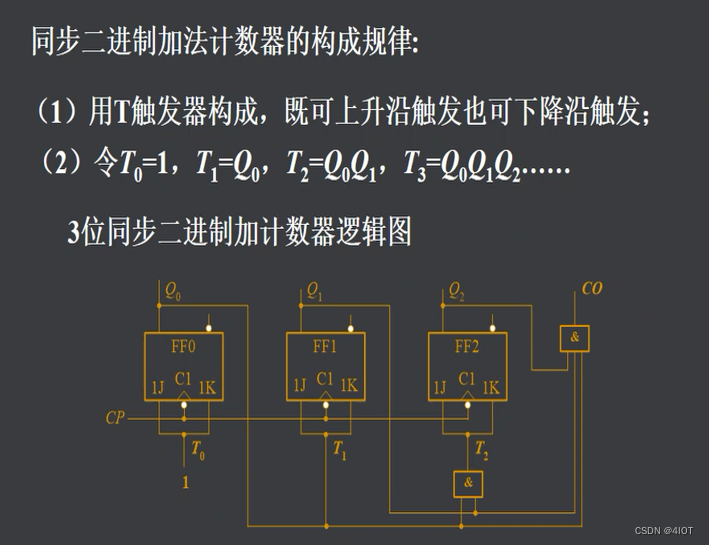

思考:如何用触发器构成3位二进制(8进制)加法计数器。

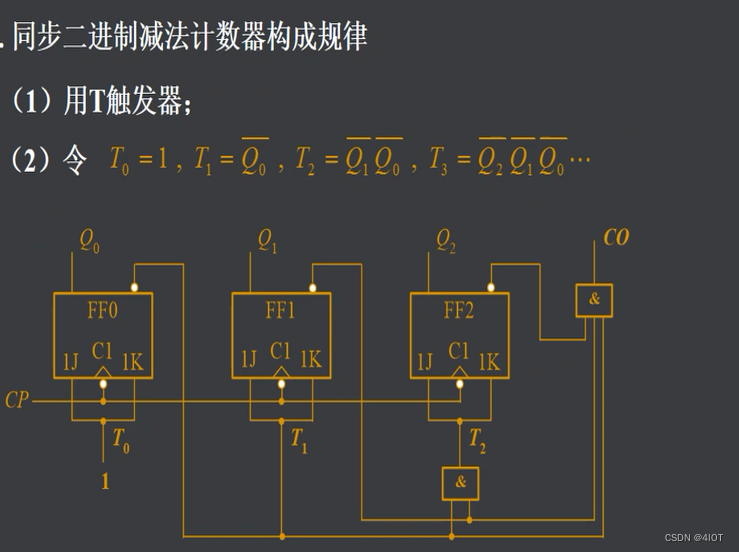

思考:如何用触发器构成3位二进制(8进制)减法计数器。

3、状态机:

除了时钟信号之外,还有输入信号X,它通过对输入信号X的响应实现状态转移。分摩尔型(Moore)状态机和米里型(Mealy)状态机两类。

摩尔型状态机:输出只和现态有关,与输入无关。如下图:

米里型状态机:输出不仅和现态有关,还和输入有关。

四、寄存器和移位寄存器

1、什么是寄存器?

寄存器用于寄存一组二值代码,广泛地用于数字系统和数字计算机中。

2、寄存器的构成

寄存器一般用D触发器构成。(透明触发器)

3、寄存器的分类

寄存器主要分并行寄存器和移位寄存器两种。

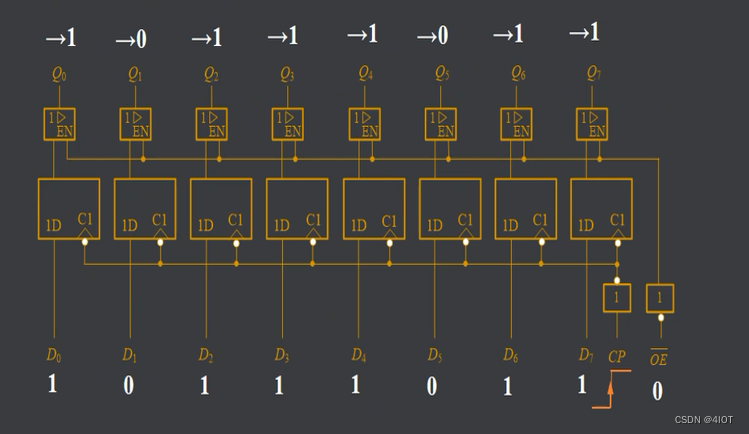

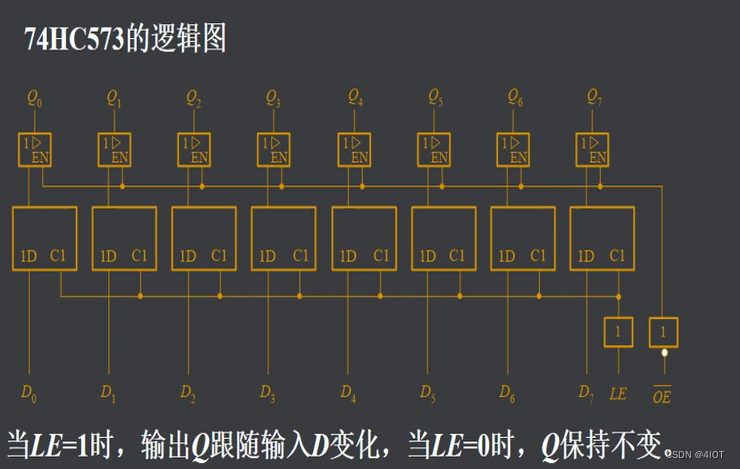

4、并行寄存器74HC574

只有CP脉冲的上升沿到来后,数据才能存入寄存器。实现了并行寄存器

思考:74HC574与并行锁存器74HC573有什么区别?

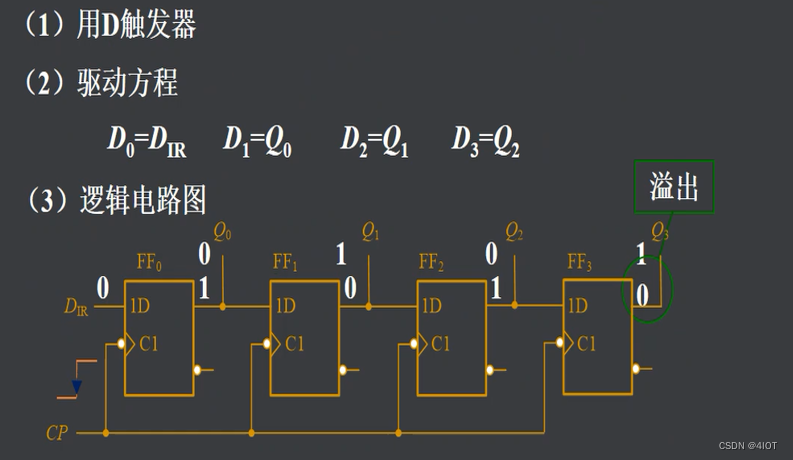

5、右移寄存器

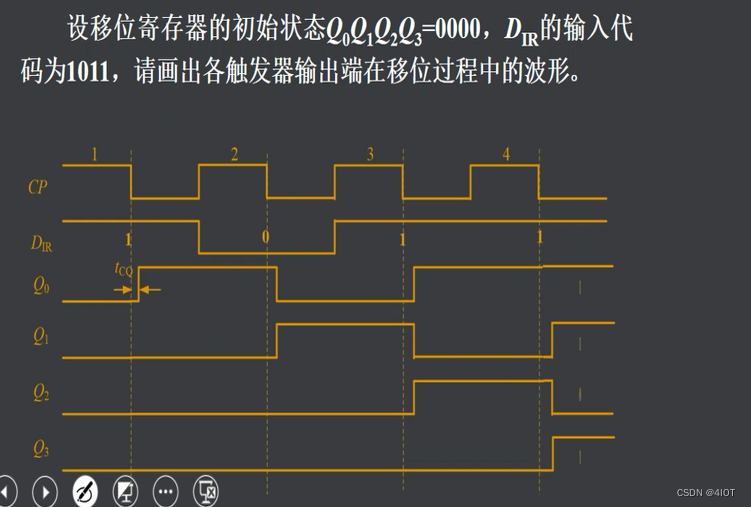

寄存器工作波形

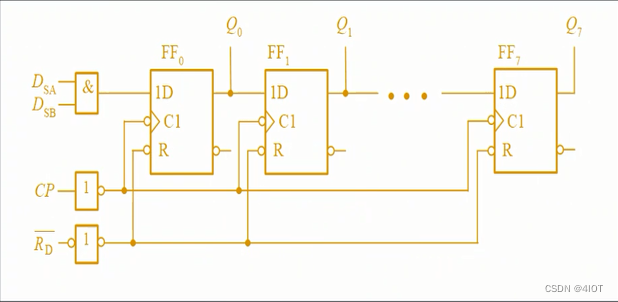

8位移位寄存器74HC164

R复位信号

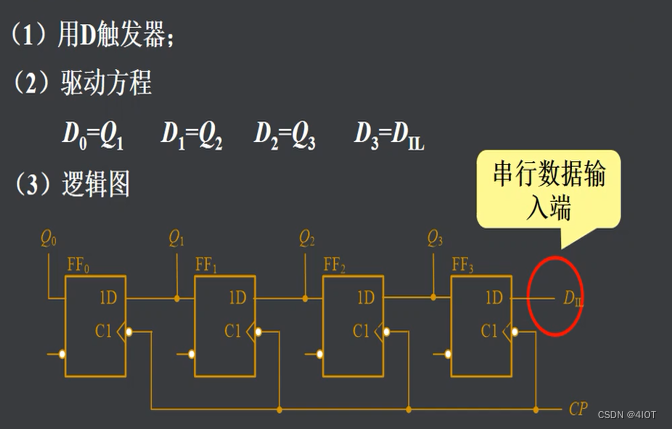

6、左移寄存器

从左往右

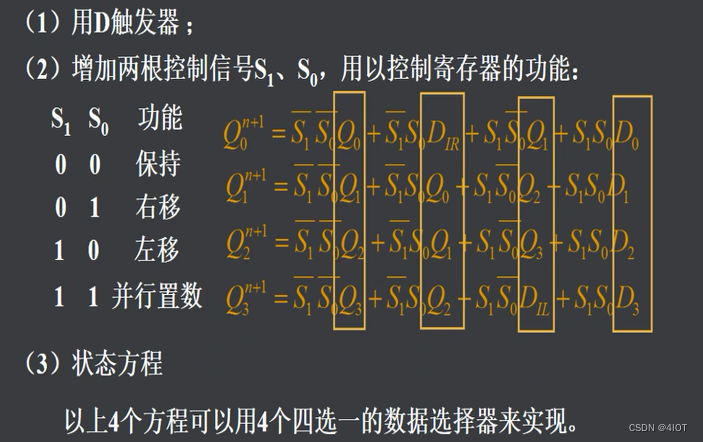

7、多功能寄存器(保持、右移、左移、并行置数)

6960

6960

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?