PCB 基本布线规范与设计原则

优秀的 PCB 设计者同时也是出色的艺术家,但是伴随 5G 的全面商用以及物联网设备的普及,电路板走线越来越精密,信号频率日益提高,电磁干扰问题日趋严重,PCB 设计人员不得不去面对一个现实问题:PCB 电路板已经开始像一个具有电阻、电容、电感的组件,而非像过去 10 年前那样仅仅作为线路连接的平台。电磁兼容性与信号完整性的问题日益突出,对于 PCB 布线与元器件布局的要求越来越高。

本文首先介绍了 PCB 制造工艺与元器件封装相关的知识,然后重点讨论了笔者工作过程当中总结的一些 PCB Layout 方面的基本布线规范与设计原则。当然,信号完整性作为一个比较系统的工程化问题,这些经验与原则并非绝对适用于任意场合,实际布线时仍然需要具体问题具体分析,结合实际的工况进行设计。而对于信号完整性方面的各类繁杂问题,将会专门新开一篇文章另行讨论。

基本术语

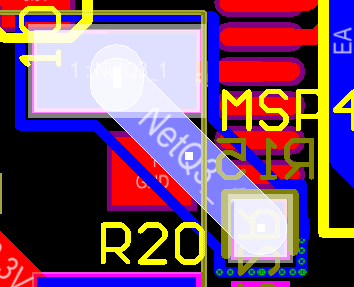

目前全球 EDA 产业格局主要由 Synopsys (新思科技)、Cadence (铿腾电子)、Mentor(明导电子) 三大企业垄断,其中 Cadence 公司的 Allegro(/əˈleɡroʊ/) 是业内比较推崇的一款高速 PCB 板级布线工具,当然面对价格不菲的商业 License,也可以选择免费又好用的 KiCad。

PCB 是印刷电路板(Printed Circuit Board)的英文缩写,其基材是由介电层(绝缘材料)和高纯度导体 (铜箔)构成,常用的 PCB 的基材主要是覆铜箔环氧玻纤布层压板,也称为FR-4 全玻纤板,使用浸润了环氧树脂的玻璃纤维布层压而成。

- 网络:电路也称为网络,即电路网络;

- 板框:放置 PCB 封装之前,需要先行在相应的图层绘制 PCB 板的边框;

- 飞线:是基于相同的原理图网络产生的,当两个封装的焊盘网络相同时就会出现飞线,表示这两个焊盘在 PCB 当中可以通过导线连接;

- 焊盘:用于将电子元件固定并且连接到 PCB ,每个焊盘都拥有独立编号,以便于和元件引脚对应;

- 泪滴:平滑过渡布线与焊盘之间的连接,提高连接的可靠性,降低信号传输时阻抗的急剧跳变,避免高频信号由于线宽突然减小而造成反射;

- 铺铜:用于保留连接地或者电源的整块铜箔区域,一块 PCB 可以分别设置并且绘制多个铺铜区;

布线

- 差分对布线:差分对是一种有效的高速信号走线方式,可以抑制共模噪声,达到更好的信号完整性;其中,等长和等距是差分布线的最基本要求;

- 蛇形等长布线:蛇形走线用于解决高速信号下,线长不相等导致的并行信号到达时间差异,进而引发信号时序的改变;其没有所谓滤波或者抗干扰的能力,因而只适用于时序匹配用途;

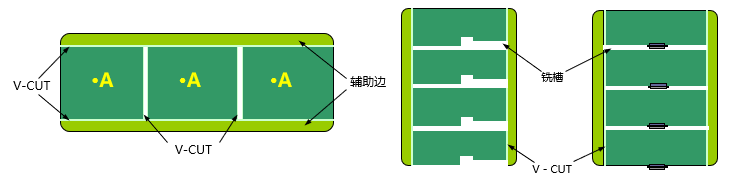

拼板

- 拼板:用于充分利用 PCB 板材,将多块相同或者不同的 PCB 设计放置到一个上面,从而提高生产效率;

- V 割:也称为

V-CUT,是指板厂按照客户的拼板要求(便于后期分板),在印刷电路板的特定位置预先使用切割机开出 V 形槽,由于 V-CUT 刀只能走直线,不能走曲线和折线,所以规则的 PCB 拼板才会采用该方式;此外,PCB 走线距离 V 割线距离不应小于0.4mm以避免损坏; - 邮票孔:一种是为了便于后期分板,在分板位置打上一些小孔,由于容易造成毛边等问题,所以仅用于拼板不规则的场合;

- 半孔:通常用于制作核心板引脚,即被精确切割为一半的过孔;

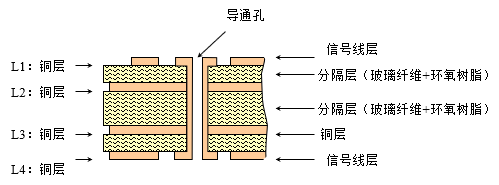

过孔

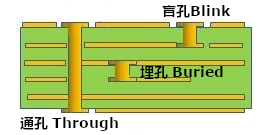

过孔(Via Hole)是镀铜的的金属小孔,用于实现不同铜层之间的电气连接,具体可以划分为如下 3 种:

- 通孔(

Through):连接顶层与底层并贯穿整个 PCB; - 盲孔(

Blind):一端位于 PCB 表面,另一端位于 PCB 中间的工作层; - 埋孔(

Buried):用于 PCB 内部中间两个工作层之间的连接;

注意:出于信号完整性的考虑,PCB 设计当中应该尽量减少过孔的使用;如果必须使用过孔,则尽量避免采用盲孔和埋孔,它们不但增加了 PCB 的加工难度,也带来了大量电气安全性方面的问题。

过孔的寄生电容

过孔本身存在着对地的寄生电容,过孔的寄生电容会延长传输信号的上升时间,例如一块厚度为 50mil 的 PCB 板材,对于直径为 20mil 内径为 10mil 的过孔,其与接地覆铜区的距离为 32mil,则该过孔的寄生电容约为 0.5pF。

虽然单个过孔的寄生电容对于信号上升沿的变缓作用不明显,但是如果在走线过程当中,多次使用过孔进行层间切换,则寄生电容的影响将会直线上升。

过孔的寄生电感

过孔在存在寄生电容的同时,也存在着寄生电感,在高速数字电路当中,过孔寄生电感所带来的危害往往大于寄生电容,多个过孔产生的串联寄生电感会削弱旁路电容的作用,从而降低整个电源系统的滤波效果。

特别是对于旁路电容,其在连接电源层与地层的时候,往往需要使用到两个过孔,这样带来的寄生电感会成倍增加,使用时需要额外注意。

阻焊

阻焊也称为焊接掩模(Solder Mask),是指 PCB 上需要覆盖阻焊油墨的部分,阻焊层通常使用负片输出,所以阻焊层形状映射到 PCB 之后,并不是为了填充阻焊油墨,而是为了暴露出铜箔。

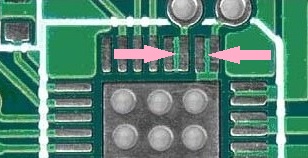

阻焊桥

阻焊桥是贴片元件之间的阻焊(两个阻焊开窗之间保留阻焊油的宽度,通常大于 6mil),主要用于防止焊盘在焊接时连锡短路。

阻焊开窗

阻焊开窗是指覆铜板不盖油墨的部分,即暴露出 PCB 表面的铜泊部分。

包地

包地是指使用接地网络将信号线包住,从而达到降低串扰的目的。

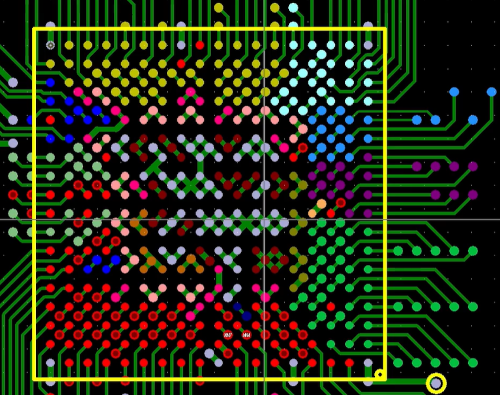

Fanout 扇出

扇出(Fanout [fænaʊt])设计是在 PCB 布局完成之后,进行布线之前的一项工作。目的是通过一段走线和过孔把原来只存在于表层的贴片元件焊盘连接至 PCB 内层,这样在后期进行内层布线的时候,就可以不用关注表层的贴片元件焊盘,而只需要对 Fanout 出来的过孔进行连接即可。

单位换算

密耳是 PCB 设计当中经常使用到的一个长度的单位,它代表千分之一英寸,通常写做 mil,其换算方式如下所示:

1 2 3 | 1 mm (毫米) ➜ 39.37 mil (密耳) 1 mil (密耳) ➜ 0.0254 mm (毫米) ➜ 25.4 μm (微米) 1 inch (英寸) ➜ 1000 mil (密耳) ➜ 25.4 mm (毫米) |

元件封装

封装(Package)描述了电子元器件的外形与尺寸,具有相同电子参数的元件可能拥有不同的封装,由于封装技术日新月异并且没有统一标准,本文总结了一些常用电子元件的封装类型。

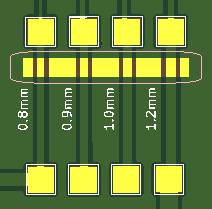

贴片元件

SMT 是表面贴装技术(Surface Mounting Technology)的英文缩写,常见的贴片元件有 0201、0402、0805、0603、1206、1210、1812、2010、2512 九种类型:

| 英制(mil) | 长(mm) | 宽(mm) | 高(mm) | 额定功率(电阻) | 最大工作电压(电阻) | 公制(mm) |

|---|---|---|---|---|---|---|

| 0201 封装 | 0.60 毫米 ± 0.05 | 0.30 毫米 ± 0.05 | 0.23 毫米 ± 0.05 | 1/20 W | 25V | 0603 |

| 0402 封装 | 1.00 毫米 ± 0.10 | 0.50 毫米 ± 0.10 | 0.30 毫米 ± 0.10 | 1/16 W | 50V | 1005 |

| 0603 封装 | 1.60 毫米 ± 0.15 | 0.80 毫米 ± 0.15 | 0.40 毫米 ± 0.10 | 1/10 W | 50V | 1608 |

| 0805 封装 | 2.00 毫米 ± 0.20 | 1.25 毫米 ± 0.15 | 0.50 毫米 ± 0.10 | 1/8 W | 150V | 2012 |

| 1206 封装 | 3.20 毫米 ± 0.20 | 1.60 毫米 ± 0.15 | 0.55 毫米 ± 0.10 | 1/4 W | 200V | 3216 |

| 1210 封装 | 3.20 毫米 ± 0.20 | 2.50 毫米 ± 0.20 | 0.55 毫米 ± 0.10 | 1/3 W | 200V | 3225 |

| 1812 封装 | 4.50 毫米 ± 0.20 | 3.20 毫米 ± 0.20 | 0.55 毫米 ± 0.10 | 1/2 W | 200V | 4832 |

| 2010 封装 | 5.00 毫米 ± 0.20 | 2.50 毫米 ± 0.20 | 0.55 毫米 ± 0.10 | 3/4 W | 200V | 5025 |

| 2512 封装 | 6.40 毫米 ± 0.20 | 3.20 毫米 ± 0.20 | 0.55 毫米 ± 0.10 | 1 W | 200V | 6432 |

芯片封装

半导体芯片的封装材料主要有塑料、陶瓷、玻璃、金属等等,如果没有特殊工艺要求,现在普遍采用的是塑料封装:

| 封装缩写 | 封装名称 | 说明 |

|---|---|---|

| SIP | Single in-line Package | 单列直插式封装 |

| DIP | Dual in-line Package | 双列直插式封装 |

| SOP | Small Out-Line Package | 小外形封装(双列) |

| QFP | Quad Flat Package | 方型扁平式封装技术 |

| QFN | Quad Flat Non-leaded Package | 四侧无引脚扁平封装 |

| COG | Chip on Glass | 芯片安装到液晶屏玻璃当中 |

| CSP | Chip Scale Package | 芯片级封装 |

| PGA | Pin Grid Array Package | 插针网格阵列封装 |

| BGA | Ball Grid Array Package | 球栅阵列封装 |

| C/PLCC | Ceramic/Plastic Leaded Chip Carrier | 陶瓷/塑料有引线芯片载体 |

布线参数

目前 PCB 板厂默认采用 1.6 毫米厚度的 FR-4 板材:

- 外层铜厚:

1oz ~ 2oz,即35um ~ 70um,默认常规电路板外层铜箔厚度为1 oz,最多可以做到2 oz(需备注); - 内层铜厚:

0.5oz,即17um,默认常规电路板内层铜箔线路厚度为0.5 oz; - 最小线宽与间隙:嘉立创

3.5mil,捷配4mil,两者约等于0.1mm,实际布线时尽量保证大于4mil即可; - 最小过孔内外径:多层板最小内径

0.2mm,最小外径为0.4mm,双面板最小内径0.3mm,最小外径0.5mm;

注意:具体参数请参考所打样 PCB 工厂的文档,例如:《嘉立创 PCB 工艺参数》、《嘉立创制造工艺要求》、《捷配 PCB 工艺能力》。

布线宽度

IPC 是美国印刷电路板协会(The Institute of Printed Circuit)的英文缩写,该组织制定了多个 PCB 设计与制造工艺相关的的规范与标准:

- 《IPC-7525 钢网设计标准》

- 《IPC-2221 PCB 设计通用标准》

- 《IPC-SM-782 表面安装设计焊盘图形标准》

- 《IPC-SM-770 印制板组件装配规范(包括表面安装和穿孔安装的设计要求)》

下面这个线宽计算公式出自于《IPC-2221 印制电路板通用设计标准》,适用于外层电流35A、内层电流17.5A、温度为100C°、宽度 400mil 的情况::

最大电流安相对环境温升摄氏度布线宽度布线厚度,其中内层布线或外层布线最大电流(安)=�×相对环境温升(摄氏度)0.44×(布线宽度×布线厚度)0.725,其中�=内层布线0.024或外层布线0.048

当前 PCB 板厂可以加工的成品外层铜厚在1oz ~ 2oz(即 35μm ~ 70μm)之间,默认外层铜箔线路厚度为 1oz(最多可以做到 2oz),内层铜箔线路厚度为 0.5oz(即 17μm)。这里以默认的 35μm 布线厚度为基准,可以得到如下常用的布线宽度、最大通过电流、阻抗:

| 布线宽度 | 最大通过电流 | 阻抗 |

|---|---|---|

| 0.1mm | 0.450486 A | 0.0982857 Ω |

| 0.2mm | 0.744609 A | 0.0491429 Ω |

| 0.3mm | 0.999067 A | 0.0327619 Ω |

| 0.4mm | 1.23077 A | 0.0245714 Ω |

| 0.5mm | 1.44689 A | 0.0196571 Ω |

| 0.6mm | 1.65136 A | 0.016381 Ω |

| 0.7mm | 1.84662 A | 0.0140408 Ω |

| 0.8mm | 2.03433 A | 0.0122857 Ω |

| 0.9mm | 2.21568 A | 0.0109206 Ω |

| 1.0mm | 2.39156 A | 0.00982857 Ω |

| 1.2mm | 2.72953 A | 0.00819048 Ω |

| 1.5mm | 3.20884 A | 0.00655238 Ω |

| 2.0mm | 3.95301 A | 0.00491429 Ω |

| 5.0mm | 7.6813 A | 0.00196571 Ω |

布线间距

安全间距是指 2 个导电子元件或者走线之间测得的最短空间距离,即在保证电气性能稳定与安全的前提下,通过空气所能够绝缘的最短距离。下面表格标注的是安全间距最小值,该数据来源于《IPC 2221 印刷电路板通用设计标准》。

| 电压 | 内层导体 | 外层导体(海拔 < 3050 米) | 外层导体(海拔 > 3050 米) | 外层导体(永久聚合物涂层) | 外层导体(保形涂层) | 外部元件引脚/端接 | 外部元件引脚/端接(保形涂层) |

|---|---|---|---|---|---|---|---|

| 0 ~ 15 V | 0.05 mm | 0.1 mm | 0.1 mm | 0.05 mm | 0.13 mm | 0.13 mm | 0.13 mm |

| 16 ~ 30 V | 0.05 mm | 0.1 mm | 0.1 mm | 0.05 mm | 0.13 mm | 0.25 mm | 0.13 mm |

| 31 ~ 50V | 0.1 mm | 0.6 mm | 0.6 mm | 0.13 mm | 0.13 mm | 0.4 mm | 0.13 mm |

| 51 ~ 100 | 0.1 mm | 0.6 mm | 1.5 mm | 0.13 mm | 0.13 mm | 0.5 mm | 0.13 mm |

| 101 ~ 150 V | 0.2 mm | 0.6 mm | 3.2 mm | 0.4 mm | 0.4 mm | 0.8 mm | 0.4 mm |

| 151 ~ 170 V | 0.2 mm | 1.25 mm | 3,2 mm | 0.4 mm | 0.4 mm | 0.8 mm | 0.4 mm |

| 171 ~ 250 V | 0.2 mm | 1.25 mm | 6.4 mm | 0.4 mm | 0.4 mm | 0.8 mm | 0.4 mm |

| 251 ~ 300 V | 0.2 mm | 1.25 mm | 12.5 mm | 0.4 mm | 0.4 mm | 0.8 mm | 0.8 mm |

| 301 ~ 500 V | 0.25 mm | 2.5 mm | 12.5 mm | 0.8 mm | 0.8 mm | 1.5 mm | 0.8 mm |

注意:目前大部分板厂所提供的布线最小间距为

4mil,即0.1mm。

最小过孔

当前 PCB 板厂可以提供的多层板最小内径为 0.2mm,最小外径为 0.4mm,双面板最小内径 0.3mm,最小外径 0.5mm。

封装尺寸

PCB 堆叠与分层

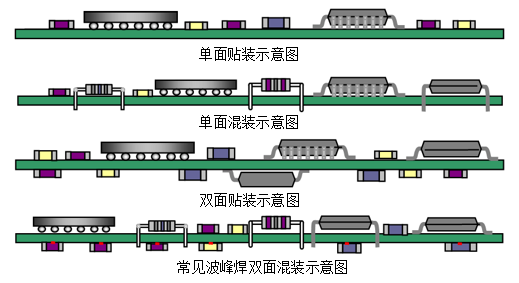

虽然 PCB 可以分为多层结构进行设计,但是通常元器件仅能在顶层或者底层,分别通过波峰焊(针对贴片元件)或者回流焊(针对分立元件)进行焊接:

根据覆铜层数的不同,可以将 PCB 具体划分为如下 3 种类型:

- 单面 PCB 板:仅有一面走线或者覆铜;

- 双面 PCB 板:顶层和底层都会进行走线或者覆铜;

- 多层 PCB 板:除了顶层和底层之外,中间还包含了

信号层、中间层、电源层、接地层,每一层之间相互绝缘并采用过孔连接;

注意:因为双面 PCB 的电磁兼容性较差,所以通常仅用于低速设计当中。

每层 PCB 之间,分别可以采用通孔、盲孔、埋孔方式进行连接。总体而言,绝大多数板级 EDA 工具软件都定义有下表当中的 PCB 功能层次:

| 名称 | 描述 |

|---|---|

| 顶层/底层 | PCB 板顶面、底面的铜箔层,用于信号走线。 |

| 内层 | 覆盖有铜箔,用于信号走线与铺铜,可以设置为信号层和内电层。 |

| 顶层/底层丝印层 | 印刷在 PCB 板上的字符层(通常为白色)。 |

| 顶层/底层锡膏层 | 也称为正片工艺时的助焊层,用于为贴片焊盘制造不锈钢网使用的层,从而决定锡膏填充区域大小以辅助焊接,不需要贴片可以忽略该层; |

| 顶层/底层阻焊层: | PCB 顶层、底层上的盖油层(通常为绿色阻焊油),其作用是阻止焊锡粘结板材;该层为负片绘制方式,当有导线或区域不需要覆盖阻焊油时进行绘制,生产出的 PCB 相应区域将不会覆盖阻焊油,该操作通常称为开窗; |

| 边框层 | 该层用于定义板框的形状、尺寸,板厂会基于该层进行 PCB 生产; |

| 顶层/底层装配层 | 元器件的简化轮廓,用于装配与维修,可以导出文档打印,不会对 PCB 板生产造成影响; |

| 机械层 | 用于记录一些 PCB 板的机械信息,生产时默认不会使用该层定义的形状进行制造,某些板厂使用源文件生产时会采用机械层作为边框,使用 Gerber 文件生产时该层仅用于标识工艺参数、V 割路径等文字信息; |

| 文档层 | 类似于机械层,但是该层仅在 EDA 工具当中可见,不会导出至 Gerber 文件当中; |

| 飞线层 | 显示 PCB 网络飞线,不属于物理意义上的层,只是为了方便颜色设置,因此某些 EDA 工具会将其放置到层管理器当中进行配置; |

| 孔层 | 类似于飞线层,不属于物理意义上的层,仅用于通孔(非金属化孔)的显示与颜色配置使用; |

| 多层 | 类似于飞线层,金属化孔的显示和颜色配置,当焊盘层属性为多层时,该层将用于连接包括内层在内的每个铜箔层; |

| 错误层 | 类似于飞线层,用于 DRC(设计规则检验)的错误标识显示与颜色配置; |

注意:信号层主要放置铜膜导线与元件,为电气信号提供传输通道;内部电源/接地层 也称为内电层,主要用来铺设电源和接地,由大块的铜膜覆盖而成,可以提升 PCB 工作的稳定性。

四层 PCB 参考设计

| 板层顺序 | 第 1 层 | 第 2 层 | 第 3 层 | 第 4 层 |

|---|---|---|---|---|

| 第 1 种情况 | 接地层 | (信号 1 + 电源) | (信号 2 + 电源) | 接地 |

| 第 2 种情况 | 信号 1 | 接地层 | 电源层 | 信号 2 |

| 第 3 种情况 | 接地层 | 信号 1 | 信号 2 | 电源层 |

- 第 1 种情况,比较理想的四层板堆叠设计,因为最外层是接地层,对于 EMI 有屏蔽作用,同时电源层与接地层可以靠得很近,使得电源内阻较小;但是,当元器件密度比较大时,不能保证接地层的完整性,信号层的信号质量会变得较差,相邻信号层之间的串扰较大;

- 第 2 种情况,这种方式较为常用,这种结构拥有较好的层电容效应,整个 PCB 的层间串扰较小,信号层可以取得较好的信号完整性;但这种结构当中,由于信号层处于表层,空间电磁辐射的强度增大,需要通过外加屏蔽壳才能够降低 EMI;

- 第 3 种情况,电源层与接地层都处于表层,信号完整性比较好,其中

信号 1层上的信号质量最好,信号 2层次之;这种设计对于 EMI 有一定的屏蔽作用;但是,由于环路较大,器件密度的大小直接决定着信号质量,相邻信号层不能避免层间干扰,整体上不如第 1 种结构,除非对于电源功率有特殊要求;

六层 PCB 参考设计

| 板层顺序 | 第 1 层 | 第 2 层 | 第 3 层 | 第 4 层 | 第 5 层 | 第 6 层 |

|---|---|---|---|---|---|---|

| 第 1 种情况 | 信号 1 | 接地层 | 信号 2 | 信号 3 | 电源层 | 信号 4 |

| 第 2 种情况 | 信号 1 | 信号 2 | 接地层 | 电源层 | 信号 3 | 信号 4 |

| 第 3 种情况 | 信号 1 | 接地层 | 信号 2 | 电源层 | 信号 3 | 信号 4 |

| 第 4 种情况 | 接地层 | 信号 1 | 电源层 | 接地层 | 信号 2 | 接地层 |

- 第 1 种情况,是常见的方式之一,

信号 1层是比较好的布线层,信号 2层次之;但是要注意信号 2与信号 3之间的层间串扰,信号 4如果没有元件,就尽量减少信号线,并且多覆盖一层接地; - 第 2 种情况,

信号 2与信号 3层的信号完整性最好,其中信号 2层为最好的布线层,信号 3层次之;电源平面的阻抗较好,层间电容较大,有利于抑制整板的 EMI;但是由于信号 1与信号 2之间存在较大的层间干扰,并且距离电源层和接地层较远,EMI 空间辐射强度较大,可能需要外加屏蔽壳; - 第 3 种情况,这种情况是六层板的最佳布局,

信号 1、信号 2、信号 3都是比较好的布线层,并且电源平面的阻抗也比较好,美中不足之处在于信号 4距离接地层过远; - 第 4 种情况,虽然性能优于前面 3 种,但是可供布线的层数仅有 2 层;

信号完整性问题

信号完整性(SI,Signal Integrity)是指 PCB 上的信号经由信号线传输以后仍然能保持完整与正确,当电路中的信号能够以正确的时序、符合要求的持续时间与电压幅度进行传送,并完整的到达输出端时,即说明该电路具有良好的信号完整性;而当信号不能正常响应时,就认为出现了信号完整性问题,特别是在高频高速电路当中。因此,信号完整性分析的目的就是为了确保信号的时序与电压幅度正确传输,电路设计当中常见的信号完整性问题主要集中在如下几个方面:

- 传输延迟(

Transmission Delay):指信号没有在规定的时间内以一定的持续时间和幅度到达接收端,通常是由于驱动过载、布线过长的传输线效应引起。此外,传输线上的电容、电感也会对信号的状态切换产生延时。高速电路设计当中,传输延迟是一个无法回避的问题,因此专门引入了一个延迟容限的概念,即确保电路正常工作的前提下,所允许的信号最大时序变化。 - 反射(

Reflection):指传输线上的回波,信号功率的一部分从源端经过传输线传递至负载,另一部分则会向源端反射。高速电路设计当中,可以将导线等效为传输线,而非集总参数电路中的导线。若阻抗匹配(源端阻抗、传输线阻抗、负载阻抗三者相等)则反射不会发生;反之,如果负载阻抗与传输线阻抗不匹配就会导致接收端向源端的信号反射。布线的几何形状、不恰当的端接方式、经过连接器的传输及电源平面不连续等因素均会导致该问题,进而导致传送信号出现严重的过冲(Overshoot)或下冲(Undershoot)现象,并最终造成信号的波形变形与时序混乱。 - 窜扰(

Crosstalk):指没有电气连接的信号线之间的感应电压与电流所导致的电磁耦合,这种耦合会造成信号线产生类似天线的作用。其中,容性耦合会引发耦合电流,感性耦合则会引发耦合电压,并伴随时钟速率的提升与 PCB 尺寸的缩小而加大,一切都是由于信号线上有交变的信号电流通过所产生的磁场,处于该磁场中的其它信号线就会感应到信号电压。PCB 的工作层的参数、信号线间距、驱动与接收端的电气特性、信号线本身的端接方式等等都会对窜扰造成一定影响。 - 接地反弹(

Ground Bounce):指由于电路中由于较大电流涌动而在电源与接地平面之间产生的大量噪声,例如大量芯片同步进行切换时,就会在与电源平面之间产生较大的瞬时电流,而芯片封装与电源之间的寄生电感、电容、电阻就会随之引发电源噪声,造成电路在零电位上产生较大的电压波动,进而影响其它元器件的正常工作。

注意:信号完整性问题往往与电磁兼容性问题相伴而生。

3W/20H/55 原则

- 3W 原则:也称为 3H 原则,保证两条走线的中心间距大于 3 倍的线宽,从而减小走线之间的串扰;当走线间的中心距离大于 3 倍线宽时,可以保持

70%的线间电场不会互相干扰;如要希望达到98%的线间电场不互相干扰,则可以使用 10W 规则; - 20H 原则:多层 PCB 的边缘会向外辐射电磁干扰,让电源平面尺寸相对地平面尺寸内缩相互间距的

20倍尺寸,让电场只在接地层范围内进行传导,从而有效抑制这种边缘辐射效应;内缩20H则可以将70%的电场限制在接地层,内缩100H则可以限制98%的电场; - 55 原则:时钟频率达到

5MHz或者脉冲信号的上升时间小于5ns,那么 PCB 必须采用多层板;有时出于成本因素的考虑采用双层板结构,这种情况下最好将 PCB 其中一层作为完整的地平面层;

PCB 布局规范

- 电源与信号要分开;

- 信号的输入与输出要分开;

- 数字部分与模拟部分要分开;

- 高频部分与低频部分要分开;

- 强电部分与弱电部分要分开。

元件布局基本原则

- 通常条件下,所有元件均应分布在 PCB 的相同面上,只有在 PCB 顶层元件过密时,才将一些高度有限并且发热量较小的贴片元件放置在底层;

- 依据【先大后小,先难后易】的布线原则,重要的单元电路、核心元器件需要首先进行布局,并且保持关键信号线最短;

- 高电压大电流信号与小电流低电压信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开,并且高频元器件的隔离要充分;

- 布局过程当中,充分参考原理框图,根据主信号流向摆放主要元器件;

- 元件的布局应当便于信号流通,并让信号尽可能保持一致的流动方向;

- 保证电气性能的前提下,元件应当放置在相互平行或者垂直排列的栅格上,以求整齐美观;

- 如果元件或导线之间存在较高的电位差,应当加大其间隔距离,避免由于放电击穿引起意外短路;

- 带有高电压的元件应当尽量布置在调试时,手不容易触及的地方;

- 位于 PCB 边缘的元件,距离边缘至少要有 2 个板厚的距离;

- 相同类型的插装元件应当同方向进行放置,同类型的有极性元件也尽量朝相同方向摆放,便于后期生产检测;

- 避免不同金属封装的元件相互接触;

- 元件之间的间隔距离需要满足操作空间的要求,例如插拔 TF 卡;

- 重量较大的元件,应当安装在靠近 PCB 支承点的位置,减小 PCB 板材受力的翘曲度;必要时还应当采取固定措施,不能仅依靠引脚焊面固定;

- 高压元器件和低压元器件之间保持较宽的电气隔离带,即不将电压等级相差较大的元器件摆放在一起,既有利于电气绝缘,也可以隔离信号提升抗干扰能力;

防止电磁干扰

- 电磁辐射较强的元件,或者对于电磁辐射较为敏感的元件,应加大相互之间的距离或者添加屏蔽罩,元件摆放的方向应当与相邻的铜泊导线交叉;

- 对于变压器、扬声器、电感等会产生磁场的元件,布局时应注意减少磁力线对于印制导线的切割,相邻元件磁场方向应相互垂直,减少彼此之间的耦合;

- 电感器件不要近距离并排摆放,避免形成互感;

- 对电磁干扰源进行屏蔽,并且保证屏蔽罩能够良好的接地;

- 对于高频电路,需要考虑元件之间的分布参数的影响;

抑制热干扰

- 发热元件优先安排在利于散热的位置,必要时可以单独设置散热片、散热风扇;

- 一些功耗大的集成块、大或中功率管、电阻等元件,要布置在容易散热的地方,并与其它元件隔开一定距离。

- PCB 双面都摆放元件时,底层一般不放置发热元件;

- 电阻、电容、晶振等热敏元件,应当尽量远离高温区域,以避免受到热干扰;

- 热敏器件尽量摆放在上风口,高元件放置在矮元件后面,并且沿风阻最小的方向放置,避免风道受阻;

- 采用大面积的接地铜箔,提升 PCB 的散热效率;

- 接地安装孔可以采用较大的焊盘,以充分利用安装螺栓和 PCB 两侧的铜箔进行散热;

电源布局

- 多采用星形拓扑结构,少采用菊花链布局,缩短电源的公共回路;

- 电源的输入与输出要分开进行布局,以避免串扰问题;

- 电源管理芯片、背光芯片、升压芯片需要放置在屏蔽壳当中;

- 电源走线要尽量避开射频区域;

高速元件与天线布局

- DDR、SDRAM、NAND Flash 等存储芯片需要靠近 CPU 进行摆放,并尽量减少线长以及交叉线的数量;

- 屏幕插座应当顺着 CPU 出线的方向,中间的 RC 滤波器尽量摆放在 CPU 一侧;

- 高速器件 CPU、液晶屏幕插座等应当远离天线模块;

- 射频模块和天线周边不要有金属元器件,以避免影响天线的频率点、阻抗等参数;

PCB 布线原则

- 高速信号的走线要尽可能短和直,走线间距要足够大,并且尽量靠近 PCB 边缘或者接插件;

- 相同信号传输线的线宽需要保持一致,拐线时同样需要保持相同的线宽;

- 重要的信号线可以增加线宽,以降低其特性阻抗;

- 关键信号线可以采用平行地线的方式进行隔离;

- 相邻的两层之间,走线采用 # 字型错开布线;

- 每条走线的宽度与元器件每个引脚的焊盘连接保持对称,并且从元件焊盘中心位置出线;

- 当和焊盘连接的走线比焊盘宽时,走线不能覆盖焊盘,应从焊盘末端引线;

- 引脚间距较为密集的贴片元件焊盘引脚,需要从焊盘外部走线进行连接,不允许直接连接引脚之间的焊盘;

- 过孔可能会引发信号传输线的阻抗突变,因此需要尽量减少过孔使用的数量;

- 信号传输线上避免出现桩线,如果无法避免,那么桩线的长度应小于信号的上升时间,避免出现反射;

- 高速信号走线换层时,附近要有接地孔提供回流环路,确保整板回环小阻抗小;

- 模拟信号不要使用 EDA 工具的自动布线功能;

- 对敏感节点使用屏蔽线,即在受干扰结点的周边添加一组屏蔽线,并且在屏蔽线上放置多个接地过孔;

串扰

- 反向电流平行走线带来的串扰较大;

- 串扰强度与走线长度成正比,与间距成反比,与频率成正比;

- 加大走线的间距,缩小走线的平行长度,必要时可以采用 Jog-Out 凹凸布线;

- 加入端接匹配可以降低反射,并且减小串扰;

- 将信号层限制在高于接地平面

10mil范围以内; - 向串扰比较严重的两条线之间插入一条地线进行隔离,从而减小串扰;

- 避开噪声源,例如 MCU、电感、晶振邻近的表层严禁走线或者打过孔;

覆铜

- PCB 设计当中,没有布线的区域最好选择一个较大的接地平面来进行覆盖,以提供屏蔽和提高去耦能力;

- 发热元件周围或者大电流走线应当尽量避免使用大面积铜箔,长时间受热会导致铜箔膨胀脱落;

- 发热元件周围如果必须使用大面积铜箔,那么最好采用栅格覆铜,便于释放铜箔的表面张力;

- 相同层的走线分布不平衡或者不同层的铜分布不对称时,推荐覆铜设计。

- PCB 最外层如果存在大面积的区域没有走线,建议在该区域内栅格覆铜,使得 PCB 整体的铜箔分布均匀;

- 推荐铺铜网格之间空白方格的大小约为

25mil x 25mil; - 噪声敏感的电路需要考虑接地屏蔽,即在信号层的四周布宽度大于

50mil地线或间距小于300mil的地孔; - 孤铜(特别是表层)超过

150mils时,不能打接地过孔,需要删除该区域,以免形成悬空的天线;

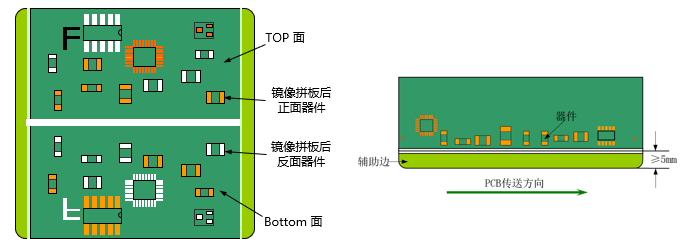

PCB 拼板

拼板是指由于电子元件自动化贴片,需要将单块 PCB 电路板进行 V 割或者邮票孔处理的加工方式。常见的 PCB 拼版方式主要有 3 种:同方向拼版、中心对称拼版、镜像对称拼版。

同方向拼版:最简单的拼板方式,将同款的 PCB 设计平铺复制以后就可以实现。

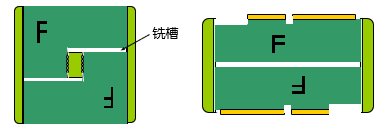

中心对称拼版:适用于拼接两块形状不规则的 PCB,中间必须开铣(xǐ)槽才能够进行分离;如果拼版以后产生较大变形,可以考虑在拼版中添加邮票孔连接的辅助块。

镜像对称拼版:通常在 PCB 正反面的贴片元件都能够满足回流焊的焊接要求时采用,但是要注意镜像对称拼版需要满足 PCB 光绘的正负片对称分布,例如四层板第 2 层为电源/接地的负片,则与其对称的第 3 层也必须是负片,否则不能采用镜像对称方式拼版。

工艺边

工艺边是为了满足自动化贴片的需要而增加的辅助部分,生产完成之后会被移除,一般设计为 5mm。

- 定位孔: 用于 PCB 加工和测试时的定位,一般设计为

2mm的过孔; - Mark 点: 用于自动化贴片机进行识别定位,通常设计为

1mm的焊盘;

测试点

关键元件需要在 PCB 设计上添加测试点,以便于后期进行自动化的飞针测试。不允许将用于焊接贴片元件的焊盘作为检测点,必须单独设计专用的测试焊盘,以降低对于焊点检测和生产调试的影响。用作测试点的焊盘需要尽可能分布在 PCB 相同侧,以降低检测时间和成本。

- 测试点距离 PCB 边缘尽量大于

5mm; - 确保测试点不会被阻焊层或者其它油墨覆盖;

- 测试点最好镀锡或者沉金处理,以防止氧化;

- 测试点尽量放置在距离元件

1mm以外,避免元件遭到探针的错误撞击; - 测试点需要距离定位孔

3.2mm以上; - 测试点的直径不可小于

0.4mm,相邻测试点的间距最好在2.54mm以上; - 测试面不能放置高度超过

6.4mm的元器件,以避免探针的测试夹具撞击到这些过高的元件; - 确保每块芯片都拥有电源和接地测试点,并且尽可能靠近芯片(最好小于

2.54mm); - 在 PCB 走线上设置测试点时,可以将测试焊盘的宽度进行适当放大;

- 测试点应当均匀分布在 PCB 上面,以避免探针下压产生的应力过于集中;

- 电源应当分区域设置测试点,以便于去耦以及故障查询;

PCB 布线五要素

- 规划电路分区,核心元件布局在整板的正中心,而其它重要元件也尽量分布在中轴线附近;

- 电源优于一切,电源的输入输出走线尽量加粗(线宽不能超过元件引脚焊盘,或者选择回路走线),不同铜层之间的电源走线可以通过多个过孔(2 ~ 6 个)来提高载流能力;

- 模块化设计思路,理解每一个电路模块,对于重要的模块和信号走线要进行合理的包地处理;

- 合理的扇出 Fanout 贴片元件引脚,保持走线的美观;

- 最优走线层通常是指最为靠近完整地平面的走线层;

PCB 布线基本策略

- 首先放置

安装孔、接插件、开关等结构件相关的封装位置; - 基于封装原点的 X/Y 位置,设计封装属性当中的相对 X/Y 位置,从而实现封装放置的精确定位;

- 首先摆放主控 IC 芯片,然后分功能模块摆放其它 IC 芯片,最后再放置其它的附属元件;

- 滤波电容的容值越小,越需要靠近 IC 芯片的引脚进行放置(非常重要);相反的,如果容值较大,则可以适当的放置得距离引脚更远;

- 布线过程当中,如果飞线对于元件的连接关系形成了干扰,则可以隐藏 EDA 工具封装

值与位号的显示;

本文详细介绍了PCB设计的基本布线规范与设计原则,涵盖术语、元件封装、布线参数、封装尺寸、PCB堆叠、信号完整性问题等关键点。强调了差分对布线、阻焊设计、过孔寄生效应、电源布局以及防止电磁干扰的重要性。此外,还提出了布局规范和布线策略,帮助设计者在高速电路中解决信号完整性和电磁兼容性问题。

本文详细介绍了PCB设计的基本布线规范与设计原则,涵盖术语、元件封装、布线参数、封装尺寸、PCB堆叠、信号完整性问题等关键点。强调了差分对布线、阻焊设计、过孔寄生效应、电源布局以及防止电磁干扰的重要性。此外,还提出了布局规范和布线策略,帮助设计者在高速电路中解决信号完整性和电磁兼容性问题。

2399

2399

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?