个人课程学习所作,仅供参考

Verilog代码文件已丢失......

目录

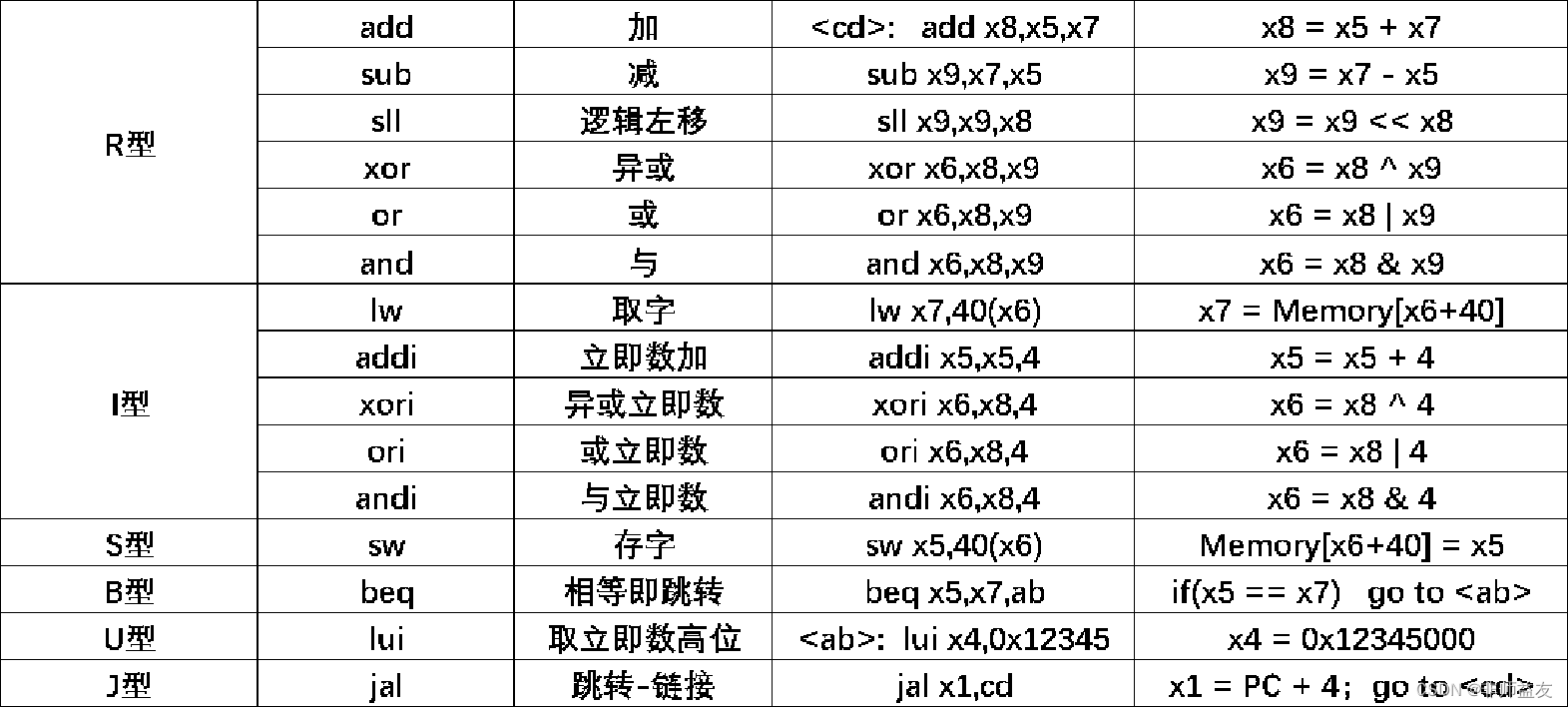

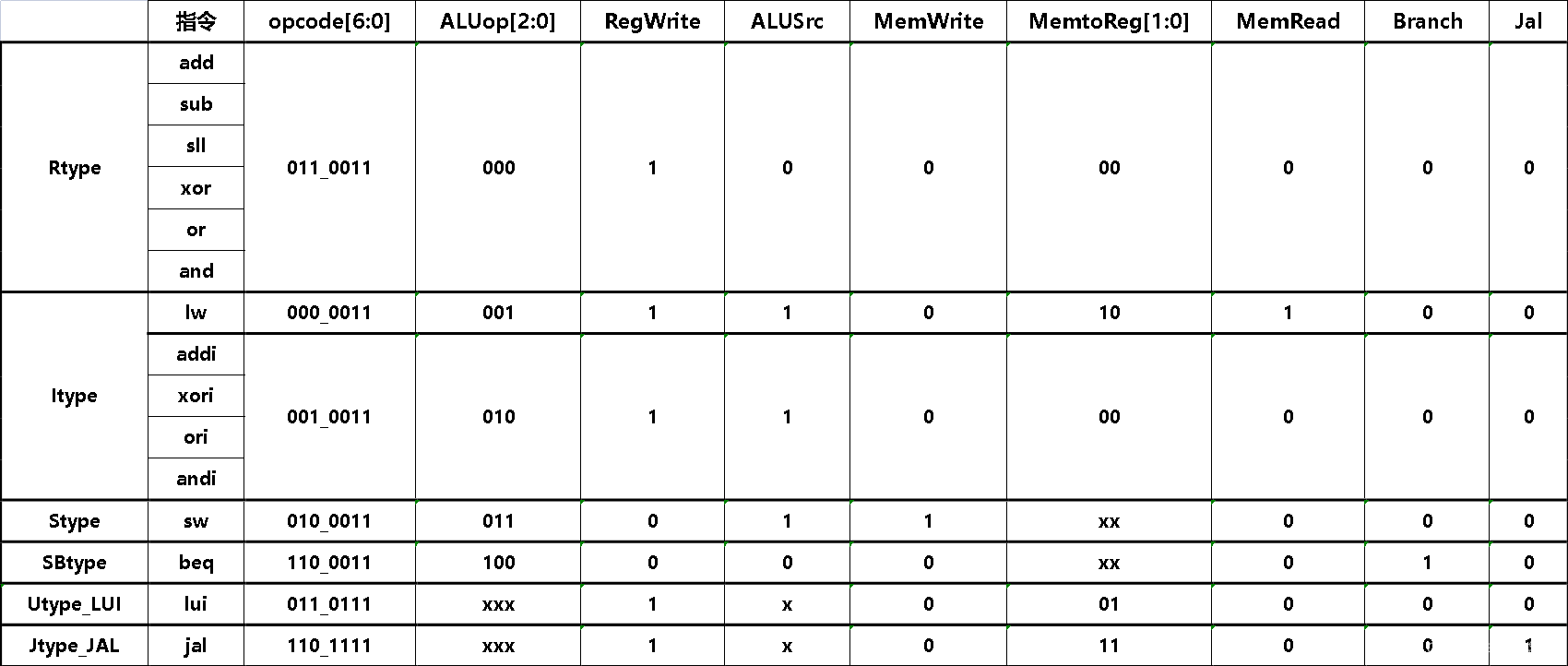

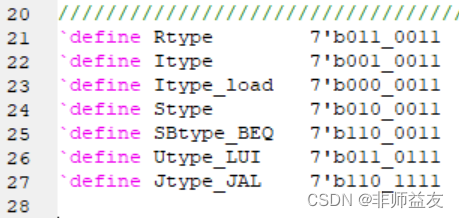

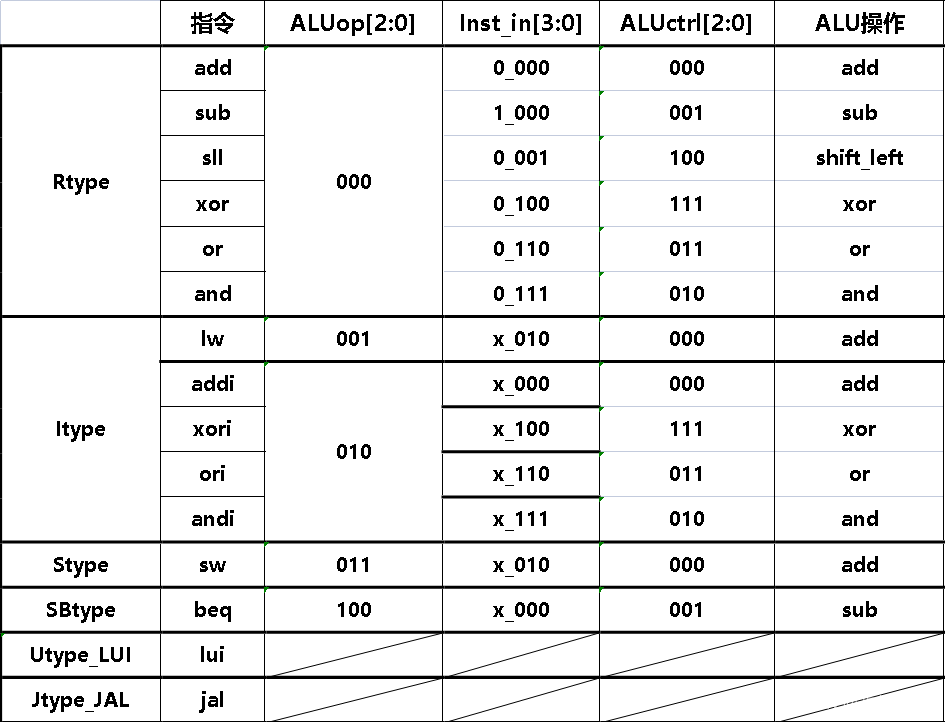

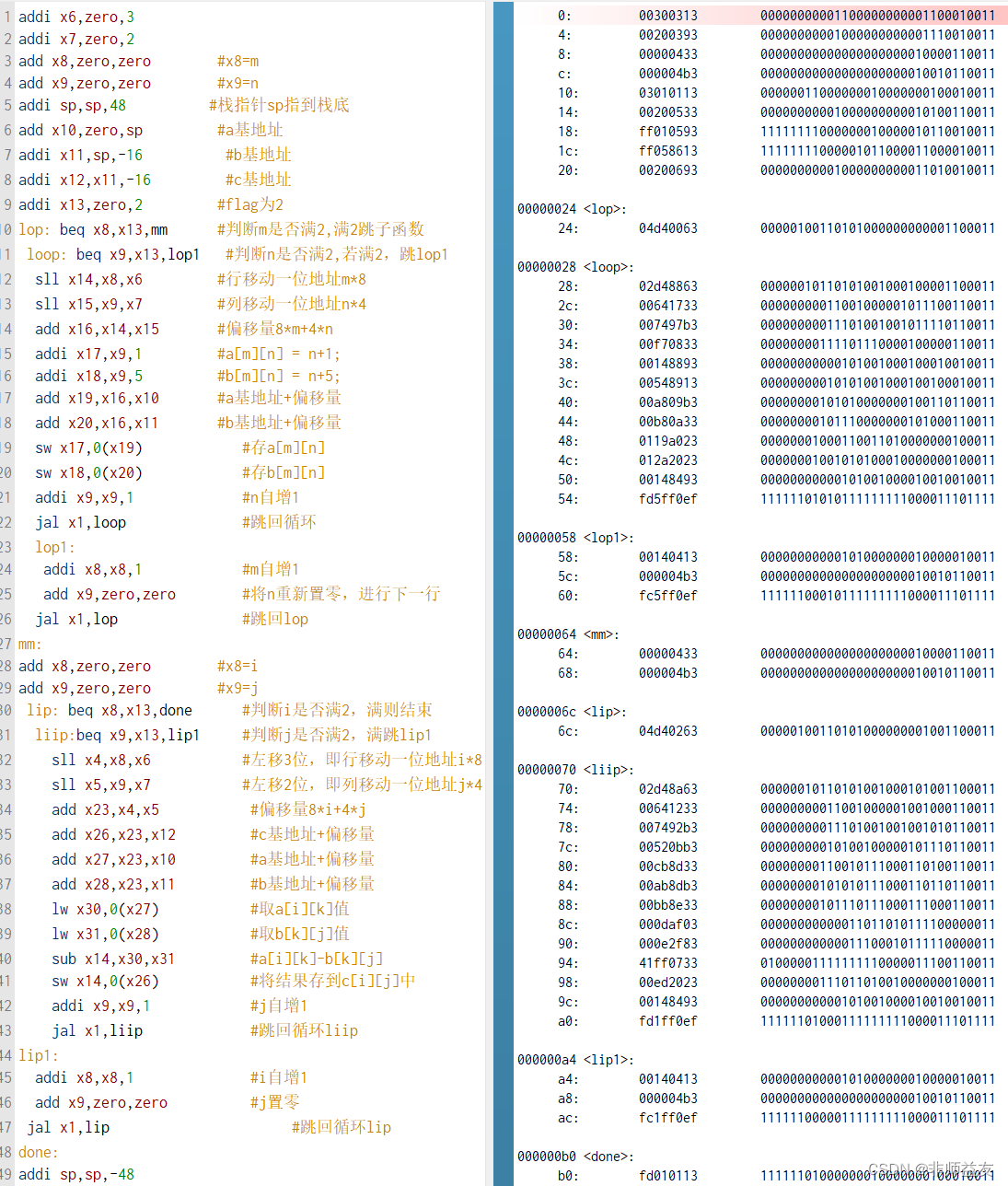

支持指令

设计支持6种类型的15条指令

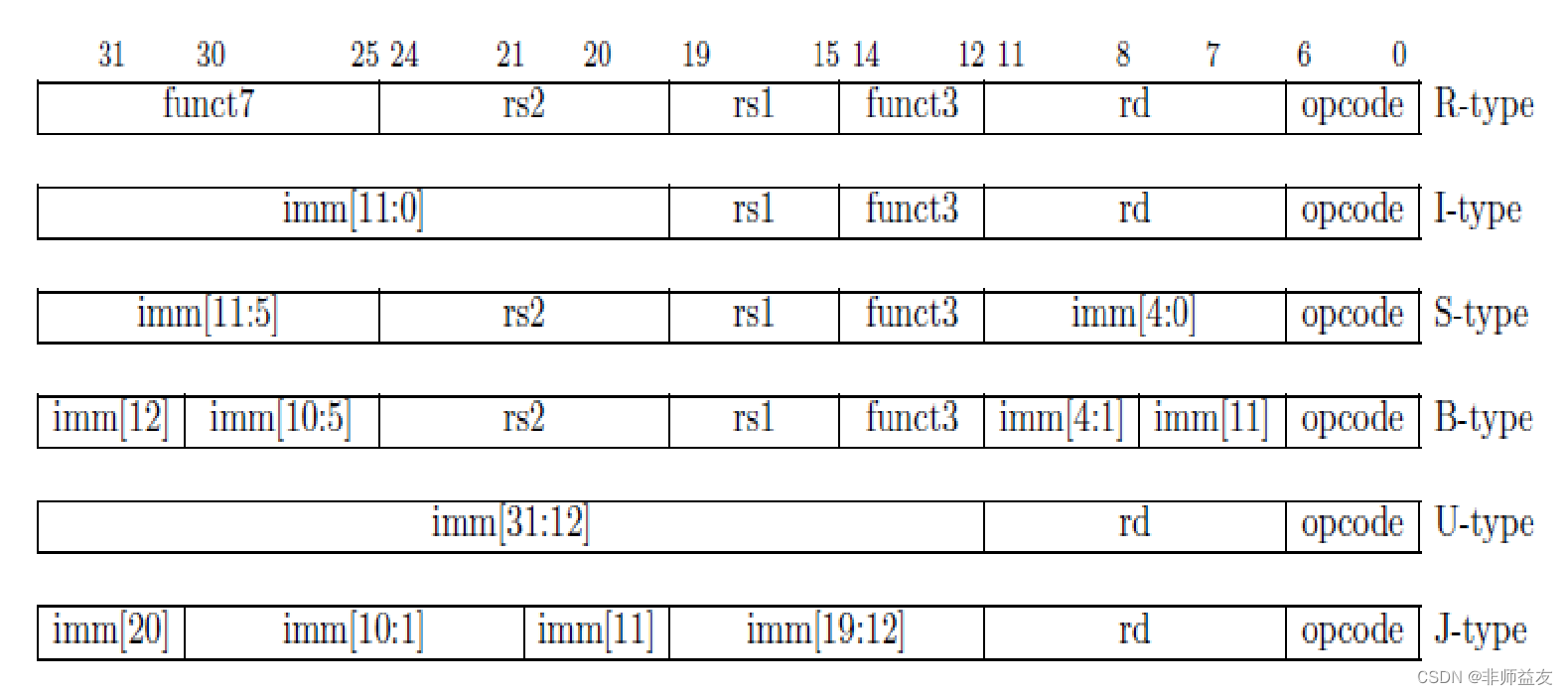

6种类型的指令格式

指令对应的op码、funct3/7字节

| opcode[6:0] | funct3[12:14] | funct7[25:31] | ||

| R_type | add | 0110011 | 000 | 0000000 |

| sub | 0110011 | 000 | 0100000 | |

| sll | 0110011 | 001 | 0000000 | |

| xor | 0110011 | 100 | 0000000 | |

| and | 0110011 | 111 | 0000000 | |

| or | 0110011 | 110 | 0000000 | |

| I-type | addi | 0010011 | 000 | XXXXXXX |

| ori | 0010011 | 110 | XXXXXXX | |

| xori | 0010011 | 100 | XXXXXXX | |

| andi | 0010011 | 111 | XXXXXXX | |

| lw | 0000011 | 010 | XXXXXXX | |

| U-type | lui | 0110111 | XXX | XXXXXXX |

| S-type | sw | 0100011 | 010 | XXXXXXX |

| B-type | beq | 1100011 | 000 | XXXXXXX |

| J-type | jal | 1101111 | XXX | XXXXXXX |

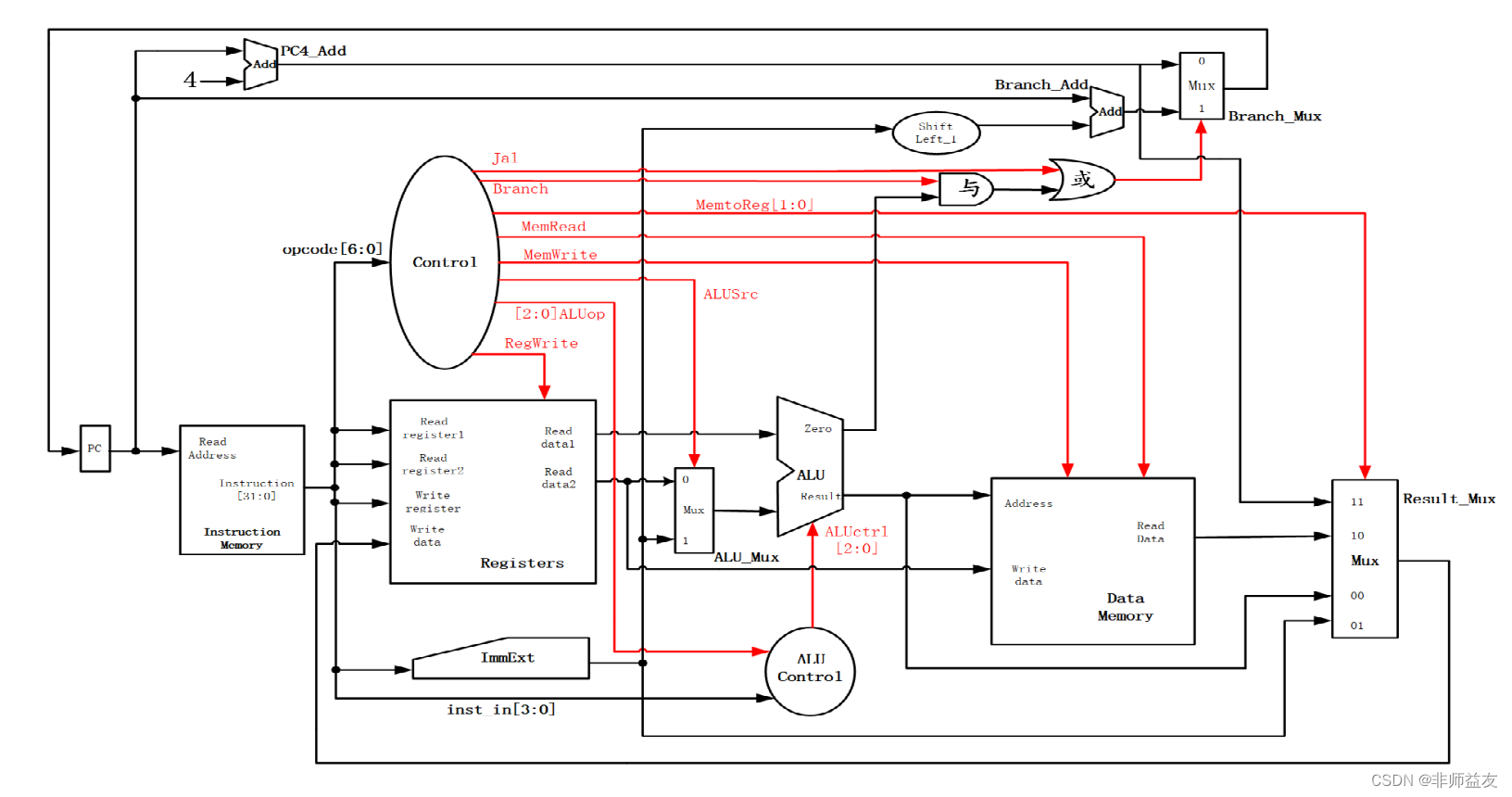

数据通路

数据通路

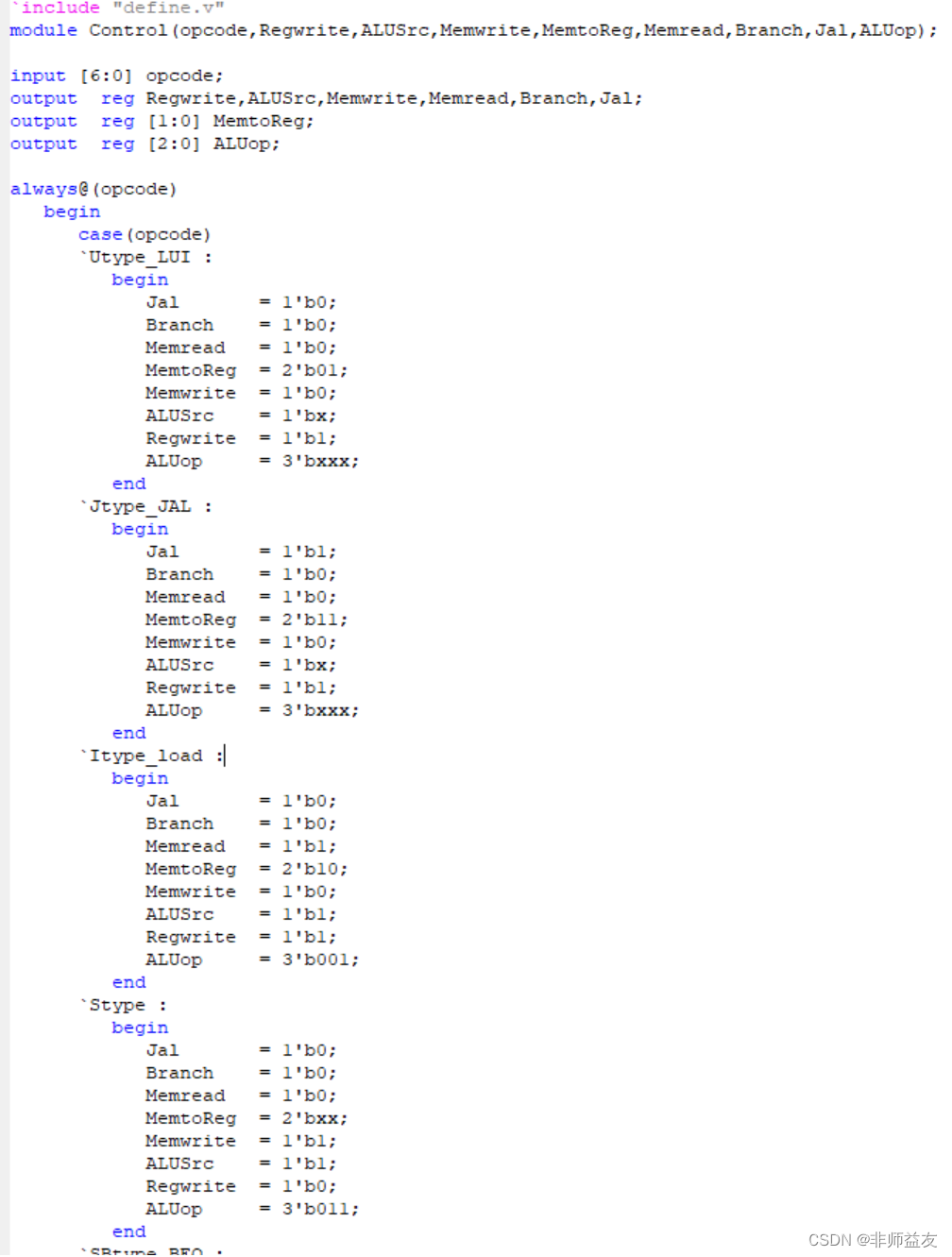

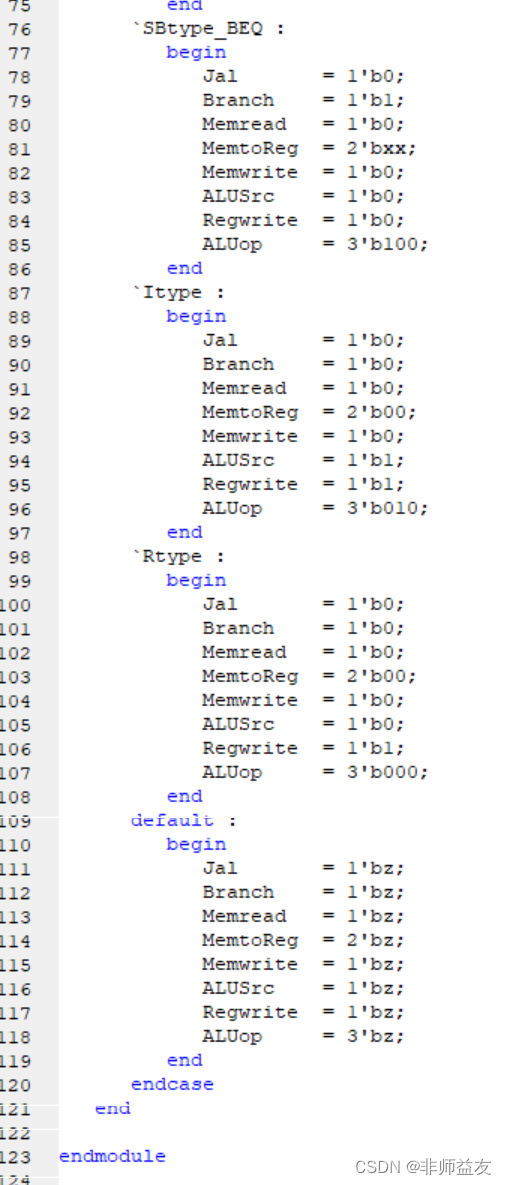

模块代码

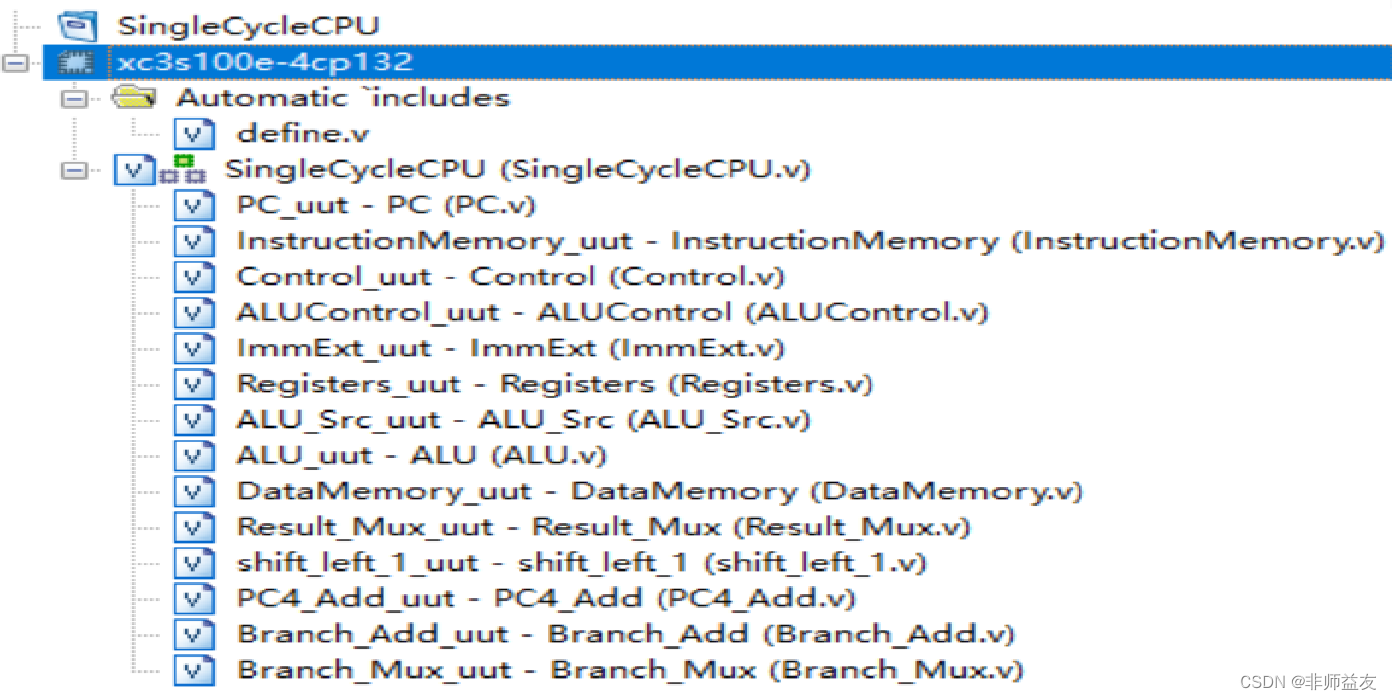

代码结构

-

SingleCycleCPU

-

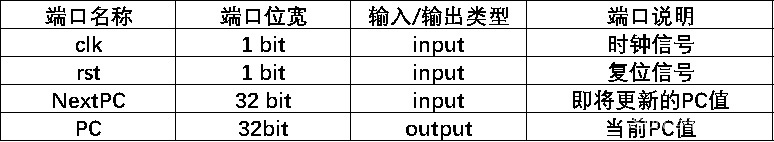

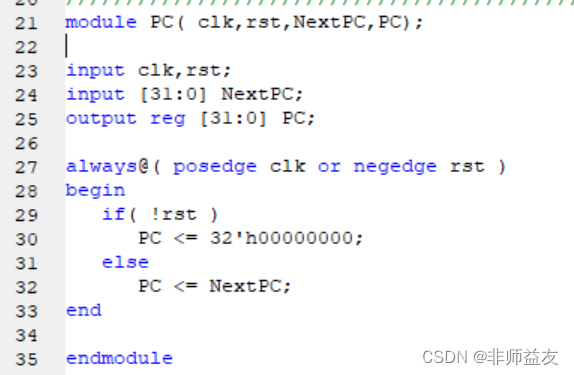

PC

-

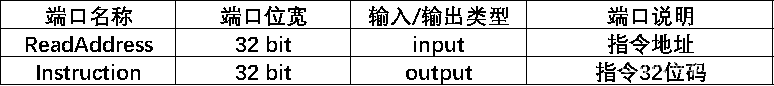

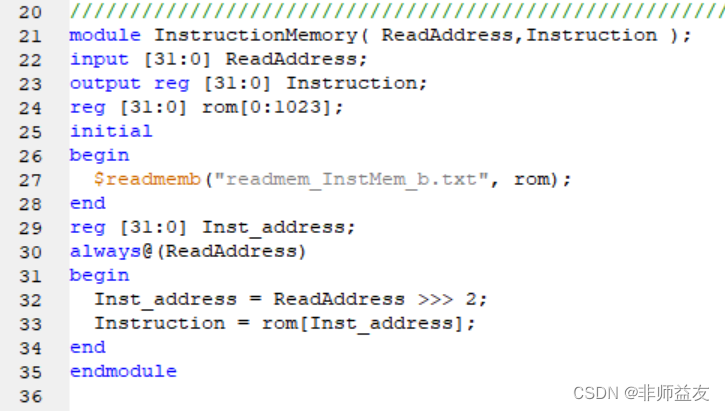

InstructionMemory

-

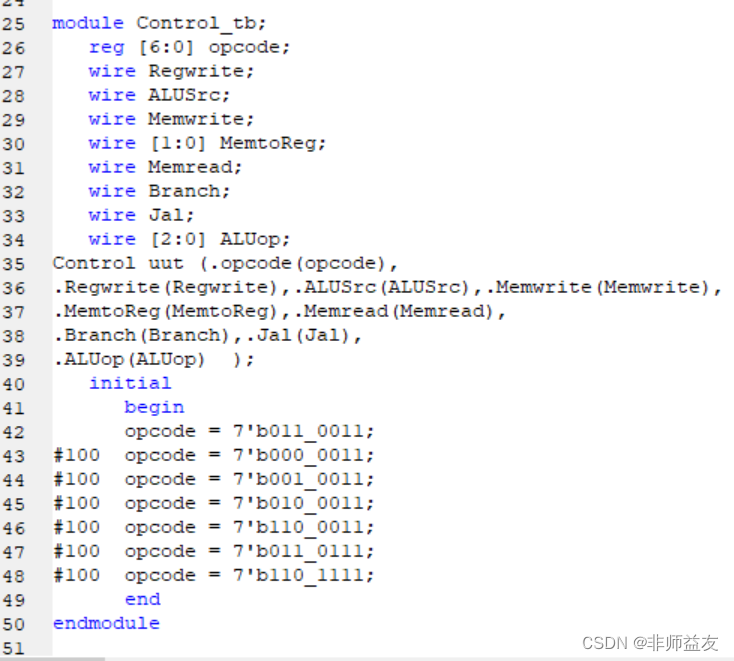

Control

-

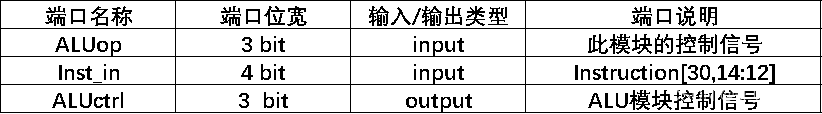

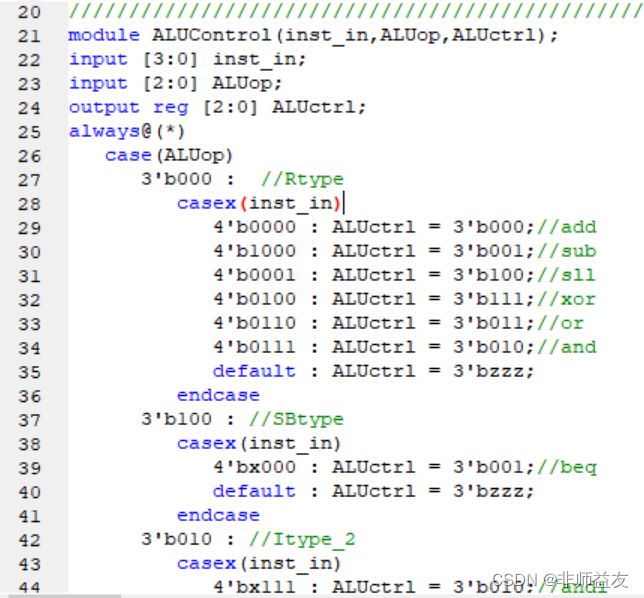

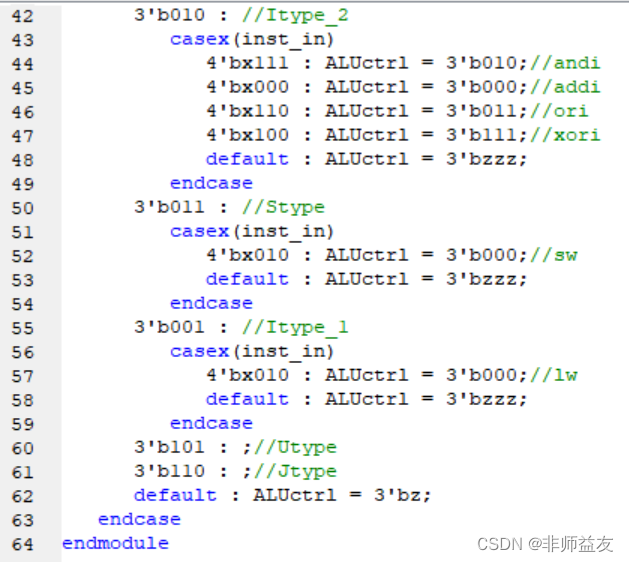

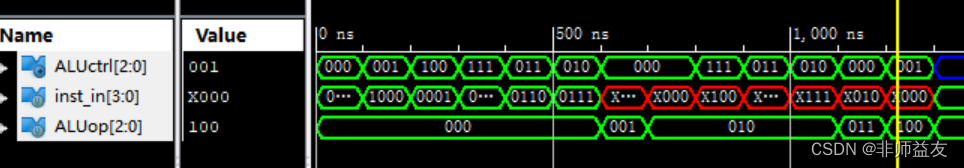

ALUControl

-

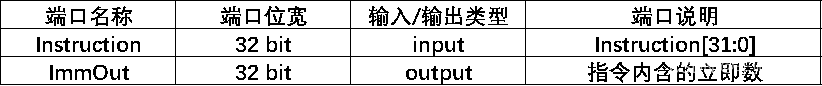

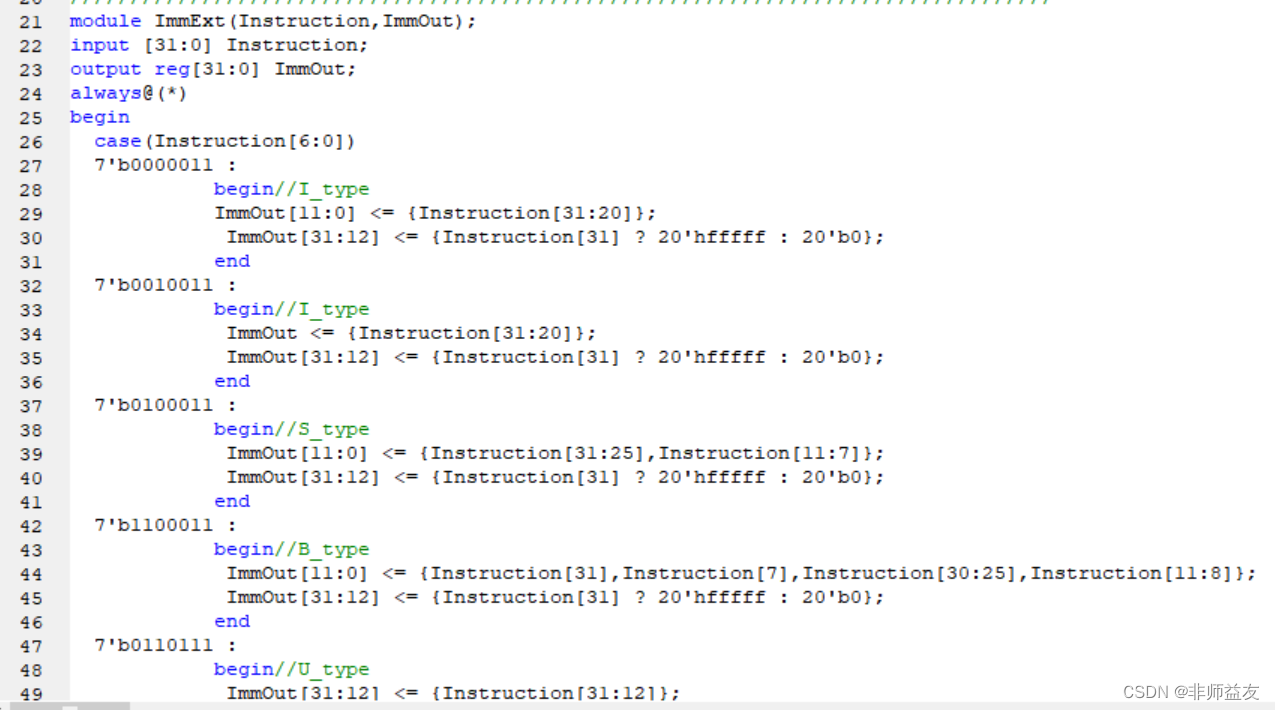

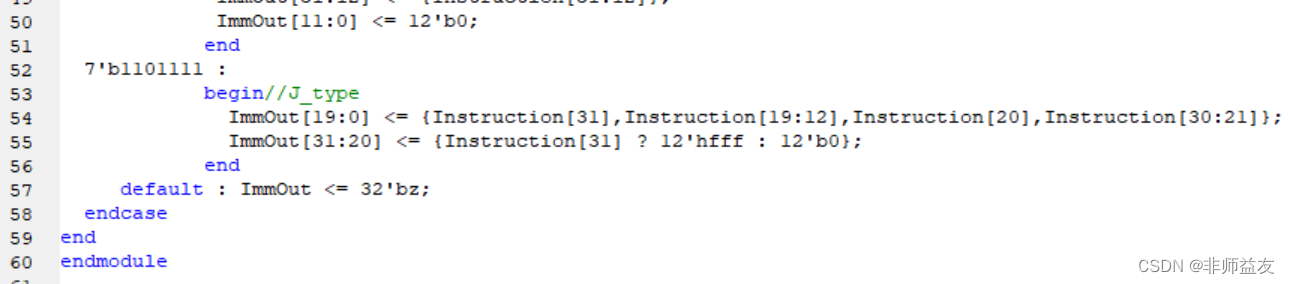

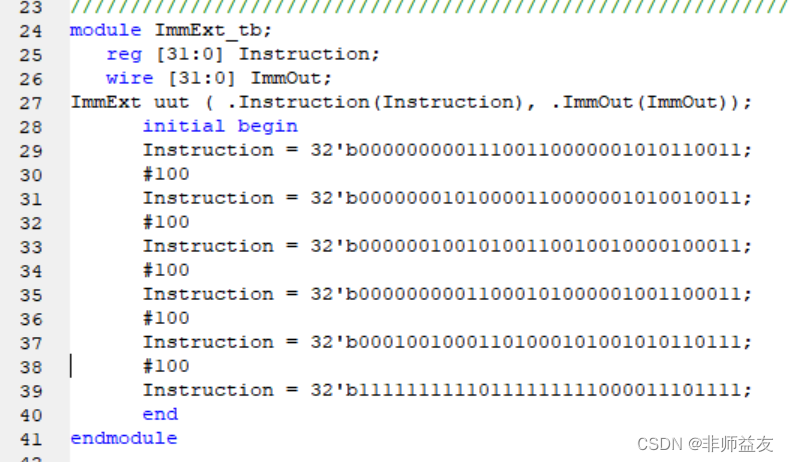

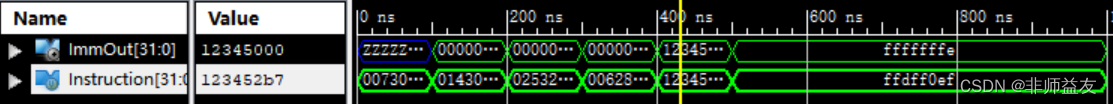

ImmExt

-

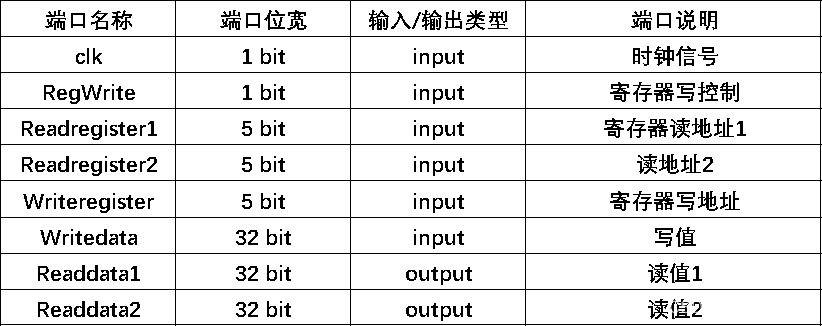

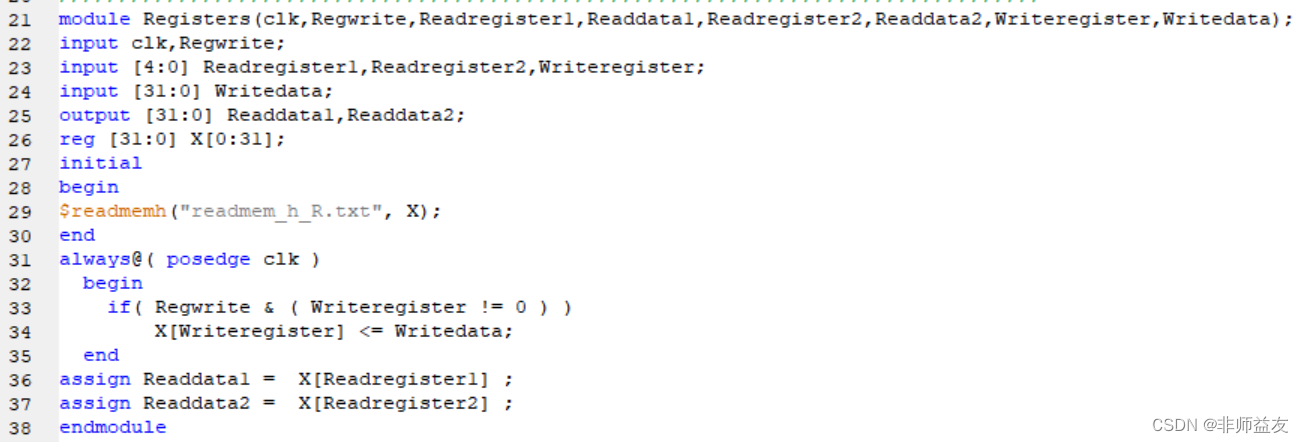

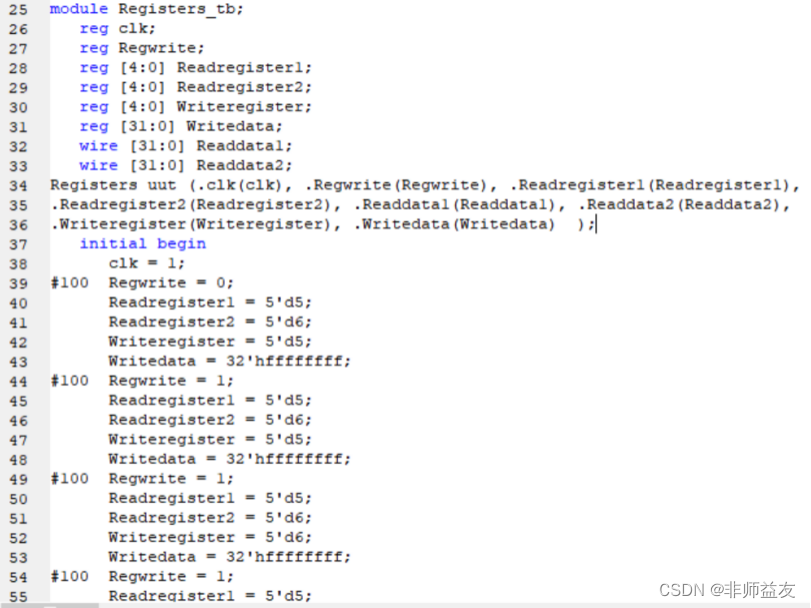

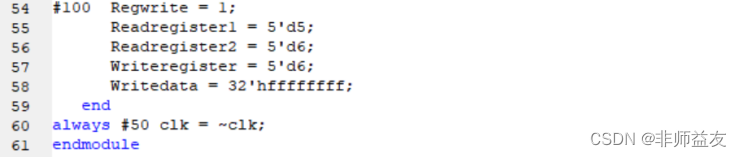

Registers

-

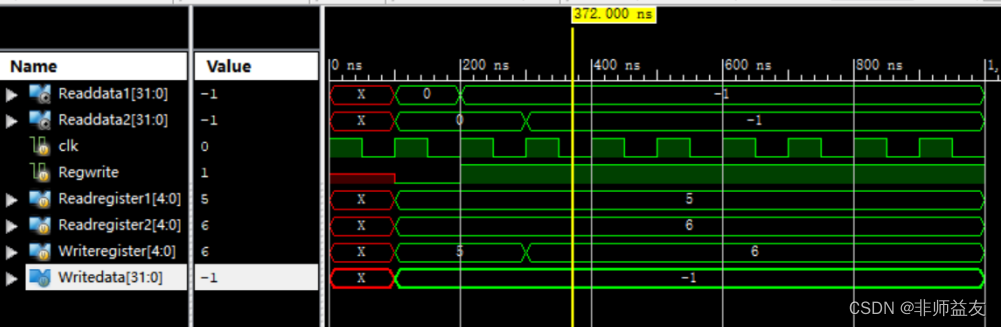

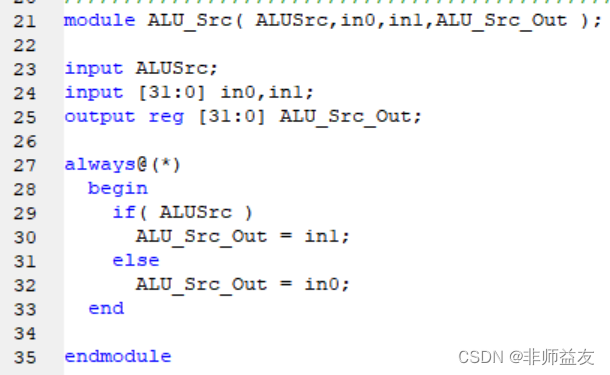

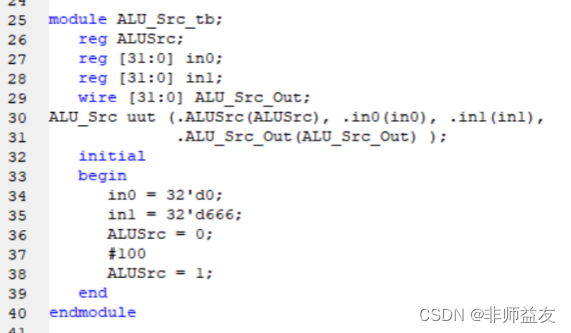

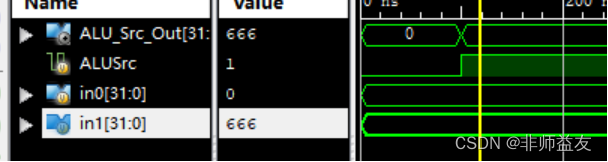

ALU_Src

-

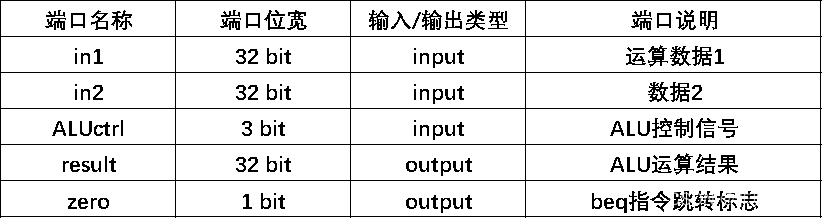

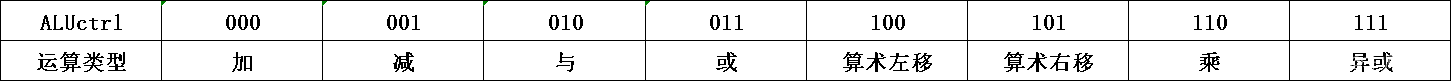

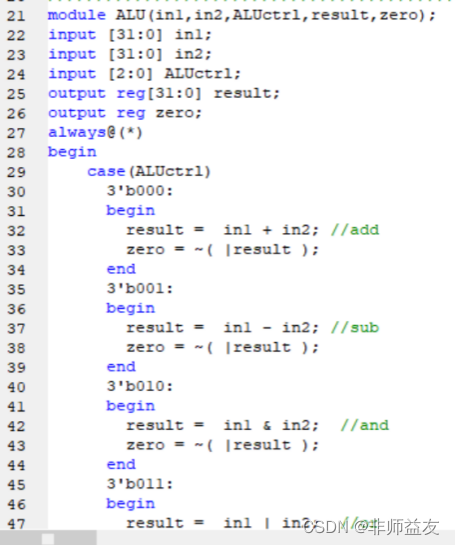

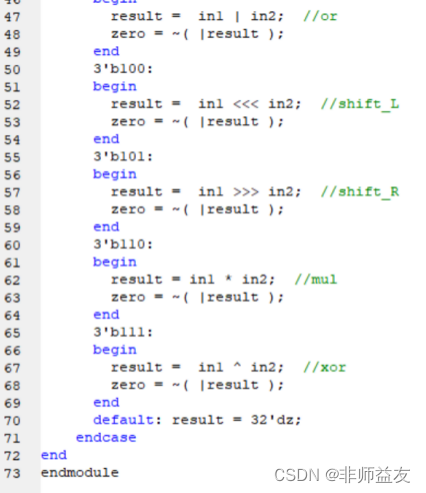

ALU

-

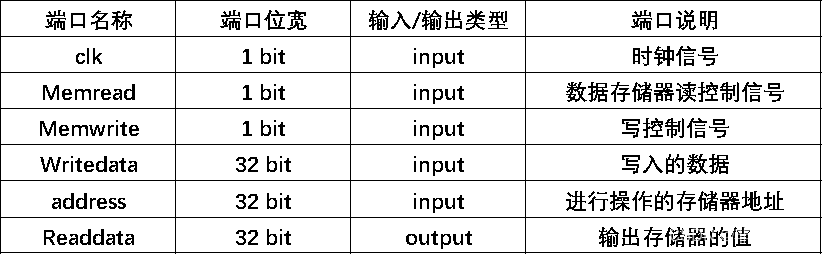

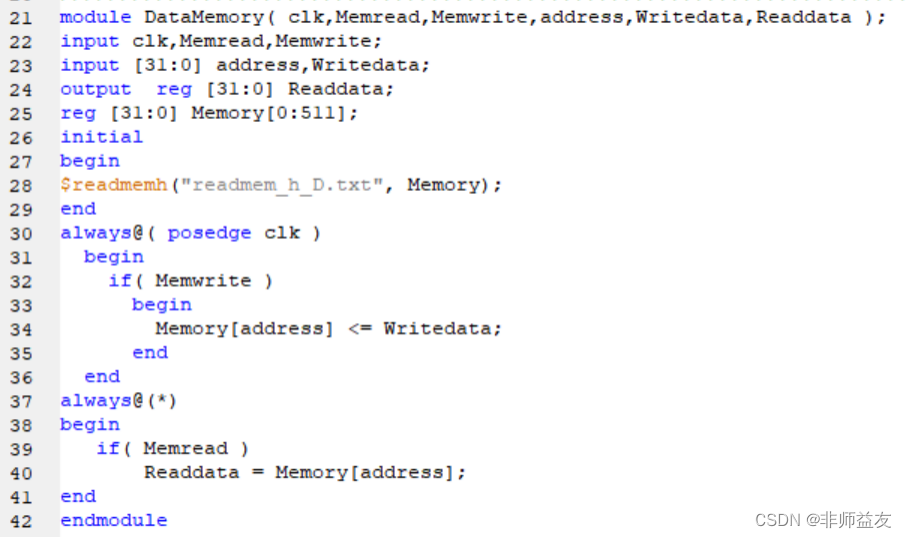

DataMemory

-

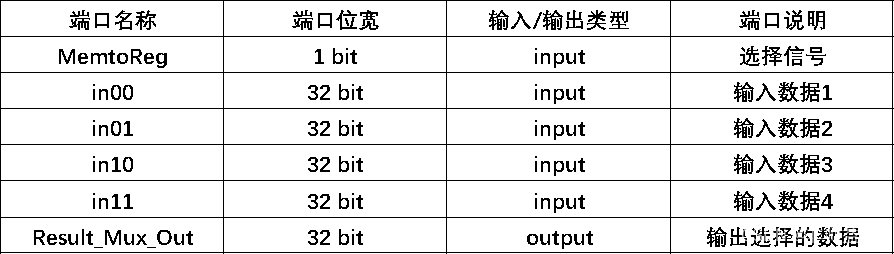

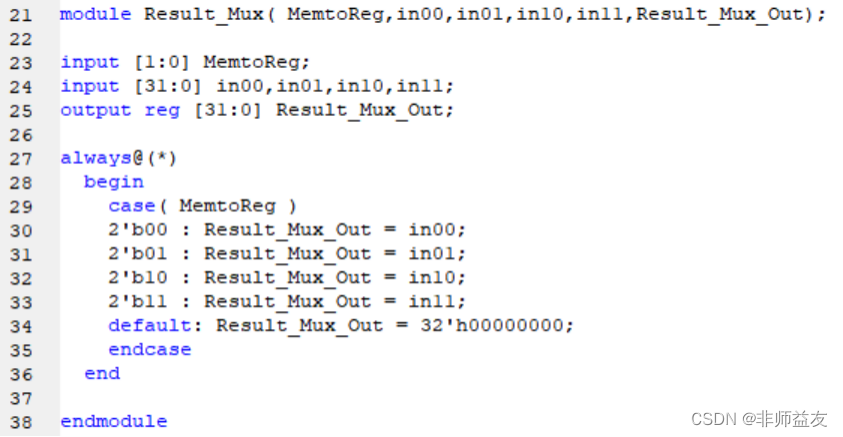

Result_Mux

-

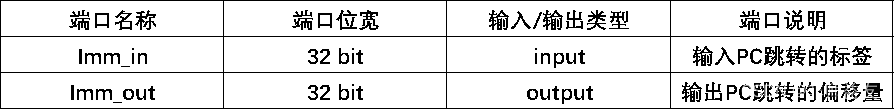

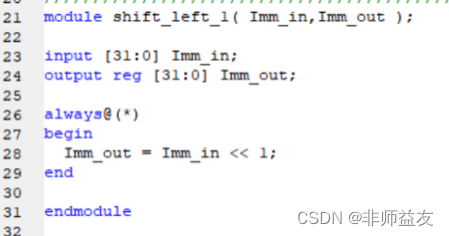

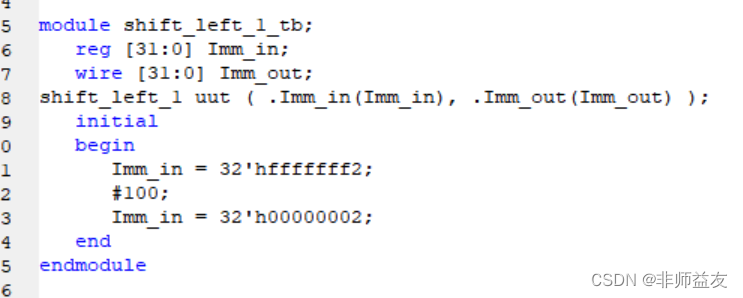

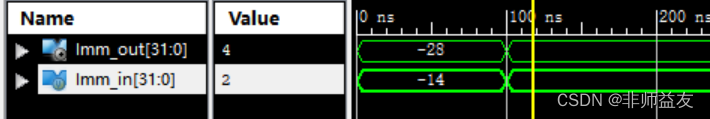

shift_left_1

-

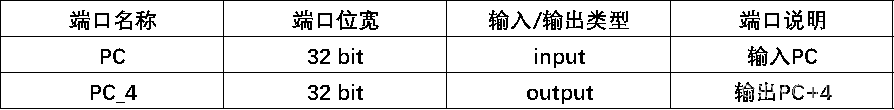

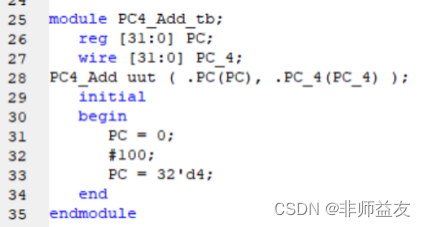

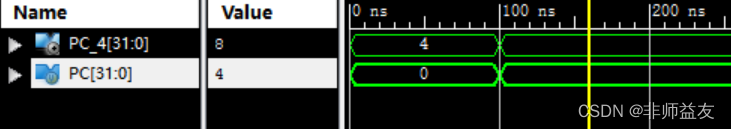

PC4_Add

-

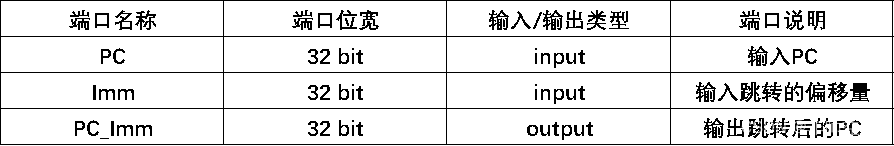

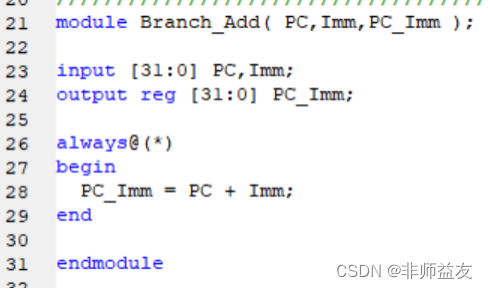

Branch_Add

-

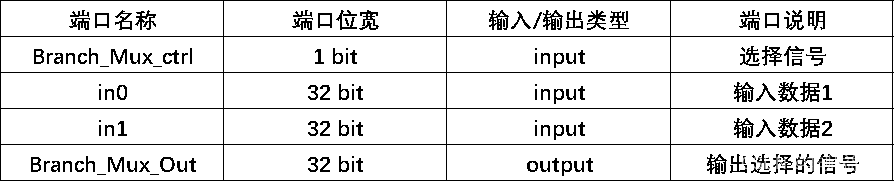

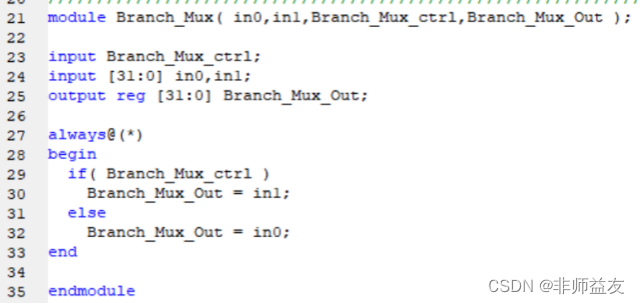

Branch_Mux

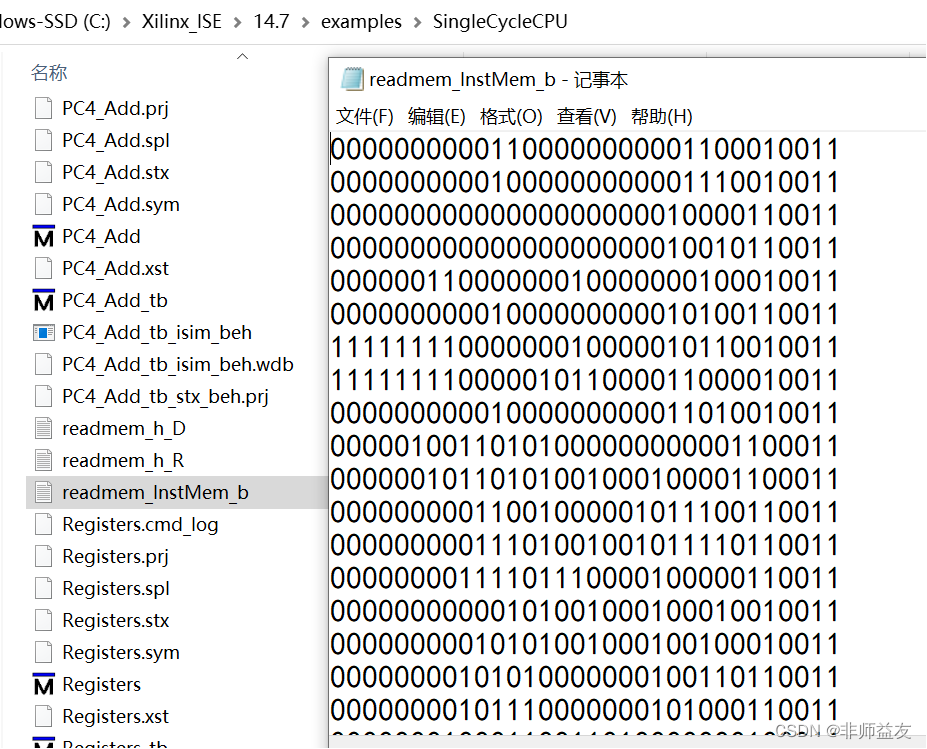

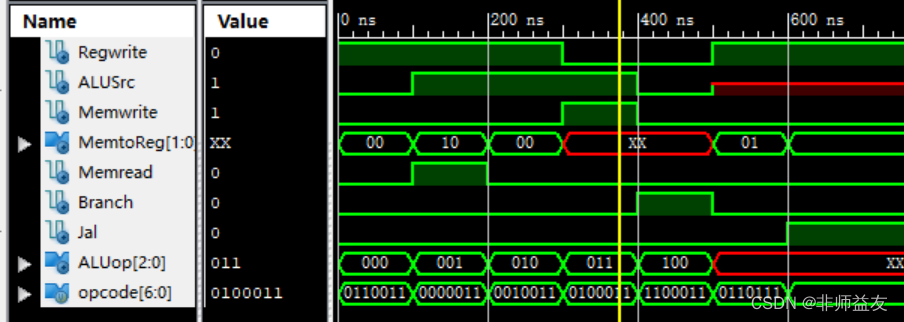

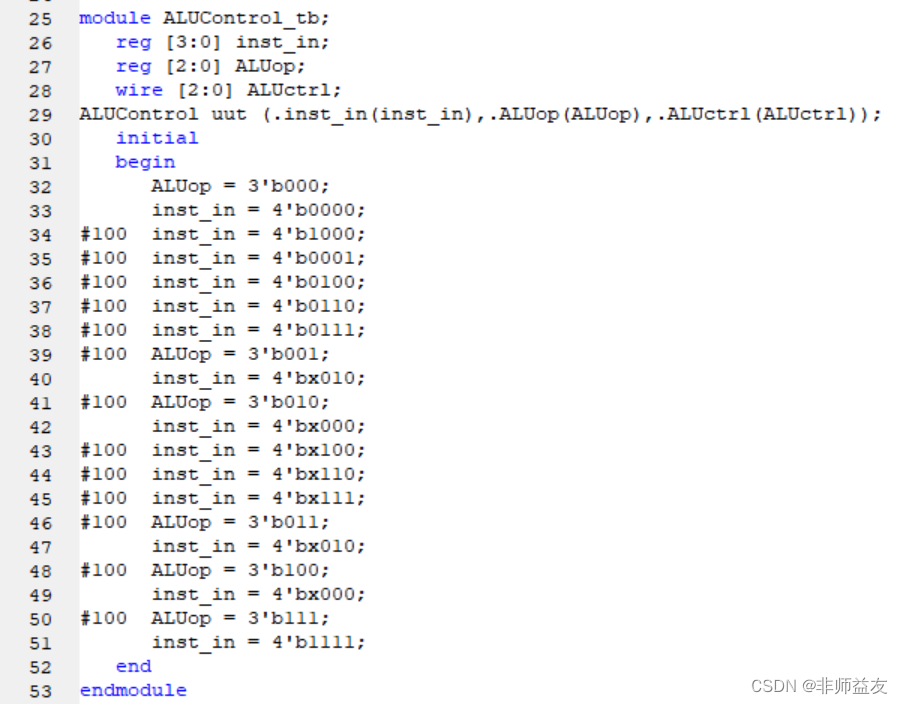

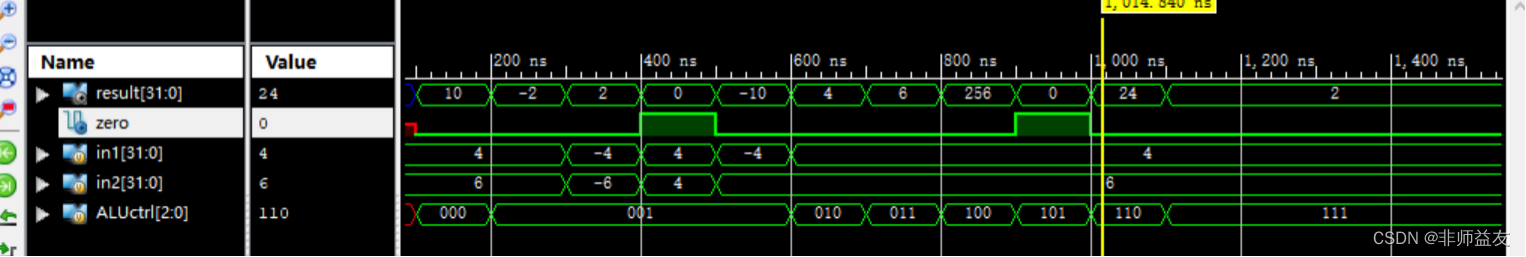

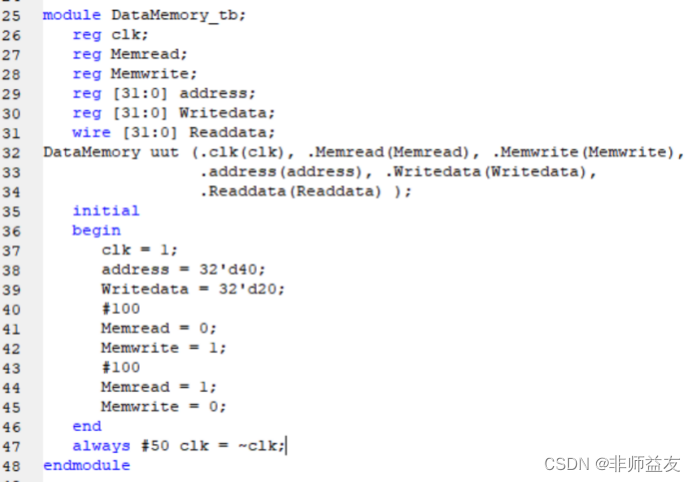

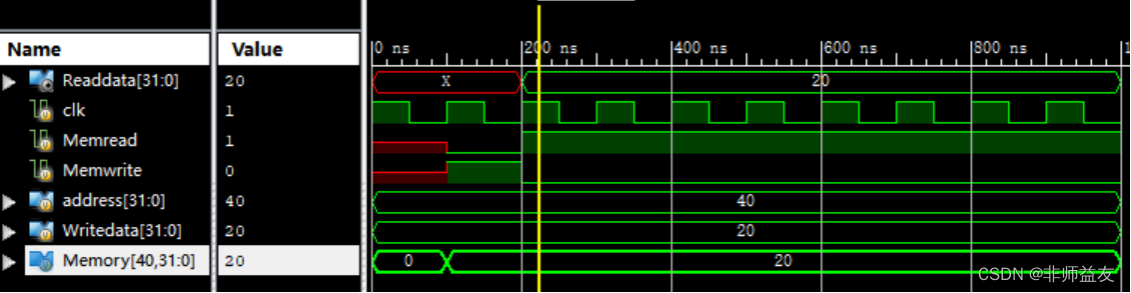

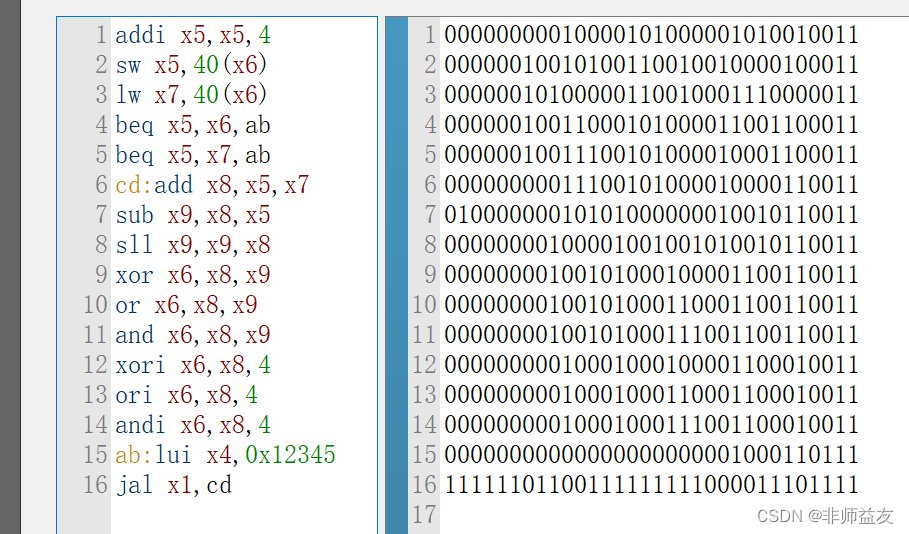

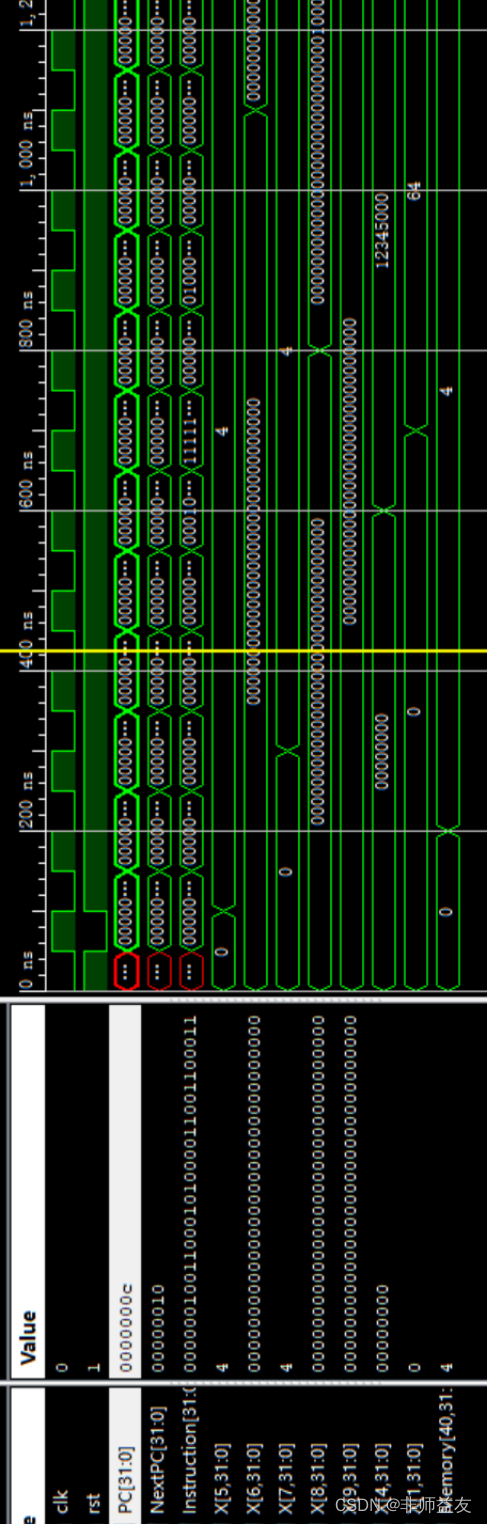

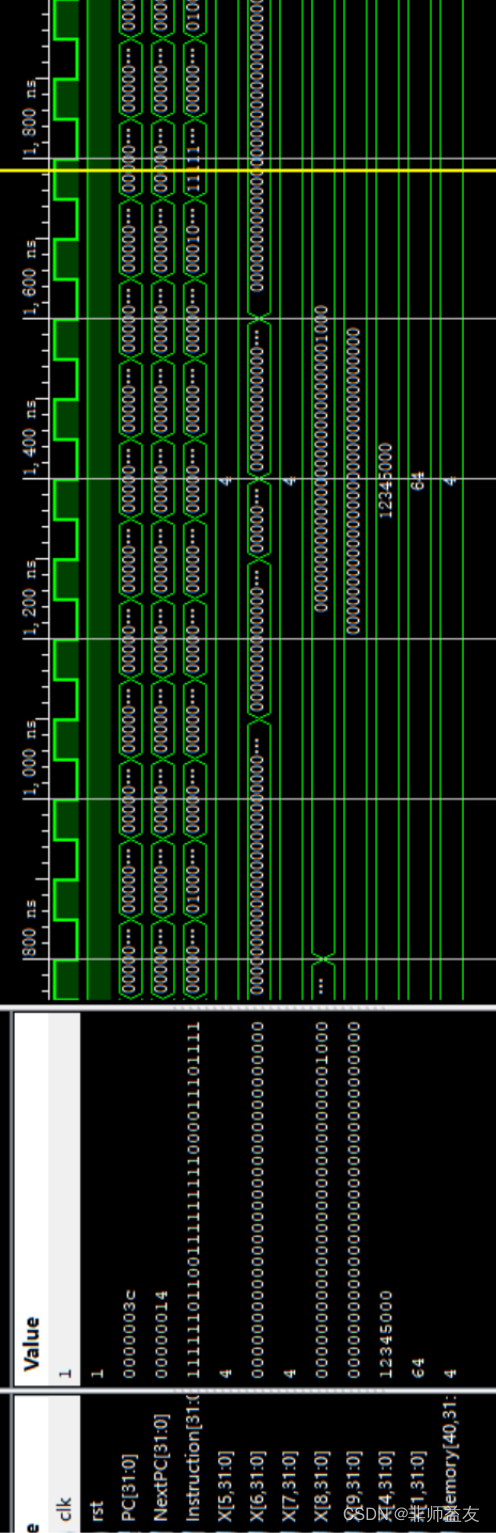

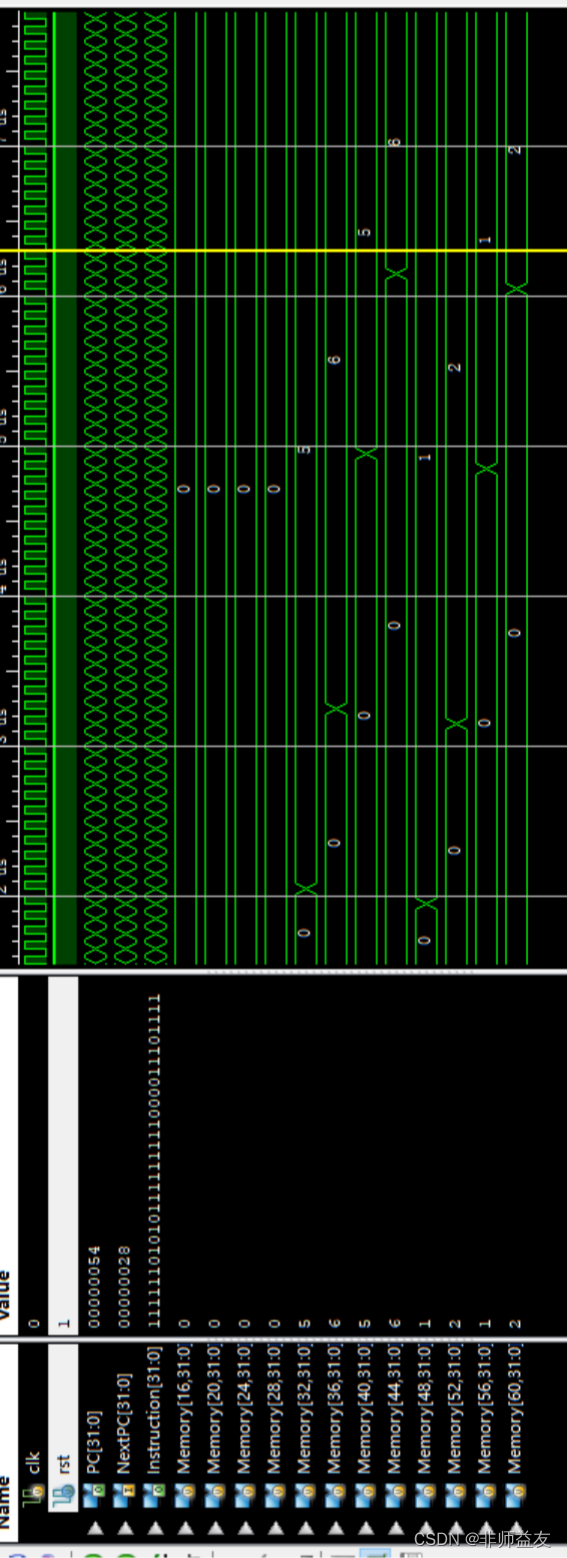

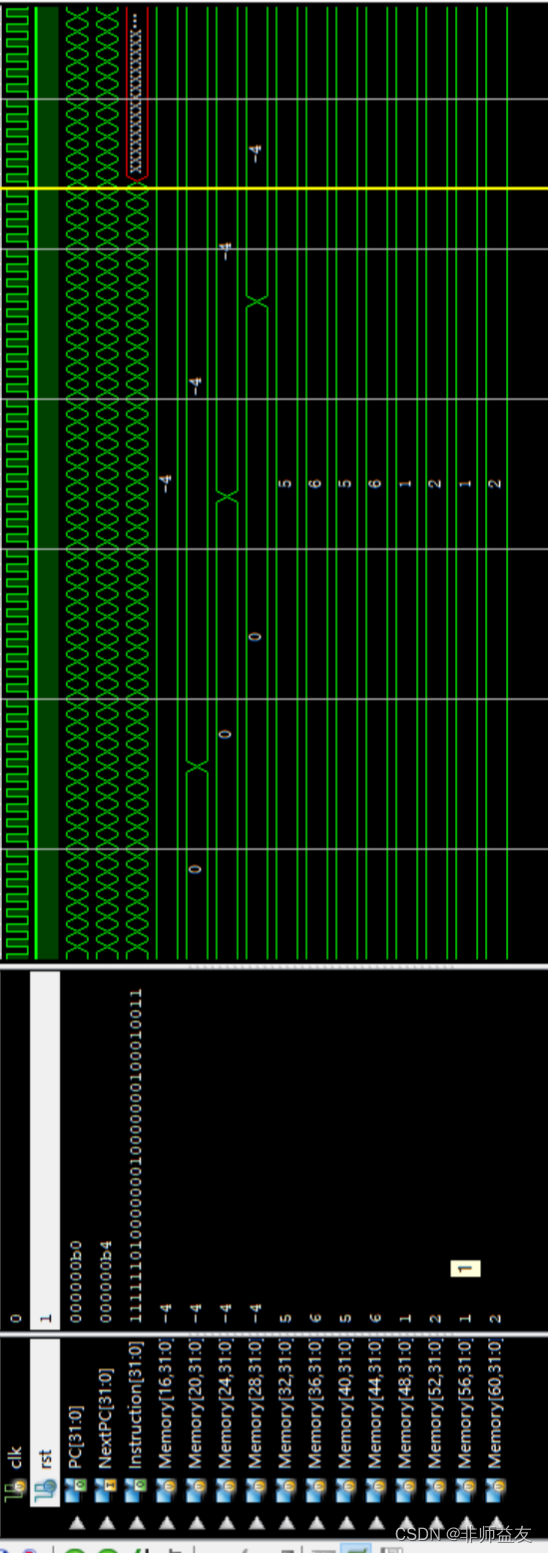

仿真测试

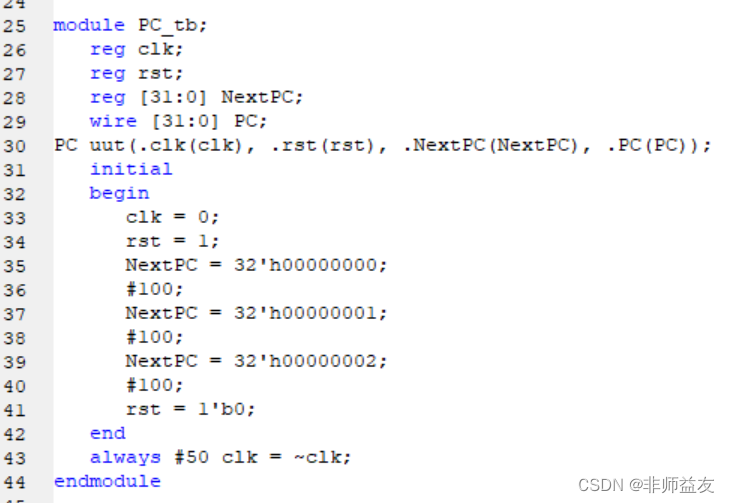

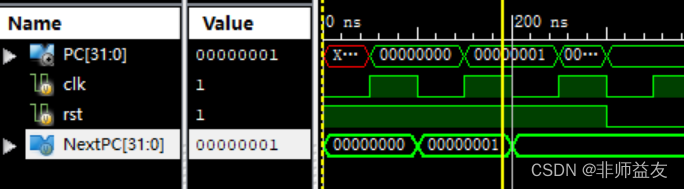

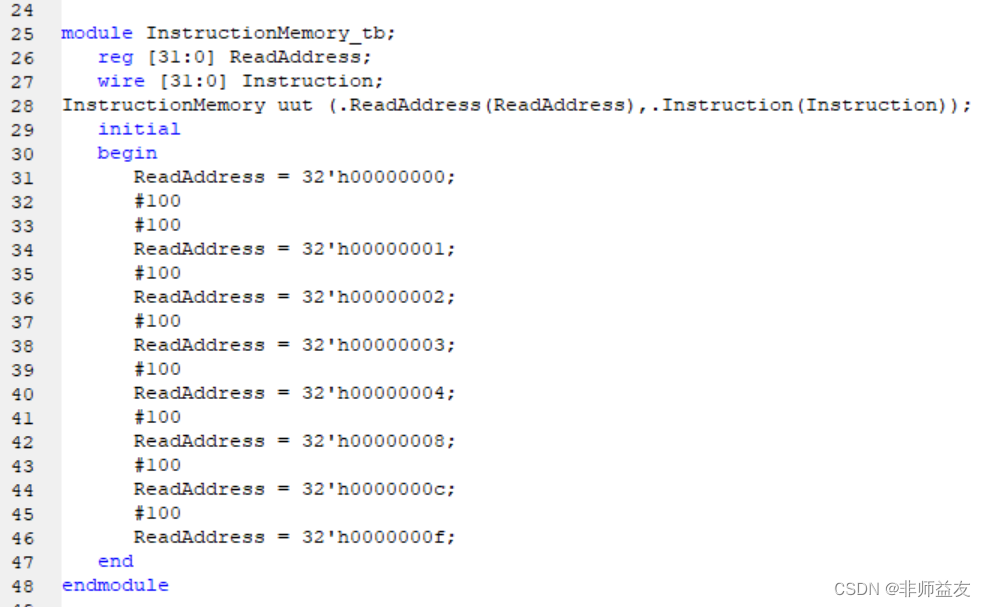

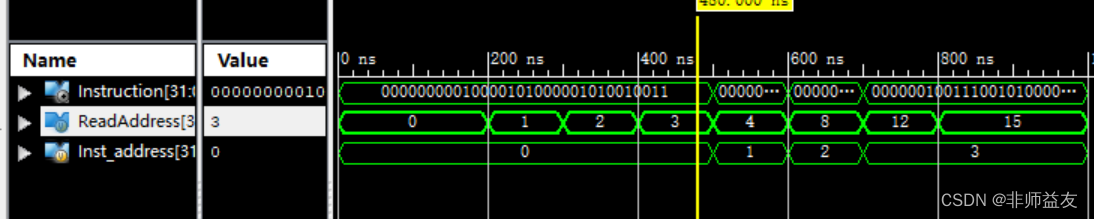

1.指令逐条仿真

2.矩阵相减仿真测试

623

623

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?