FPGA(1)在DE-115上电亮流水灯

前言

- 什么是fpga?

FPGA(Field Programmable Gate Array)是在PAL (可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点 - 我们需要哪些工具?

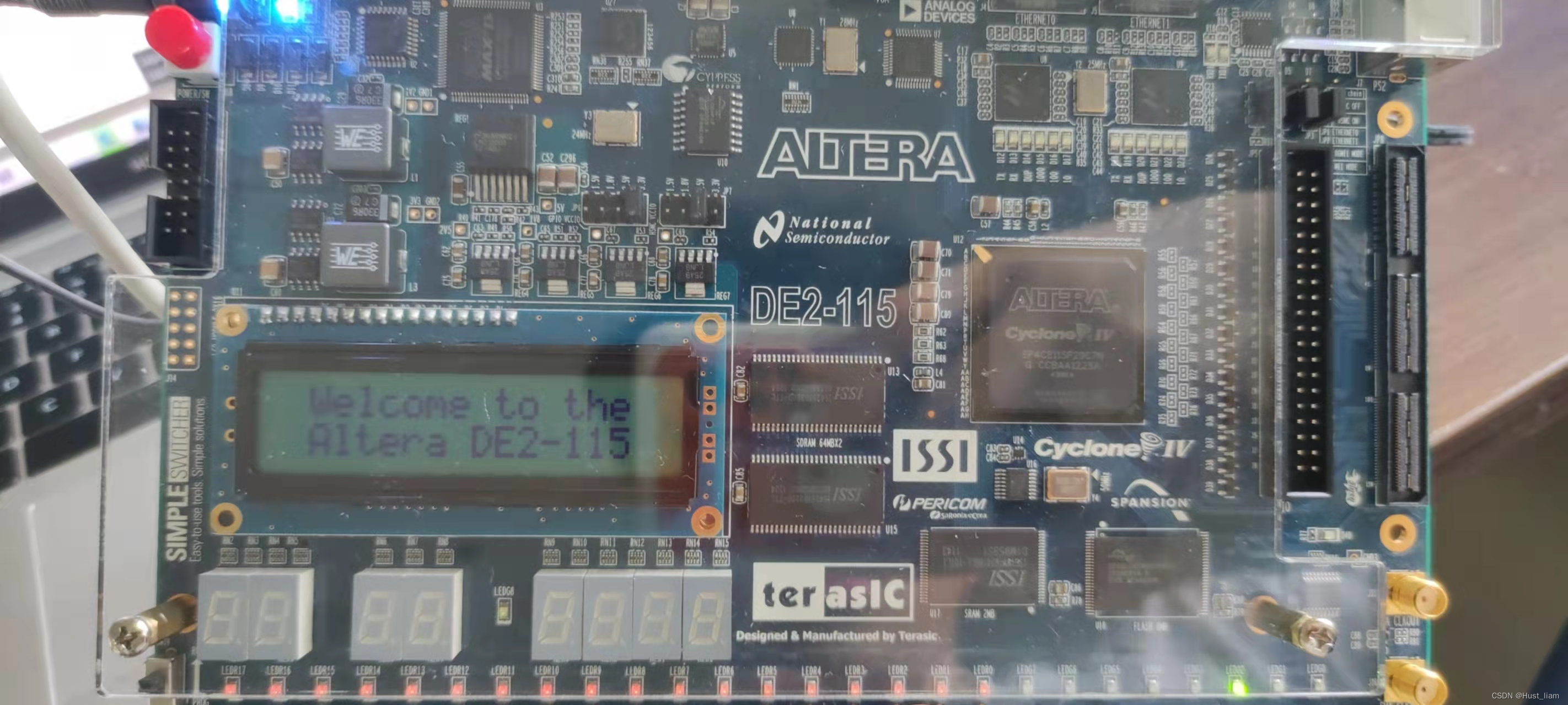

1.DE2-115开发板 2. Quartus Prime软件

2. Quartus Prime软件

一、Quartus Prime基础步骤

-

建立新的设计项目

进入主界面,选择File->New Project Wizard命令,点击next至项目界面,选择保存的位置,并输入项目名和顶层实体文件名。选择目标器件Cyclone IV E,再设置筛选条件,选择package中的FBGA,Pin count选择780,Core speed grade选择7,target选择specfic device selected 那个选项,再在最下方的devices目录里选择EP4CE115F29C7

再点击next至finish

再点击next至finish -

输入设计文件

File->New的design files中 选择verilog HDL Flies,输入设计文件,输入完成后保存,文件名输入waterlight.v,勾选下方的add file to current project,单击保存。 -

分配引脚

手工分配引脚的流程为assignments中Pin Planner,但在分配引脚前最好进行一次全编译(progressing中的start compilation。分配引脚的方式是双击端口旁的location,再右键点击箭头,或者手动输入引脚。该例中引脚如下

-

编译设计文件

-

编辑器件,测试功能

使用JTAG编程模式对FPGA器件编程,测试功能。首先将开发板左下角的SW19拨到上方,选择tools中的programmer,将文件导入后,确认器件名为EP4CE115F29,并确认program小方框勾选,选择mode下拉列表框中的JTAG,单击左上角Hardward Setup,在弹出的窗口中选择USB-Blaster,单击start开始

二、文件部分

1.设计管脚

代码如下(示例):

module waterlight(input En,input CP,output reg [0:7] Out);//匹配8个灯,故宽度为8

reg [25:0] cnt;

reg cnt1;

reg Cn;

parameter cnt_max = 26'd49_999_999;//时钟的频率是50mhz,要实现几秒钟变一次就调到//相应时间,例子为1s每次

2.读秒部分

代码如下(示例):

always@(posedge CP or negedge En)//该always循环实现的是一秒钟的计数

if(En==1'b0)

cnt<=26'd0;

else if(cnt == cnt_max)

cnt<=26'd0;

else

cnt<=cnt + 1'b1;

always @(posedge CP or negedge En) //cnt每次为1代表到了一秒钟

if(En==1'b0)

cnt1<=1'b0;

else if(cnt == cnt_max-1'd1)

cnt1<=1'b1;

else

cnt1<=1'b0;

利用两个循环,用cnt1代表到1s时间

3.亮灯部分

代码如下(示例):

always @(posedge CP or negedge En)

if(En==1'b0) begin

if(Dn==1'b1) //用 Dn来判断赋不同的值,1为亮,也就可以实现两个灯一起移动的选择

Out <=8'b00000001;

else

Out <=8'b00000011;

end

else begin

if (Out[0]==1'b1)//不用判断整个Out,只需要判断最边上的1,为1则表示需要改变方向,方向由Cn判断

Cn<=1'b1;

else if(Out[7]==1'b1)

Cn<=1'b0;

if (cnt1==1'b1) begin

if(Cn==1'b1)

Out<={1'b0,Out[0:6]};//右移

else

Out<={Out[1:7],1'b0};//左移

end

end

endmodule

利用两个循环,用cnt1代表到1s时间

反思和易错点

- 管脚位置需要到网上查询清楚,并不是呈顺序分布,可以参考其他博主的说明书

- 该灯可以选择两个灯一起移动,但是赋值的时候不可多次任意赋值,可能会出问题

- 可以使用ModelSim进行仿真

- 使用无阻塞的<=赋值

1798

1798

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?