目录

一、准备实验软件和开发板

本次实验所用到的软件有:quartus、modelsim(可选)

quartus下载链接: https://pan.baidu.com/s/1QSVbJ9TXbsGq1WtT8VzQUA?pwd=d7gt 提取码: d7gt

注:这链接里面是一个pdf,是quartus的下载教学,modelsim我暂时没有下载链接。

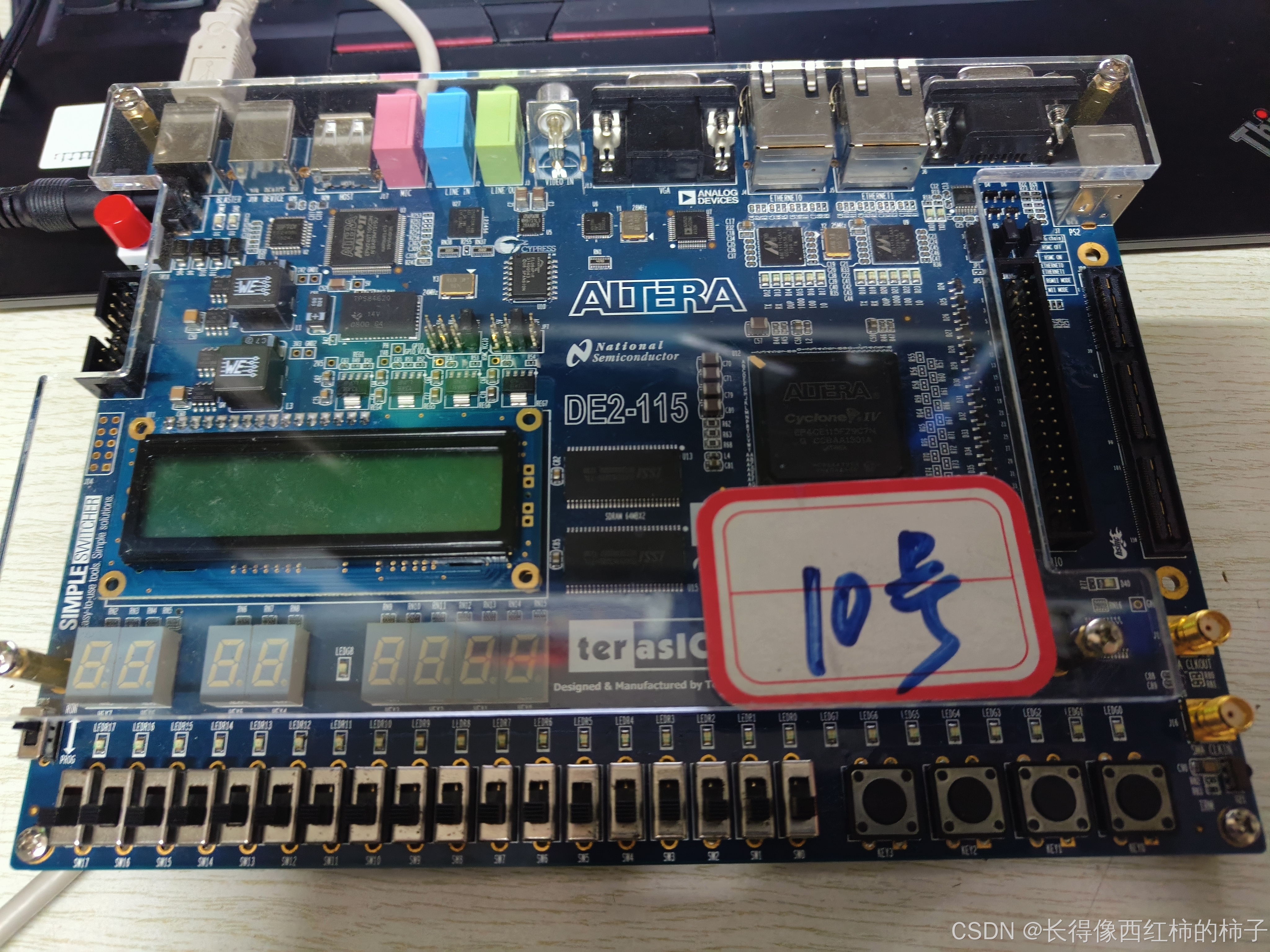

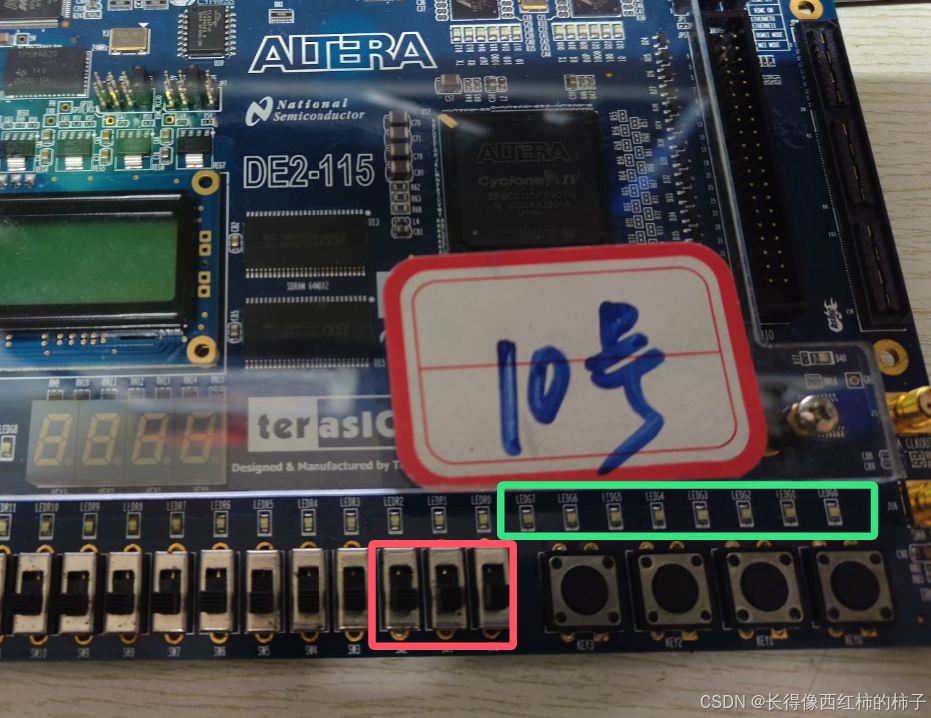

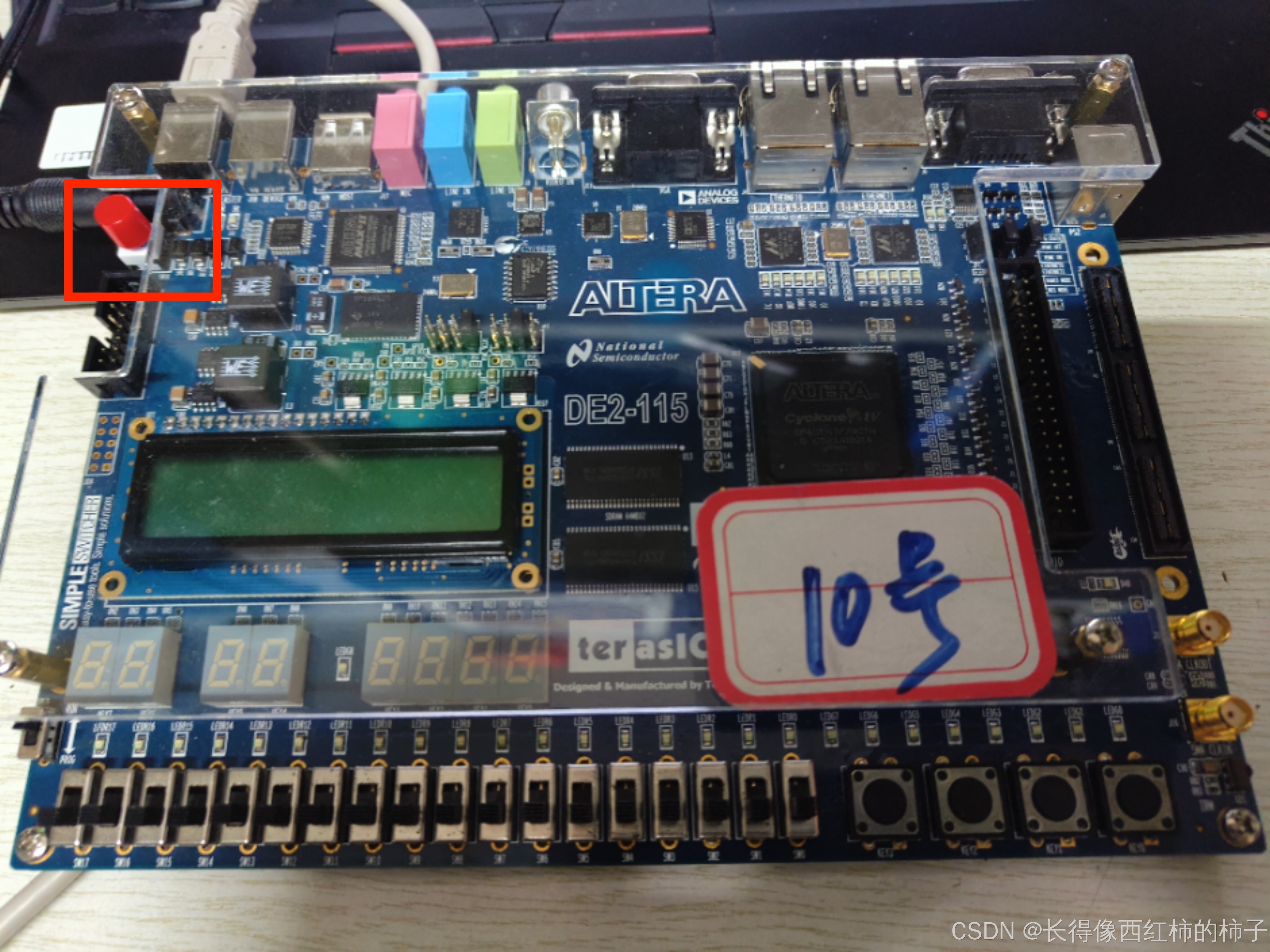

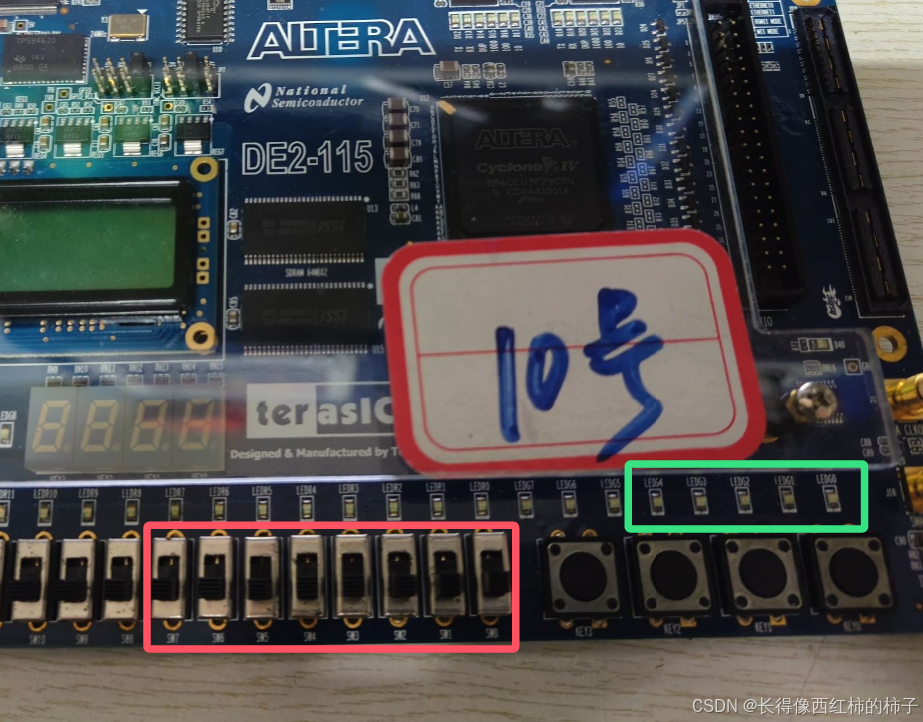

开发板:DE2-115开发板

二、实验过程

1、三八译码器

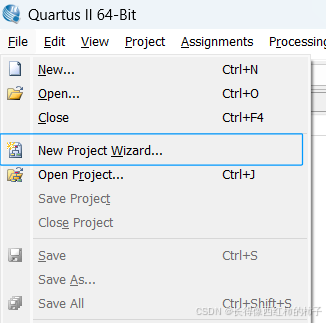

1、配置quartus工程文件

打开Quartus,选择File->new Project Wizard...

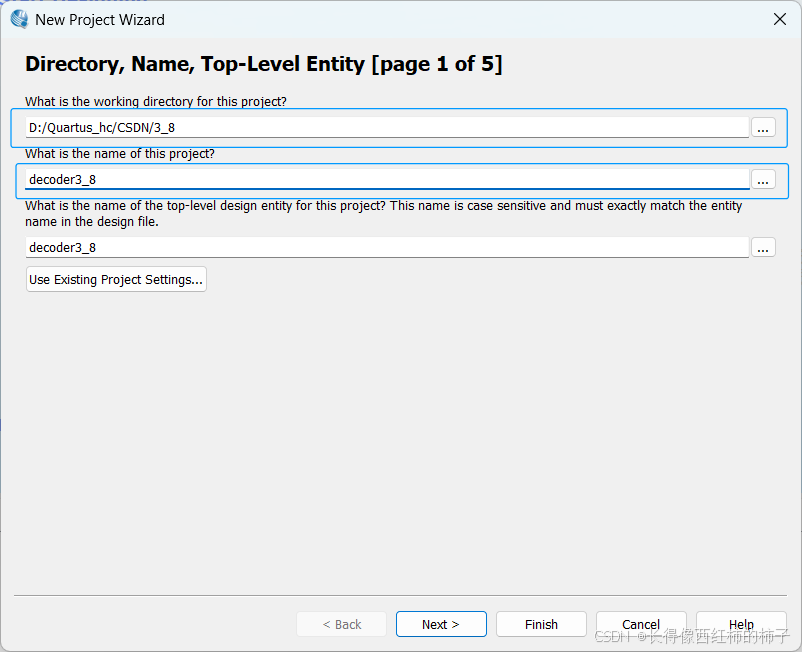

在第一排设置文件存储位置,第二排设置文件名。注:文件路径和名字不能存在中文

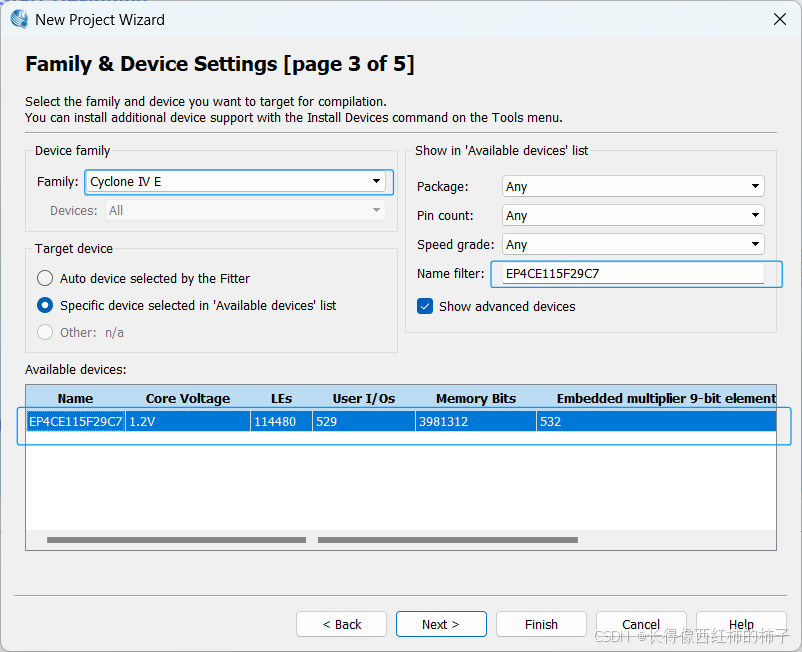

Family处选择Cyclone IV E,Name filter处输入EP4CE115F29C7,然后选择下方的同名芯片就是DE2-115中的芯片

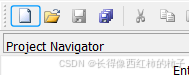

然后点击Finish后找到左上角的创建新文件

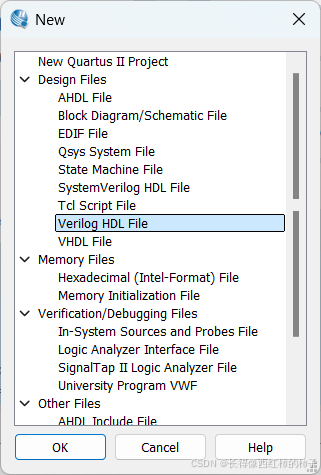

找到并点击Verilog HDL File

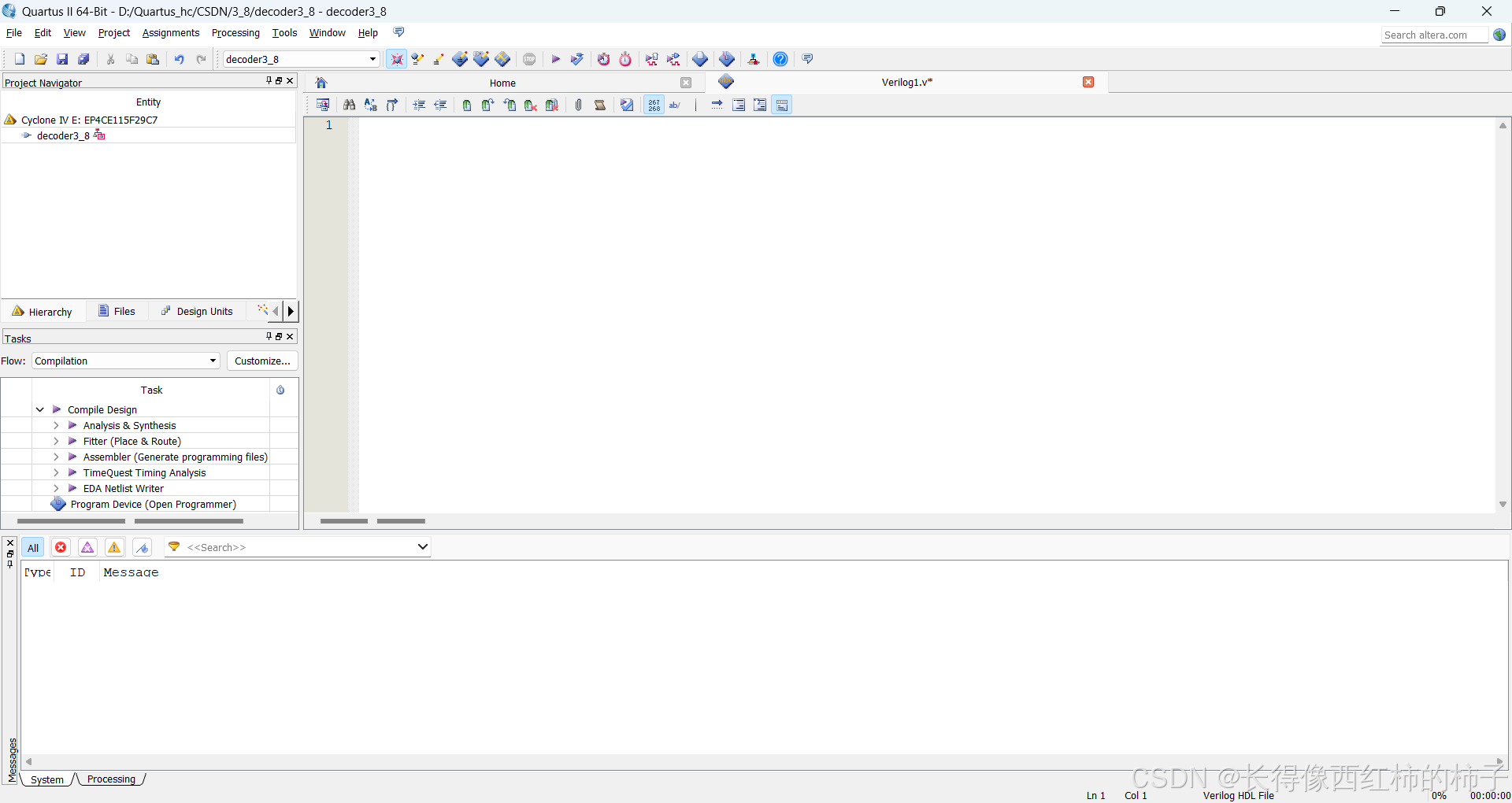

然后就会出现下图

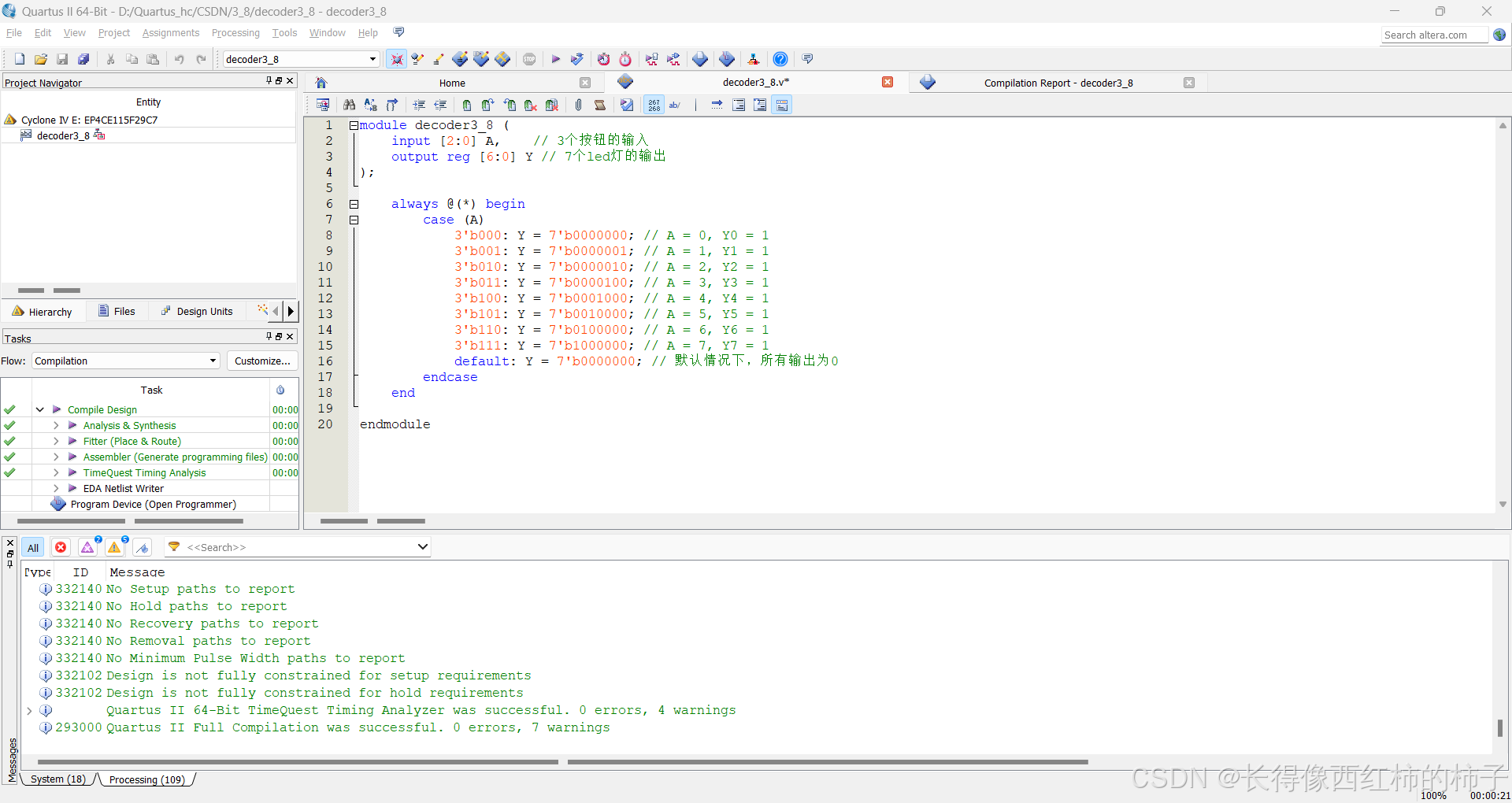

2、敲写代码

在其中复制进以下代码:

module decoder3_8 (

input [2:0] A, // 3个按钮的输入

output reg [6:0] Y // 7个led灯的输出

);

always @(*) begin

case (A)

3'b000: Y = 7'b0000000; // A = 0, Y0 = 1

3'b001: Y = 7'b0000001; // A = 1, Y1 = 1

3'b010: Y = 7'b0000010; // A = 2, Y2 = 1

3'b011: Y = 7'b0000100; // A = 3, Y3 = 1

3'b100: Y = 7'b0001000; // A = 4, Y4 = 1

3'b101: Y = 7'b0010000; // A = 5, Y5 = 1

3'b110: Y = 7'b0100000; // A = 6, Y6 = 1

3'b111: Y = 7'b1000000; // A = 7, Y7 = 1

default: Y = 7'b0000000; // 默认情况下,所有输出为0

endcase

end

endmodule然后点击编译

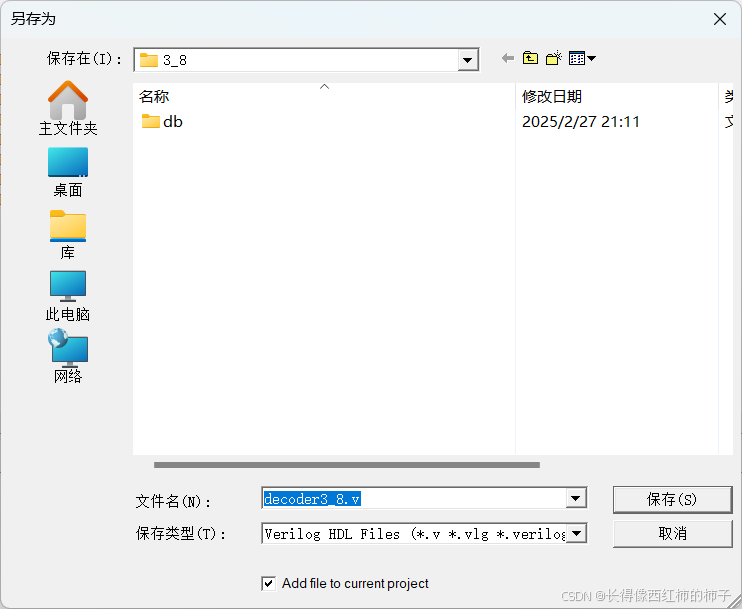

将该文件保存到你建立的文件夹下。注:module后的名称必须和你保存的文件名一致

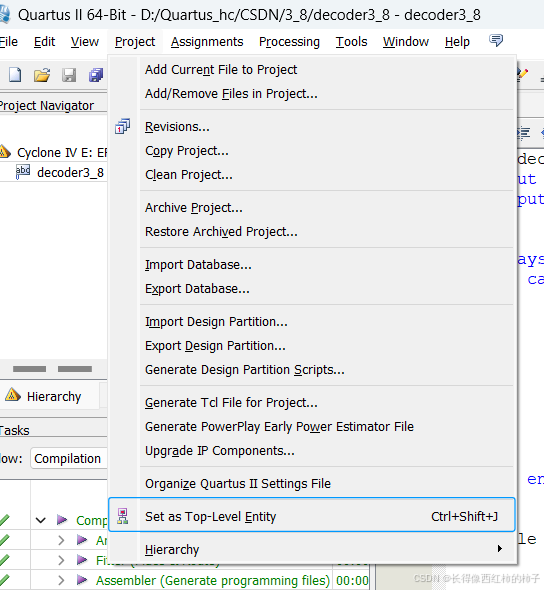

若编译失败,原因可能很多,我提供一个可能原因:没默认设置顶部实体,找到下图位置点击即可解决

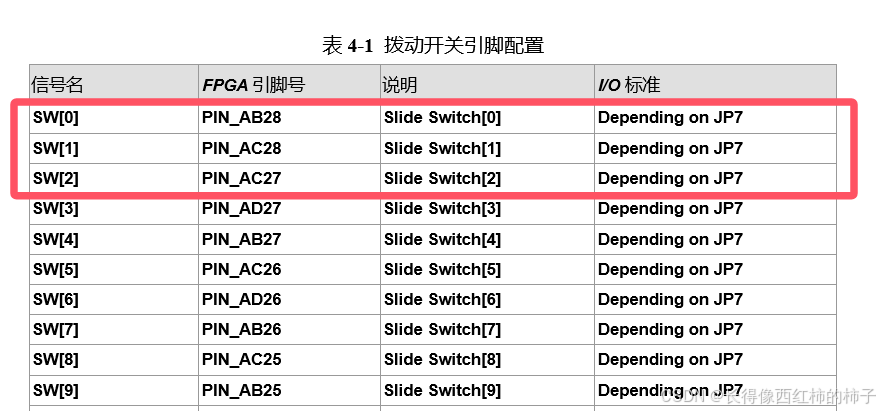

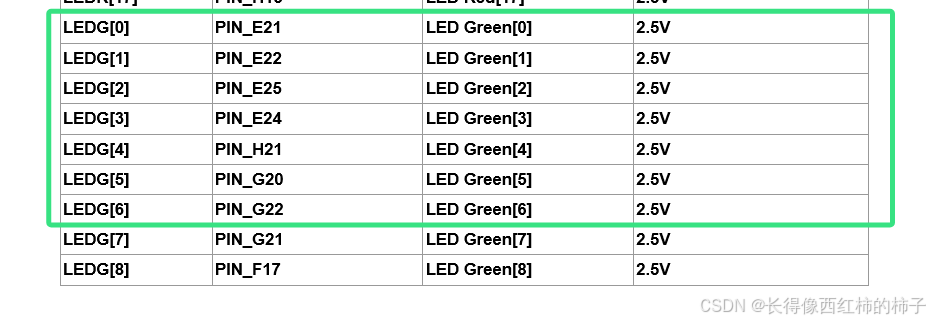

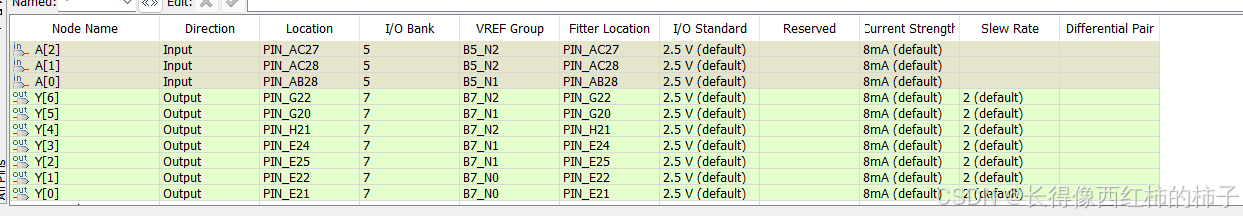

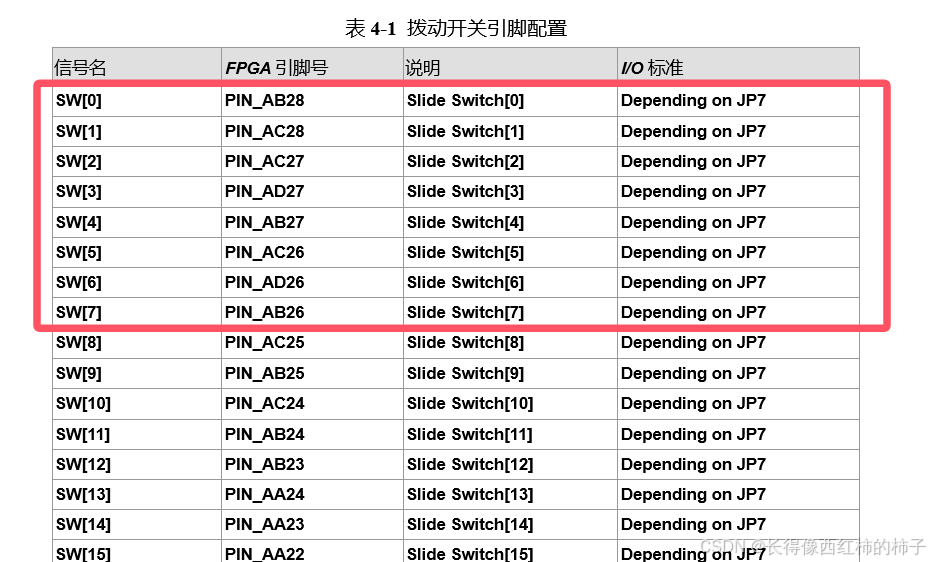

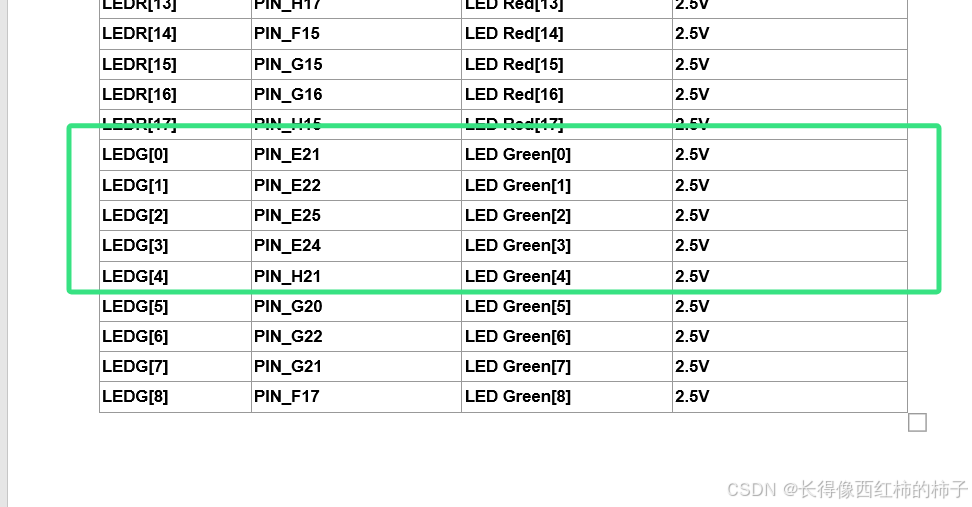

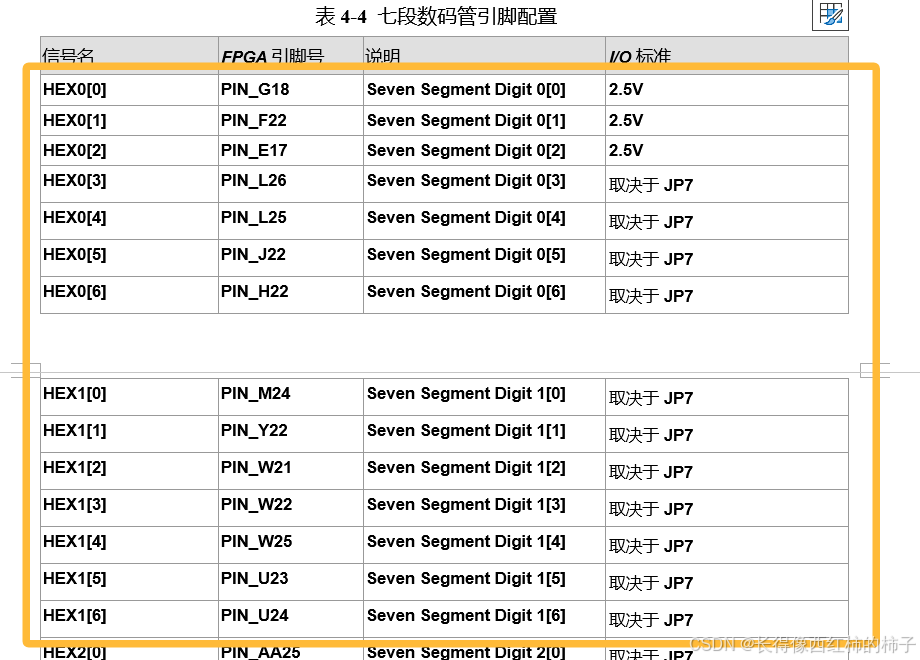

3、查表并配置引脚

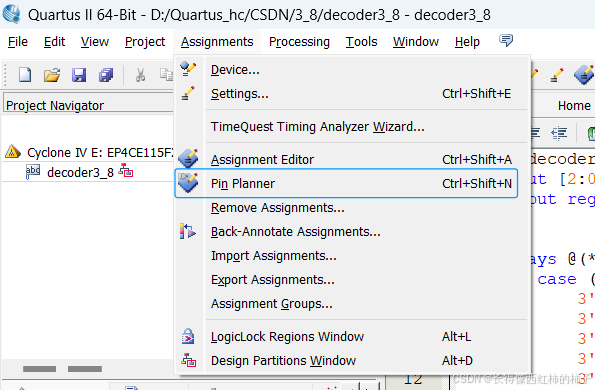

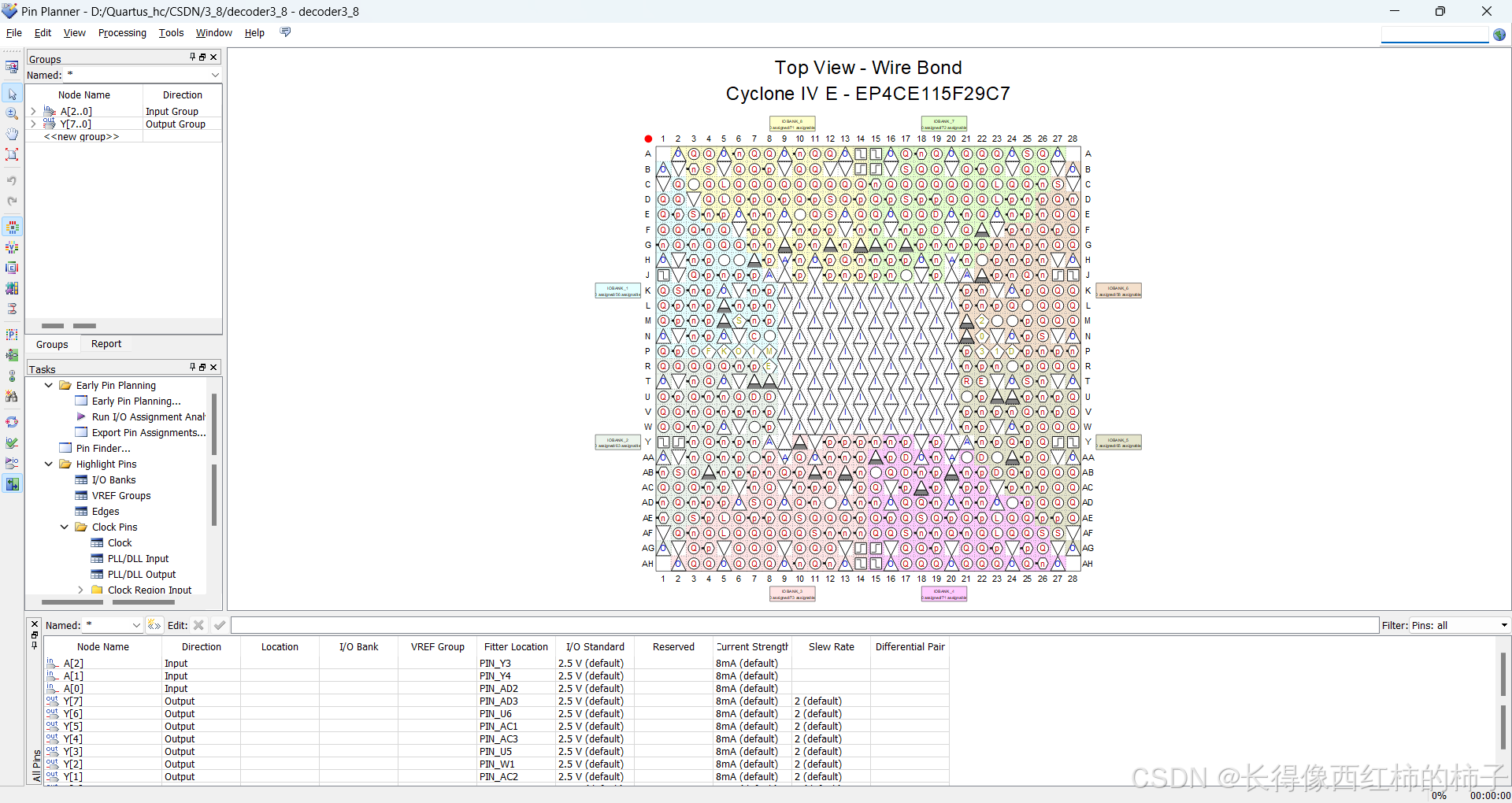

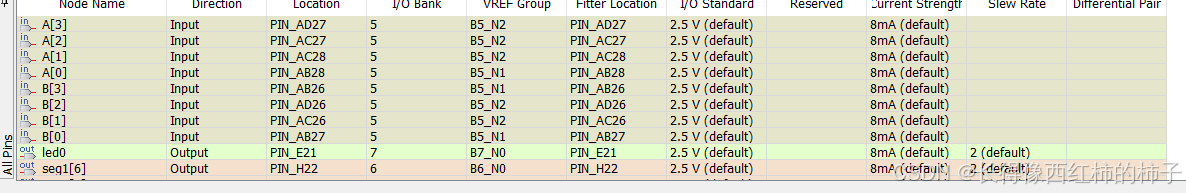

找到并点击Assignments->Pin Planner

接下来会跳转置这个界面

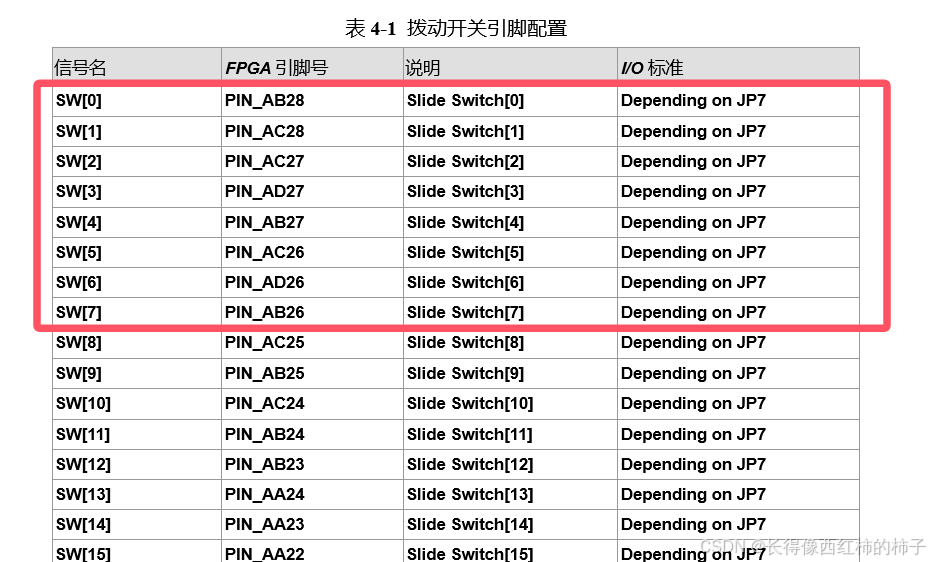

现在我们先规划一下引脚设置

三八译码器要用到3个按钮和7个led灯

我们可以选择

通过查表我们可以得知这3个按钮和8个led灯在芯片中的引脚号

DE2-115的中文手册链接我也放这儿了:

https://pan.baidu.com/s/11giuzmLEX3d7Vp74Es7PAw?pwd=89fy 提取码: 89fy

按照查表结果,给对应的输入输出位置设置引脚

设置完后再编译一次

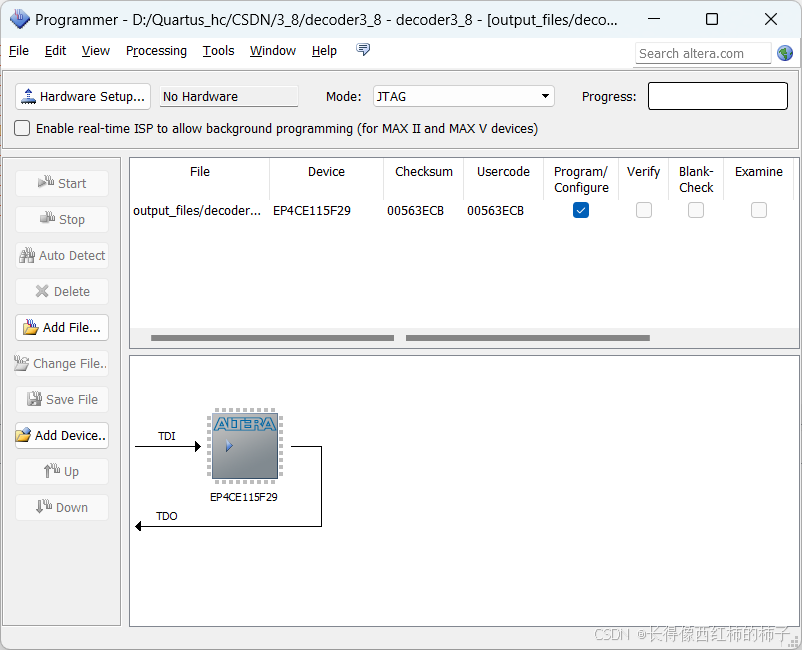

4、烧录

找到并点击上方的烧录按钮

跳转置下图界面

打开DE2-115开发板电源

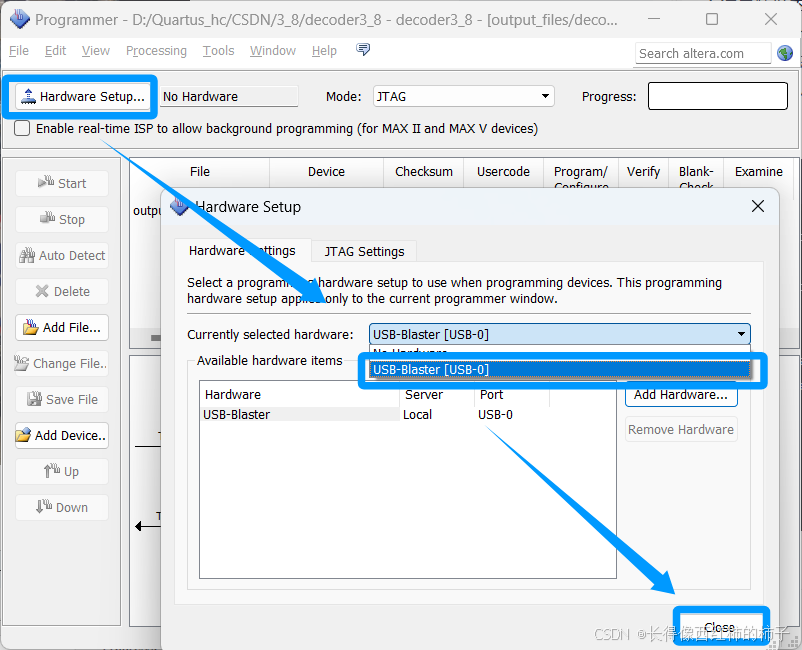

按照下图顺序设置

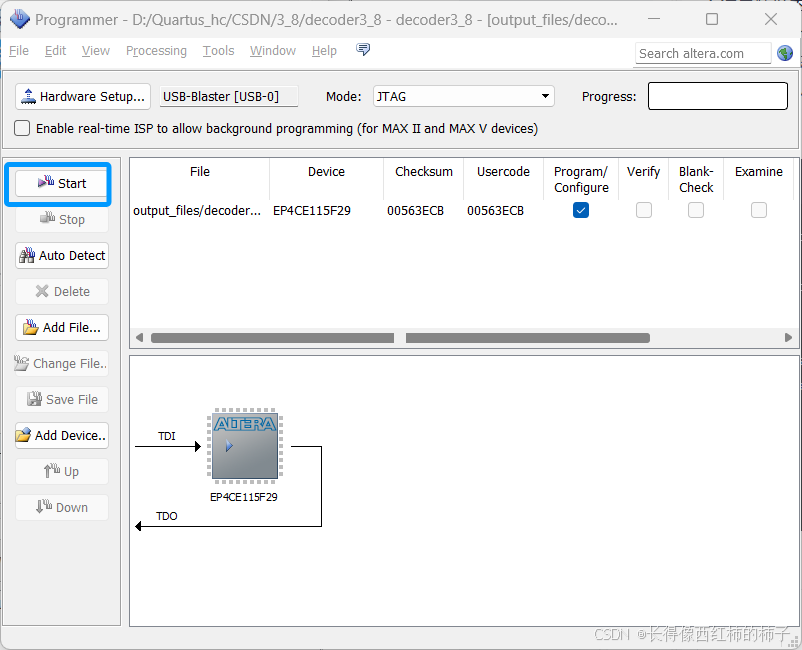

点击start

在烧录过程中可能出现俩个问题:

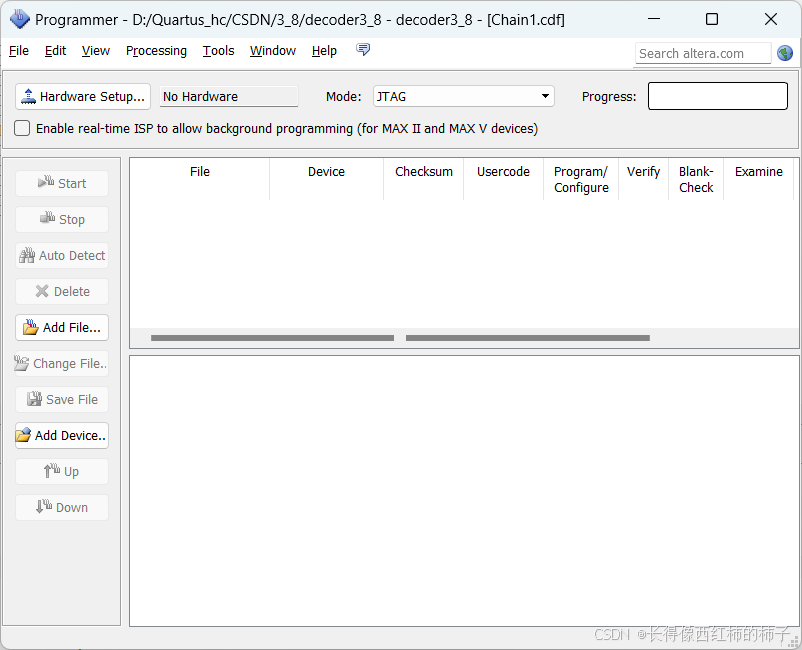

1、如下图中没出现芯片。解决方法:重新打开项目文件。

2、没有安装驱动。问题解决方法:

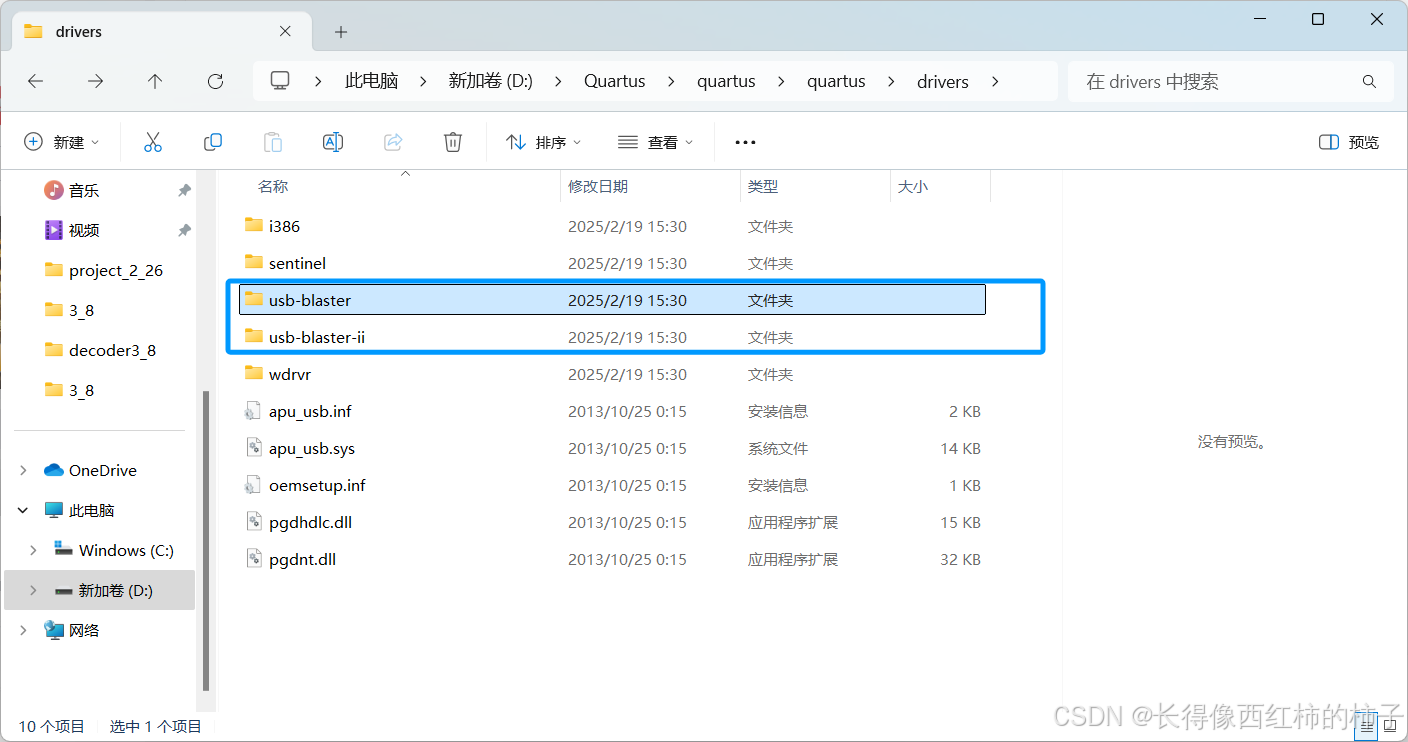

打开电脑的设备管理器,找到DE2-115开电后显示感叹号的位置,点击安装驱动,在本机有的驱动中选择,在quartus软件文件中找到驱动,位置在下图中,选择俩个其中的一个即可,若一个不行就选另一个。

5、实验结果

2、四位全加器

新建立一个项目,步骤按照三八译码器步骤即可

1、敲写代码

module a4_ (

input [3:0] A, // 四位数 A

input [3:0] B, // 四位数 B

output reg [4:0] seg1

);

wire [4:0] sum;

assign sum = A + B;

always@(*)

seg1 = sum;

endmodule编译后进入下一步

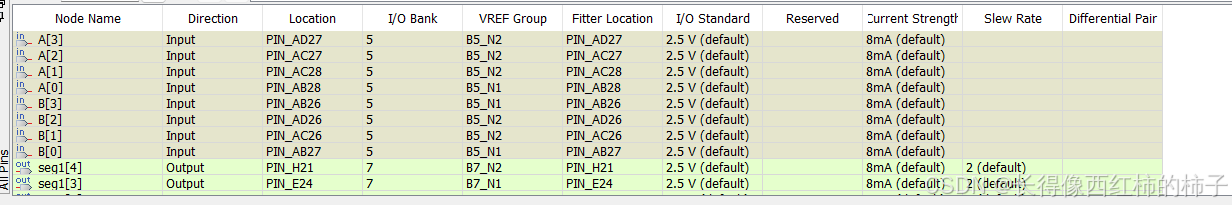

2、查表并配置引脚

四位加法器要用到8个按钮和5个led灯

我们可以选择

通过查表我们可以得知这8个按钮和5个led灯在芯片中的引脚号

将对应引脚填入

编译一遍后进入下一步

3、烧录后结果

3、四位全加器结果在七段数码管显示

新建立一个项目,步骤按照三八译码器步骤即可

1、敲写代码

module decoder3_8 (

input [3:0] A, // 四位数 A

input [3:0] B, // 四位数 B

output reg [6:0] seg1, // 第一个数码管显示

output reg [6:0] seg2, // 第二个数码管显示

output led0

);

wire [4:0] sum; // 5位,用于存放 A+B 的结果

reg [3:0] tens, units; // 结果的每一位

// 计算 A 和 B 的和

assign sum = A + B;

assign led0 = 1'd1;

// 将和分解为四个十进制位

always @(*) begin

tens = (sum % 100) / 10;

units = sum % 10;

// 将每一位数编码为7段数码管

seg2 = ~to_7seg(tens);

seg1 = ~to_7seg(units);

end

// 从4位二进制到7段数码管的编码转换

function [6:0] to_7seg(input [3:0] num);

case(num)

4'd0: to_7seg = 7'b0111111; // 0

4'd1: to_7seg = 7'b0000110; // 1

4'd2: to_7seg = 7'b1011011; // 2

4'd3: to_7seg = 7'b1001111; // 3

4'd4: to_7seg = 7'b1100110; // 4

4'd5: to_7seg = 7'b1101101; // 5

4'd6: to_7seg = 7'b1111101; // 6

4'd7: to_7seg = 7'b0000111; // 7

4'd8: to_7seg = 7'b1111111; // 8

4'd9: to_7seg = 7'b1101111; // 9

default: to_7seg = 7'b0000000; // Off

endcase

endfunction

endmodule编译一遍后进入下一步

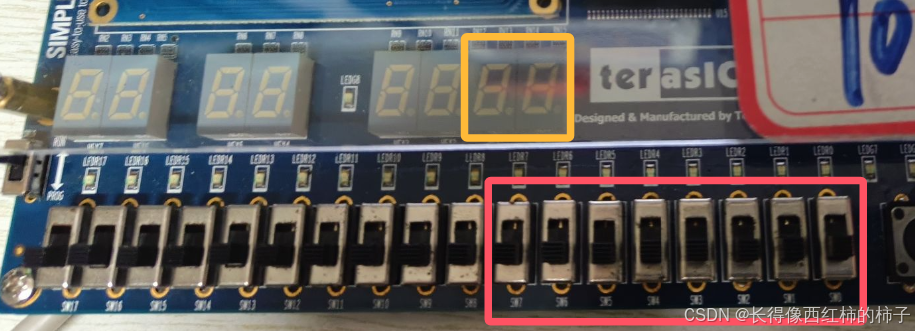

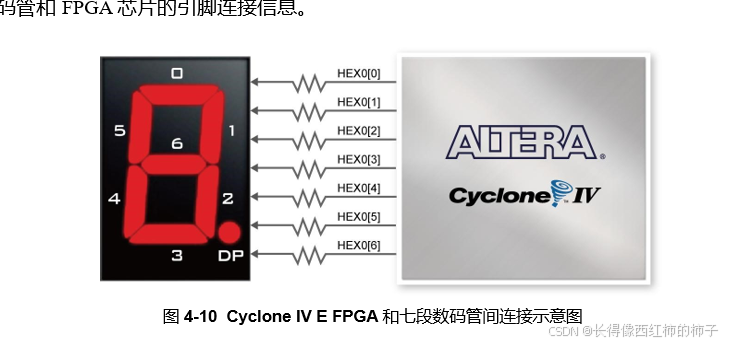

2、查表并配置引脚

四位全加器结果在七段数码管显示

要用到8个按钮和俩个七段数码管

我们可以用

通过查表我们可以得知这8个按钮和俩个七段数码管在芯片中的引脚号

将对应引脚填入

编译一遍后进入下一步

3、烧录后结果

三、号召

这次实验教学在网上有很多,但我在做的过程中遇到的部分问题,在其他博客中没有提出,所以我想做一个总体的解决在这个实验中出现的问题的博客,如果c友在实验中遇到了问题,可以来博客下留言或者私信我,我可以帮你看看,然后把问题解决方式增加到博客中。

4078

4078

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?