MATLAB仿真定点数转浮点数

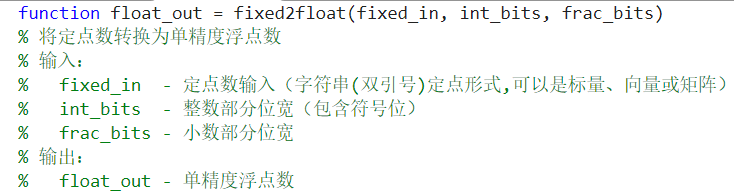

定点数可设置位宽,小数位宽;浮点数是单精度浮点数

对比VIVADO定点转浮点

目录

前言

在FPGA上实现算法时,相比MATLAB实现往往需要更长的开发周期,且调试过程更为复杂。因此,可以先用MATLAB对基于FPGA的定点和浮点运算的算法进行仿真验证,只要仿真结果正确,在FPGA上实现时通常只需解决资源和时序问题即可。笔者在仿真算法时,需要模拟一个定点转浮点的IP核功能,为此专门编写了MATLAB定点转浮点转换函数。本文将对此进行介绍。

创作不易,有用请一键三连!

一、定点数

之前的文章Vivado IP核之定点数转为浮点数Floating-point_vivado 浮点数-CSDN博客介绍过VIVADO定点转浮点IP核的使用,笔者在仿真算法时用MATLAB编写了一个模拟VIVADO IP核定点转浮点的函数,本文再说明一下。

定点数(Fixed-Point Number)是一种在计算机中表示实数的方法,有符号定点数是一种可以表示正数、负数和零的数值格式,其特点是小数点的位置固定,以补码形式存储,并通过最高位(符号位)区分正负(0为正,1为负),其余位按约定分配整数和小数部分。与浮点数(Floating-Point)不同,定点数不需要存储指数部分,因此计算更简单、速度快,但范围和精度相对固定。

工程师常用 Qm.n 表示定点数格式:m = 整数位数(含符号位)n = 小数位数,总位数 = m + n。

例如Q3.4表示的a=8‘b01100100,其代表的十进制数是6.25。Q3.4表示的b=8‘b10011100,其代表的十进制数是-6.25。

二、浮点数

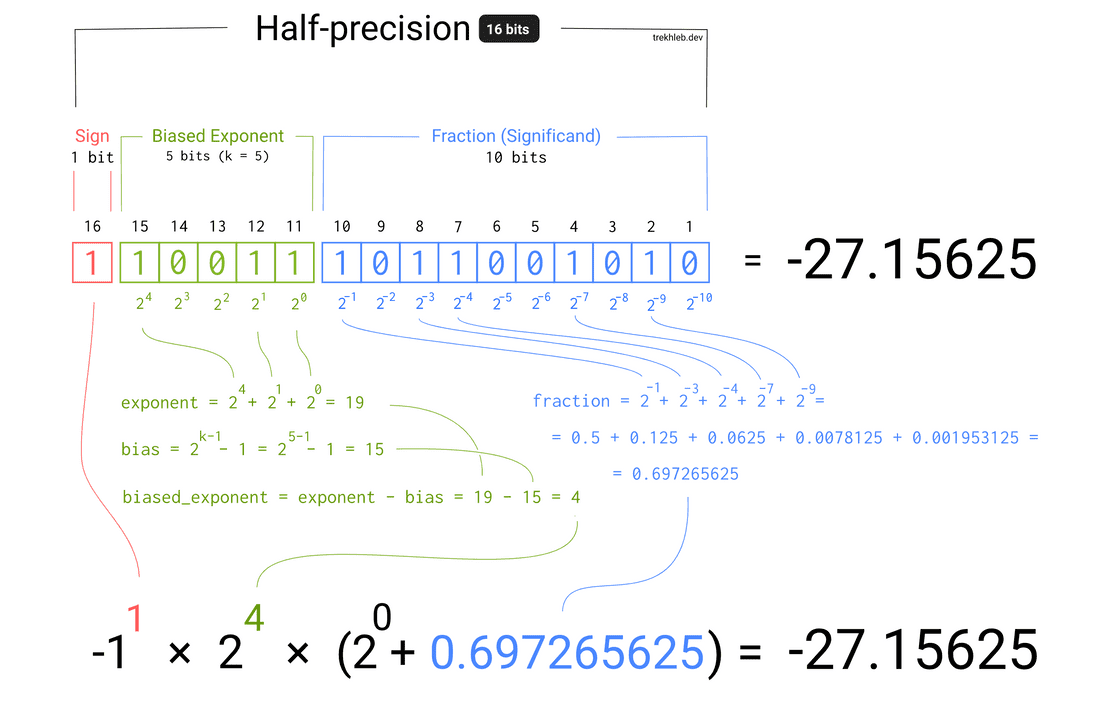

一个浮点数可以这样表示:浮点数的实际值等于符号位(sign bit)乘以指数偏移值(exponent bias)再乘以分数值(fraction),其实就是科学计数法。浮点数表示方法中,不存在原码反码补码的转换,正负都是原码。常见的几类浮点数如下表所示:

| IEEE 754 半精度浮点数:16 位 | 符号 1 位,指数 5 位,尾数 10 位 | 范围 [-6.55 × 10⁴, -5.96 × 10⁻⁸] ∪ [5.96 × 10⁻⁸, 6.55 × 10⁴] |

| IEEE 754 单精度浮点数:32 位 | 符号 1 位,指数 8 位,尾数 23 位 | 范围 [-3.40 × 10³⁸, -1.18 × 10⁻³⁸] ∪ [1.18 × 10⁻³⁸, 3.40 × 10³⁸] |

| IEEE 754 双精度浮点数:64 位 | 符号 1 位,指数 11 位,尾数 52 位 | 范围 [-1.80 × 10³⁰⁸, -2.22 × 10⁻³⁰⁸] ∪ [2.22 × 10⁻³⁰⁸, 1.80 × 10³⁰⁸] |

下面是一个半精度浮点数 16 bit 浮点数计算过程的例子:

三、定点数转浮点数

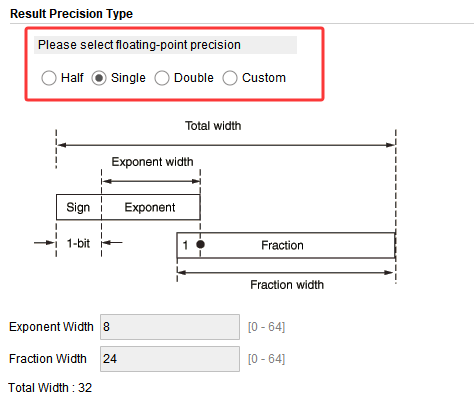

VIVADO中不仅支持半精度、单精度、双精度的浮点数,还支持自定义位宽的浮点数。

笔者要用到的算法是用单精度浮点数计算,所以本文以定点数转单精度浮点数为例进行说明。

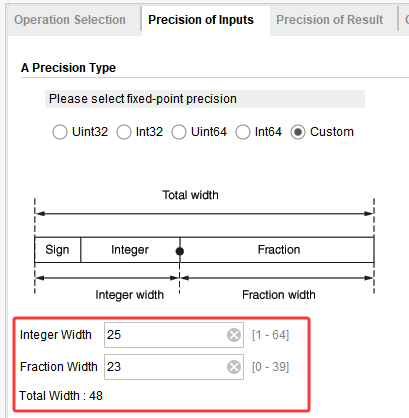

IP核中定点数设置如下:

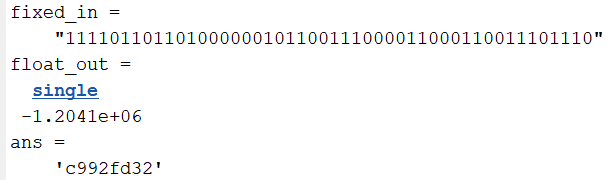

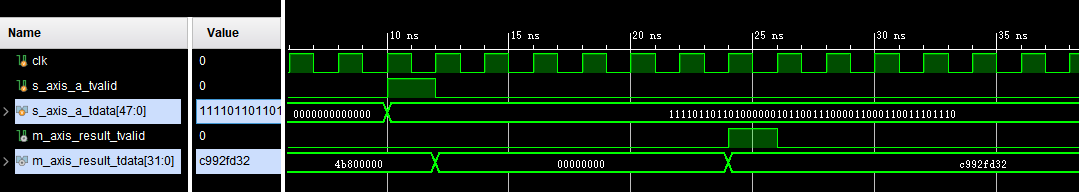

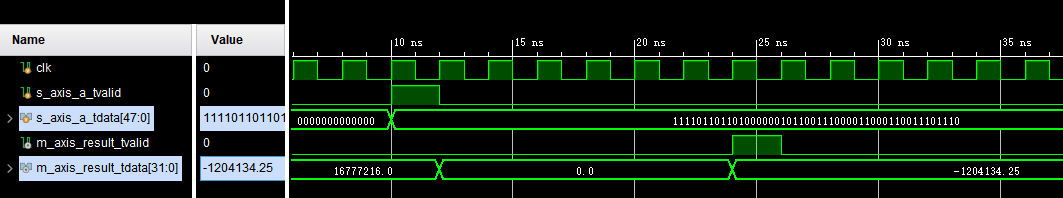

假设现在有一个48位的定点数,"111101101101000000101100111000011000110011101110",MATLAB和VIVADO的仿真结果如下,可见二者转换结果一模一样。

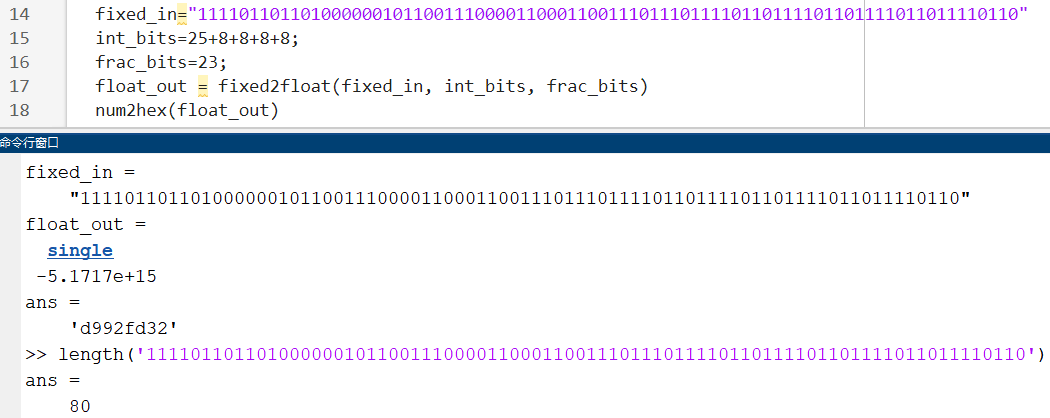

fixed_in="111101101101000000101100111000011000110011101110"

int_bits=25;

frac_bits=23;

float_out = fixed2float(fixed_in, int_bits, frac_bits)

num2hex(float_out)

其中fixed2float是自己编写的函数。

编写的该函数最大支持80位的定点数转换。

四、函数代码

需要该函数的可以去下载。

总结

以上就是本文的全部内容,MATLAB实现了定点转浮点函数。

832

832

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?