所谓边沿检测器,检测的是输入信号的变化,输入信号从0跳变到1,或者从1跳变到0。在verilog中边沿检测器非常常用且重要,比如启动信号的检测、数据有效信号的检测、将边沿信号转成脉冲信号等等。对于此类的检测器,我们一般的方法是将in信号往后延迟一个周期得到in_reg,然后利用这两个信号之间的逻辑关系生成对应边沿显示信号。

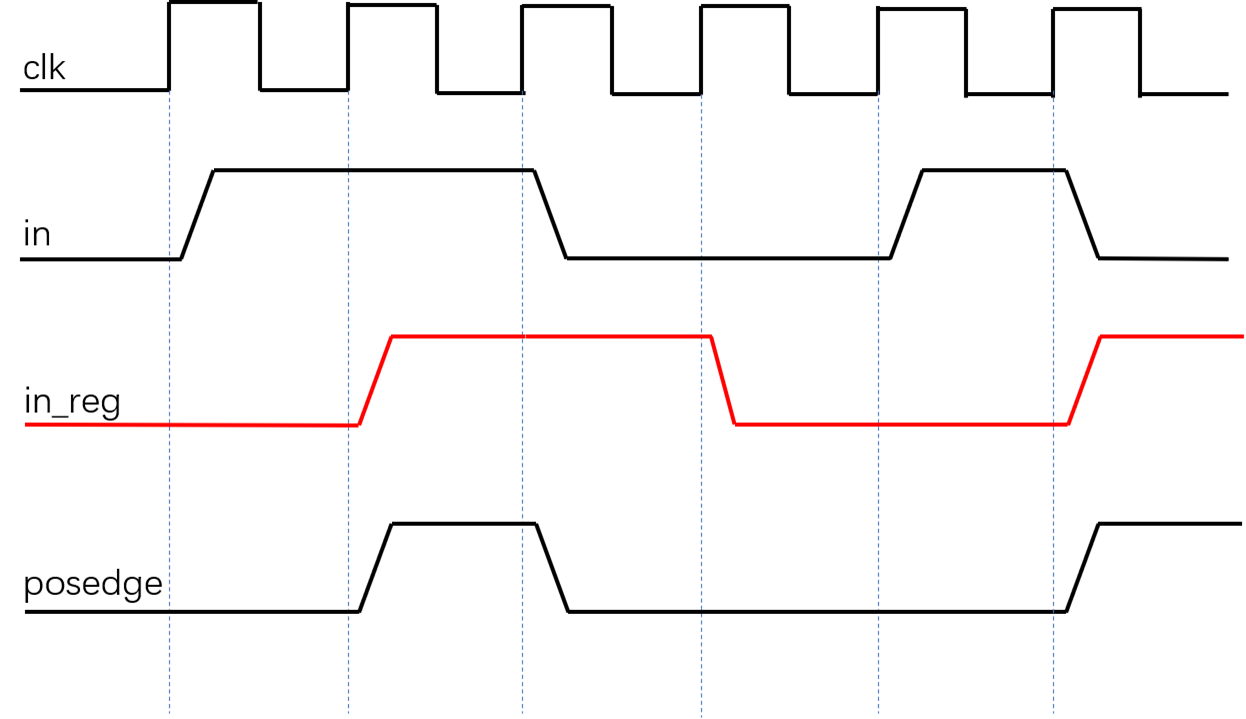

上升沿检测器:如下图所示,在in信号拉高后的下一个时钟上升沿,边沿检测信号posedge被拉高,一个周期后拉低,如此反复。可以发现在posedge被拉高的时钟上升沿,in==1,in_reg==0,想要他们通过组合逻辑产生1,有in&~in_reg, in|in_reg, in^in_reg,但是后者这在in的下降沿也能够使posegde拉高,所以不合适。

module posedgedetect;

input clk

input [x:0]in;

output [x:0]posedge;

reg [x:0]in_reg;

always@(posedge clk)

begin

in_rge <= in;

end

always@(posedge clk)

begin

posedge <= in&~in_reg;

end

endmodule

下降沿触发器:与上升沿类似在in信号拉低后的一个时钟上升沿,检测信号ne

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

786

786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?