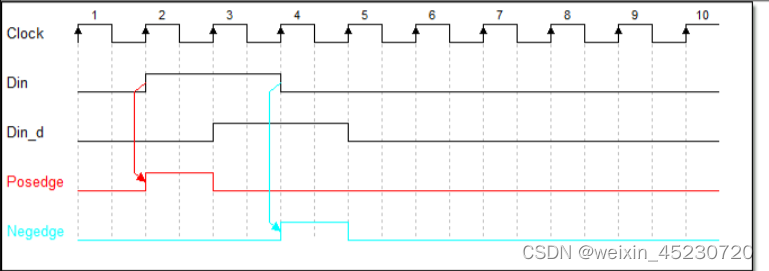

边沿检测分上升沿检测和下降沿检测

思路很简单,就是先对信号延迟一拍,再用组合逻辑对原信号和延迟信号判断

上升沿检测 din && ~din_d

下降沿检测 ~din && din_d

涉及到两个信号延迟一拍,优先考虑是不是边沿检测

module edge_detect(

input clk ,

input rst_n ,

input key_in ,

output pos_edge ,

output neg_edge ,

output data_edge

);

reg [1:0] data_r ;

always @(posedge clk ,negedge rst_n) begin

if(!rst_n)begin

data_r[0] <= 0;

data_r[1] <= 0;

end

else

begin

data_r[0] <= key_in;

data_r[1] <= data_r[0];

end

end

assign pos_edge = data_r[0] & ~data_r[1] ; //上升沿检测

assign neg_edge = ~data_r[0] & data_r[1] ; //下降沿检测

assign data_edge = pos_edge | neg_edge ; //双边沿检测

endmodule

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?