目录

《lab2》

1.实验目标

通过完成本实验,您将能够:

- 配置处理系统(PS)的GP Master端口,以连接可编程逻辑(PL)中的IP。

- 向硬件设计中添加附加的IP核。

- 设置一些编译器设置。

2.实验步骤

2.1 打开项目:

- 打开之前的项目或从{labsolutions}目录中打开lab1项目,并将项目另存为lab2。

- 打开Block Design。

2.2 添加两个GPIO实例:

- 在Sources面板中展开system_wrapper,双击打开system.bd文件进入IP Integrator。

- 在设计中添加AXI GPIO IP核。

- 更改AXI GPIO的名称为"switches"。

- 配置AXI GPIO的接口和通道。

- 运行连接自动化以连接主从接口。

- 添加另一个GPIO IP核,并将其命名为"buttons"。

- 手动连接按钮GPIO IP核到AXI Interconnect。

2.3 分配地址和创建外部端口:

-

- 在Address Editor中为IP核分配地址。

- 将GPIO外部端口分配为开发板上的引脚。

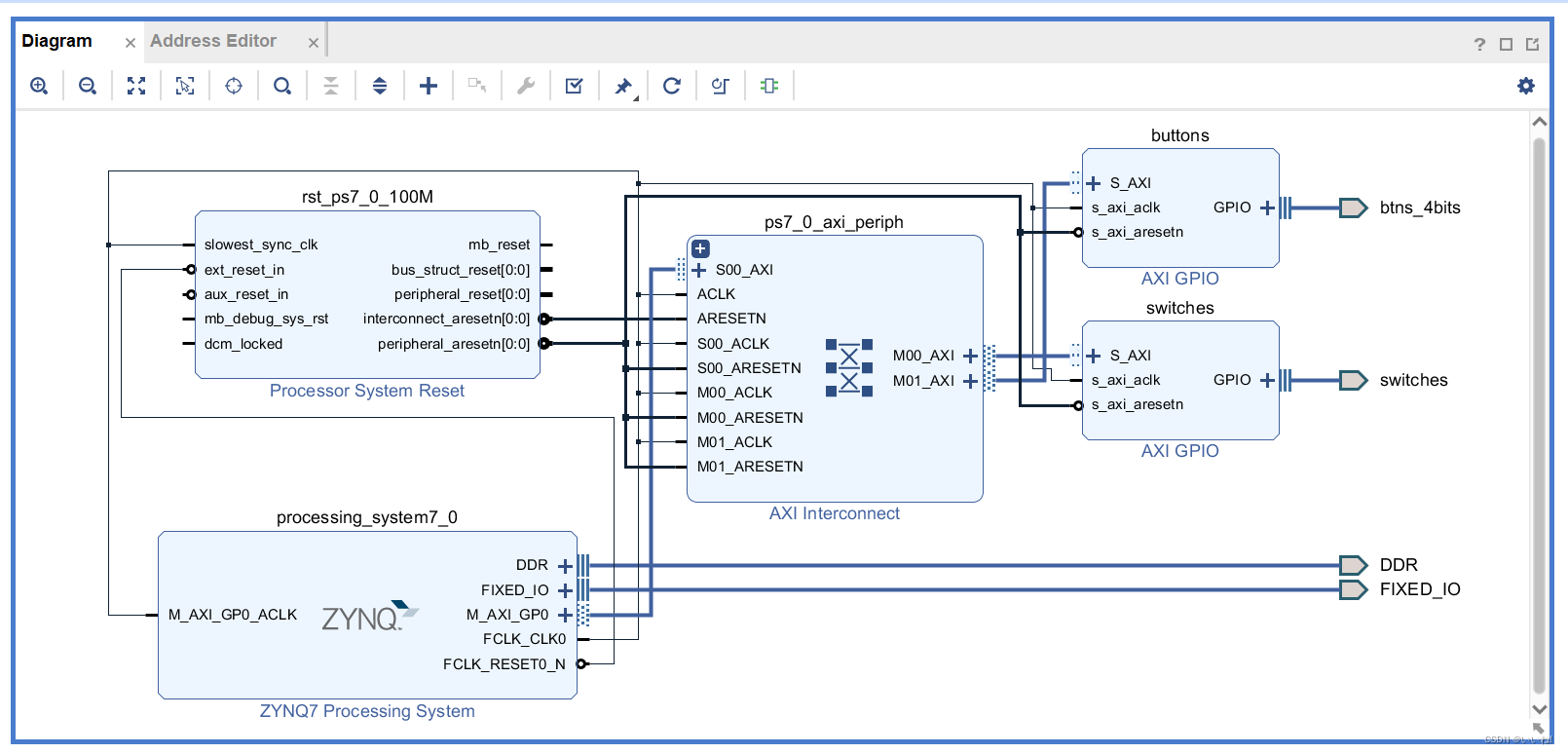

最终块设计如图:

图2.3-1 “块设计”

2.4 生成比特流和导出到SDK:

-

- 生成比特流。

- 导出硬件到SDK。

2.5 在SDK中生成测试应用程序:

-

- 创建新的应用程序项目。

- 导入lab2.c文件。

- 运行库生成器。

2.6 在硬件中测试:

-

- 连接开发板和计算机。

- 下载比特流和应用程序到开发板。

- 在终端中查看输出结果。

3.问题及解决方法

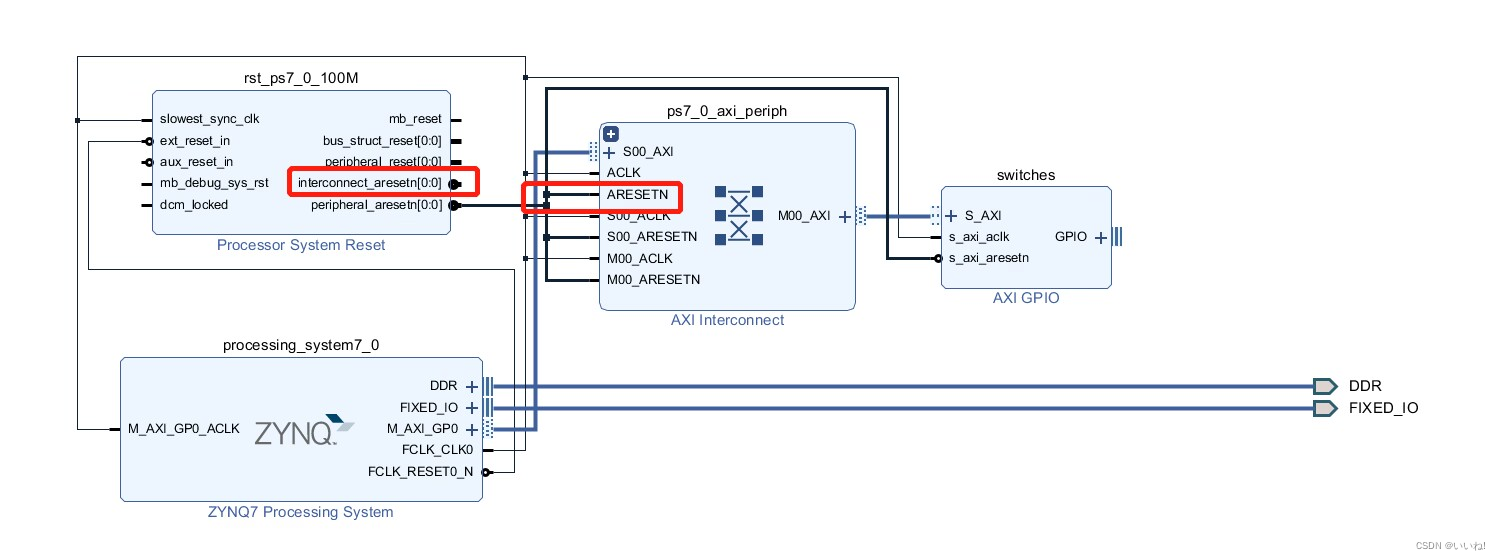

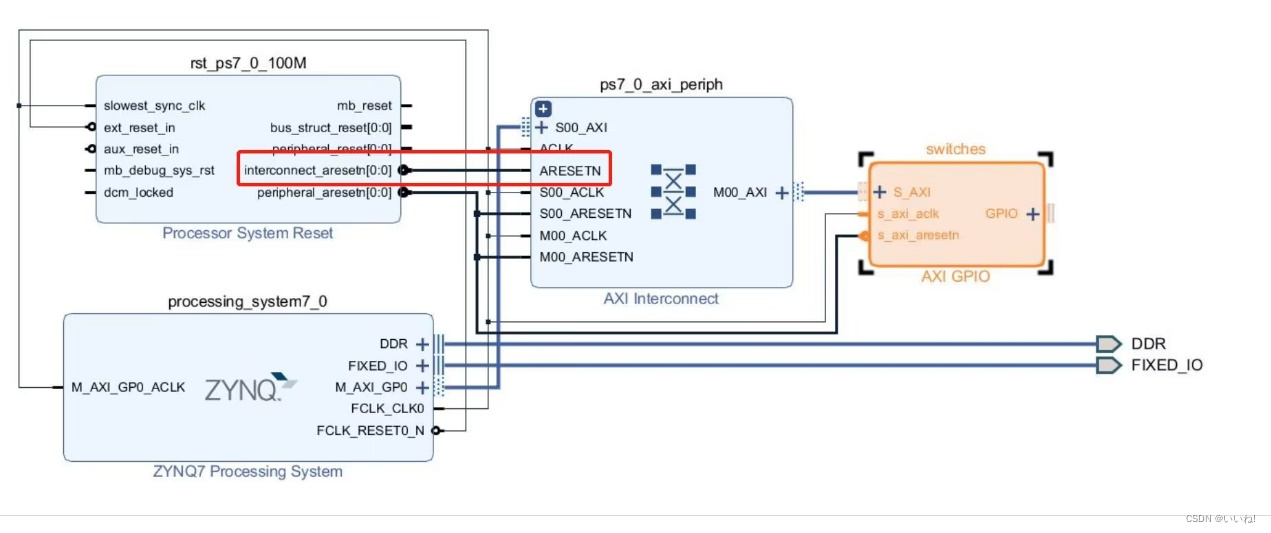

3.1 自动生成线路图时和教程中的不太一样,把自动生成的线路删除后手动连接而成

图3.1-1

图3.1-2

3.2 生成TestApp文件时,刚开始出现无法选择Use existing ,后面发现是没有仔细看教程,要先通过“Board Support Package”生成一个standalone_bsp_0

图3.2-1

4.调试

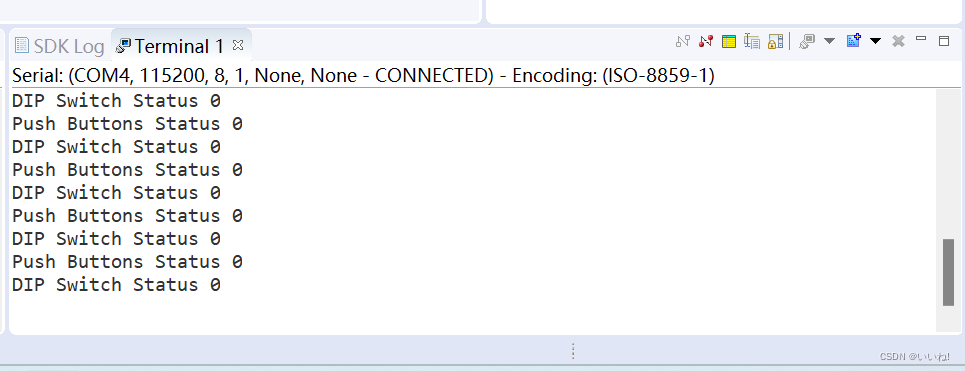

4.1 终端输出结果

输出结果:

图4.1-1

5.总结:

通过本次实验,可以更深入地了解Xilinx Vivado和SDK工具,以及FPGA开发的基本流程。首先需要我们配置处理系统(PS)的GP Master端口,将其连接到可编程逻辑(PL)中的IP。接下来,添加了两个GPIO实例,分别命名为"switches"和"buttons",并手动进行了连接。

通过在Address Editor中为IP核分配地址和创建外部端口,将GPIO外部端口与开发板上的引脚关联起来,为将来的硬件测试做好了准备。在生成比特流并将硬件导出到SDK之后,我创建了一个测试应用程序,导入了lab2.c文件,最终成功在硬件上进行了测试。最后连接了开发板与计算机,下载了比特流和应用程序,并查看了终端的输出结果。

在这个实验过程中,我也遇到了一些问题,例如手动连接线路和生成TestApp文件时的小障碍,但通过仔细阅读教程并按照指南一步步进行操作,便可以成功地解决这些问题。这个实验可以让我们更熟悉FPGA开发流程和工具,为未来的项目和实验奠定了坚实的基础。

6.附录

附录.1参考资料

[1] https://github.com/xupgit/Zynq-Design-using-Vivado/tree/master

56

56

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?