ⅰ.存储器容量的扩充

ⅱ.DRAM存储元的工作原理

ⅲ.DRAM芯片的逻辑结构

ⅳ.DRAM读/写时序

ⅰ.存储器容量的扩充

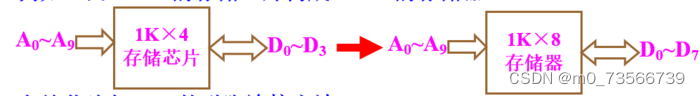

1.位扩展:按位扩充是扩大存储器的位数,其存储单元数目不变,每个单元的位数增加。

下面我们举例,使用1K×4位的存储芯片,按位扩充成为1K×8位的芯片。

2.字扩展:按字扩充就是芯片的存储单元存储的信息位数不变,但是存储单元的个数增加。

下面我们举例说明,1K×8位的芯片扩充成为2K×8位芯片。

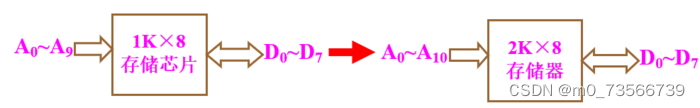

3.字位扩展:按字位扩充,每个单元位数和总单元的个数都增加,实际上就是按字扩充和按位扩充同时使用。

下面我们以1K×4位扩充成为2K×8位为例。

扩充方法:

首先进行按位扩充,形成满足位要求的芯片,再使用按字扩充,对芯片进行扩展。

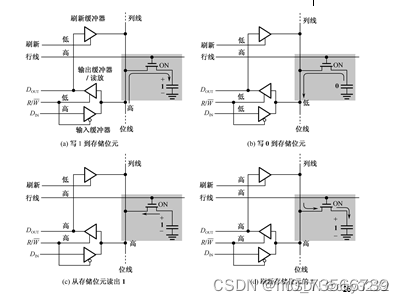

ⅱ.DRAM存储元的工作原理

DRAM是现在主流的内存形式。基本单元主要由一个晶体管和一个电容组成,电容中有电荷代表“1”,没有电荷代表“0”。由于电容中的电荷会随着时间而慢慢泄露,所以需要周期性地进行“充电”。

SRAM存储器的存储位元是一一个触发器,它具有两个稳定的状态。而DRAM存储器的存储位元是由一个MOS晶体管和电容器组成的记忆电路,如图所示

注意:输入缓冲器与输出缓冲器总是互锁的。这是因为读操作和写操作是互斥的,不会同时发生。

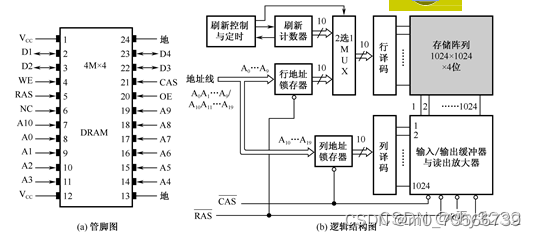

ⅲ.DRAM芯片的逻辑结构

与SRAM不同的是图中增加了行地址锁存器和列地址锁存器。由于DRAM存储器容量很大,地址线宽度相应要增加。这势必增加芯片地址线的管脚数目。为避兔这种情况,采取的方法是分时传送地址码:若地址总钱宽度为10位,先传送地址码A0~A9,由行选通信号RAS打入到行地址锁存器,然后传送地址码A10~A19,由列选通信号CRS打入到列地址锁存器。芯片内部两部分合起来。

ⅳ.DRAM读/写时序

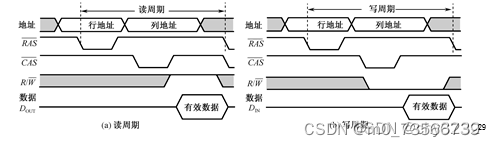

读周期、写周期的定义是从行选通信号RAS下降沿开始,到下一个RAS信号的下降沿为止的时间,也就是连续两个读周期的时间间隔。通常为控制方便,读周期和写周期时间相等。

读周期:行地址有效→行地址选通→列地址有效→列地址选通→数据输出

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?