广州大学学生实验报告

开课学院及实验室:计算机科学与工程实验室 2023年12月15日

| 学院 | 计算机科学与网络工程学院 | 年级/专业/班 | 计科221 | 姓名 | 学号 | ||

| 实验课程名称 | 数字逻辑与计算机组成实验 | 成绩 | |||||

| 实验项目名称 | 实验4 CPU指令设计实验 | 指导老师 | |||||

一、实验目的

1、理解指令类型与指令格式之间的关系,掌握取指部件、指令解析和立即数扩展器的设计方法。

2、理解随机访问存储器 RAM 和只读存储器 ROM 的操作原理。

3、理解每条目标指令的功能和数据通路,掌握单周期处理器的控制器设计方法。(选做)

二、实验要求

1、电路图合理布局,适当添加标识符和注释文字,便于理解;

2、利用仿真测试,验证电路功能正确;

3、根据本次实验内容的要求,给出实验操作步骤,包括必要的电路原理图、实验结果、功能测试、错误现象及原因分析等内容写入实验报告。

4、 将实验报告和电路图.circ文件上交,文件名为学号,如200640001.docx、200640001.circ,所有题目的电路合在一个文件中。

三、参考资料

《实验教程》:实验5 取指令部件设计,实验6 单周期CPU设计与测试。

三、实验内容

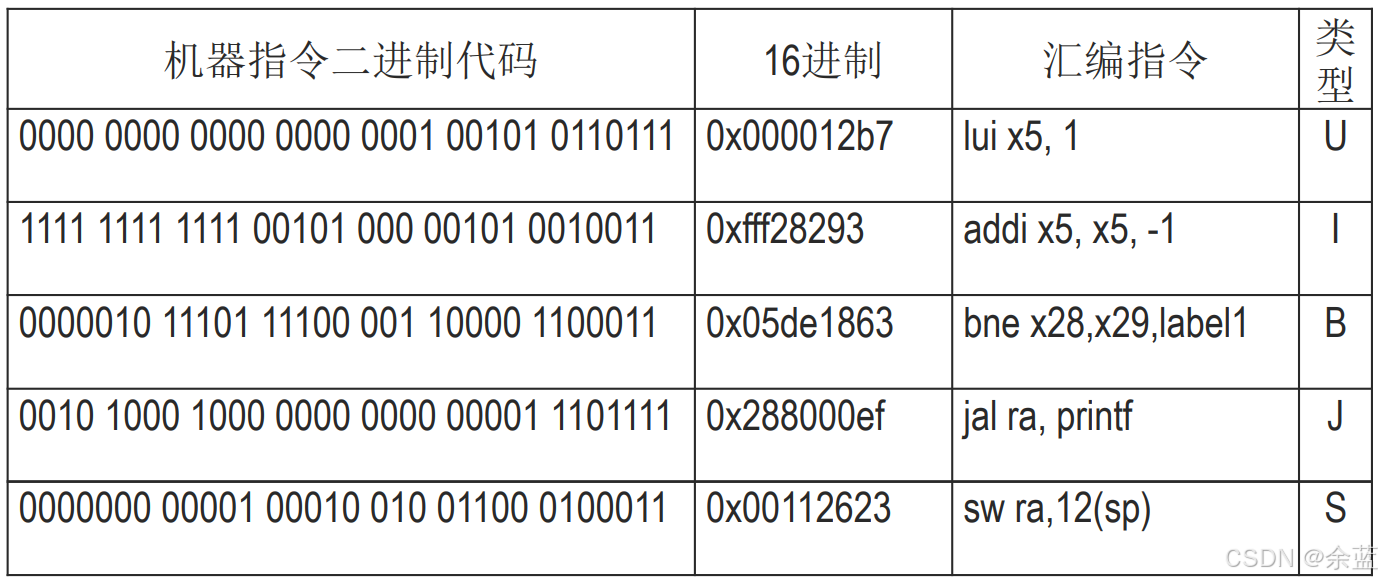

1、实验测试指令数据的准备

从指令存储器的地址第12单元开始,依次写入以下5条机器指令:

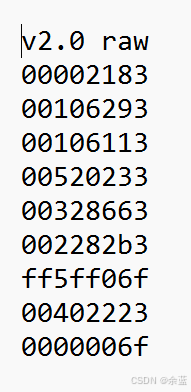

自行编写数据镜像文件,然后导入存储器。

数据镜像文件格式要求:首行以v2.0 raw开头,下一行开始存放数据,数据位宽为32位时,每一个位置存放4个字节的数据,以空格或回车隔开。连续相同的重复数字可简化表示,如12*0,表示连续12个0。

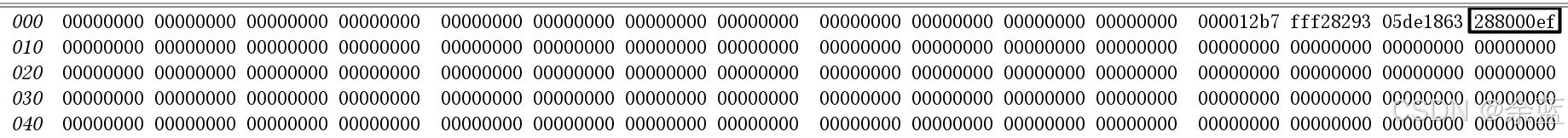

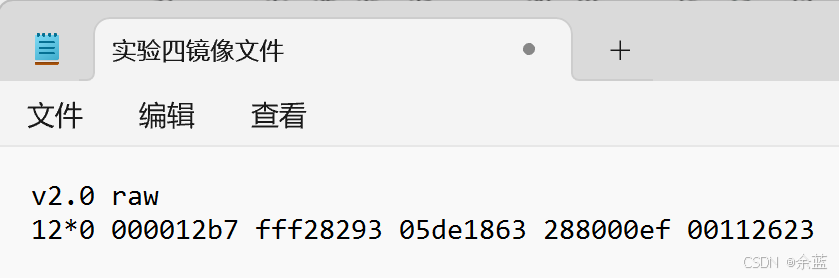

代码镜像文件示例:

v2.0 raw

12*0 000012b7 fff28293 05be1863 288000ef 00112623

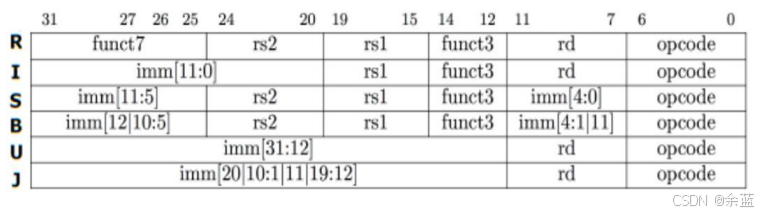

已知RISC-V指令格式如图所示:

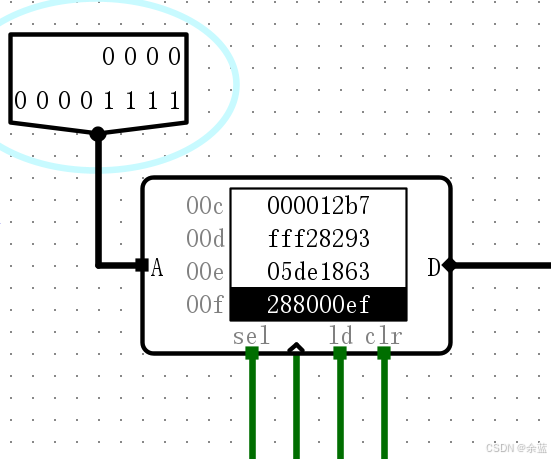

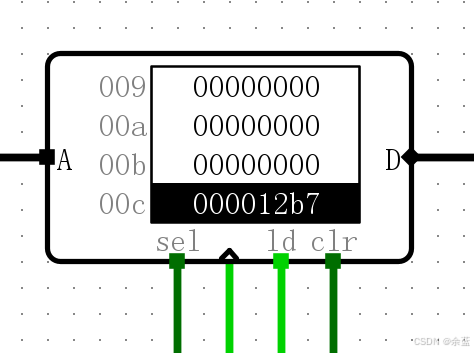

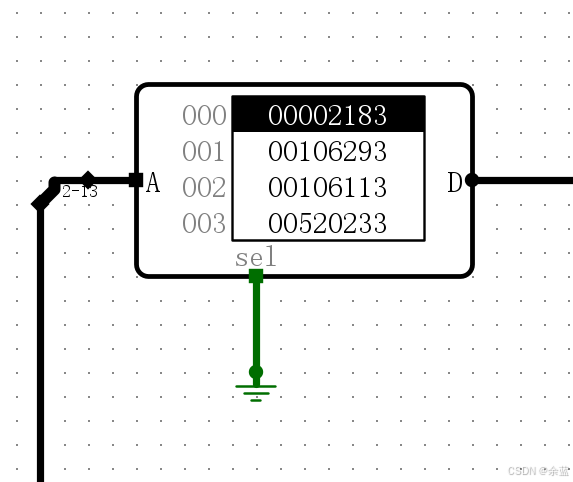

如图,选择第12号单元(00C),写入表格中的数据。

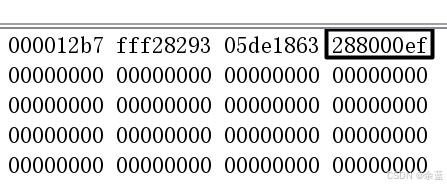

接着,把这些数据保存,存为镜像文件,打开后的效果如下图。

现测试一下,文件是否已经写入存储器中,测试效果如下。

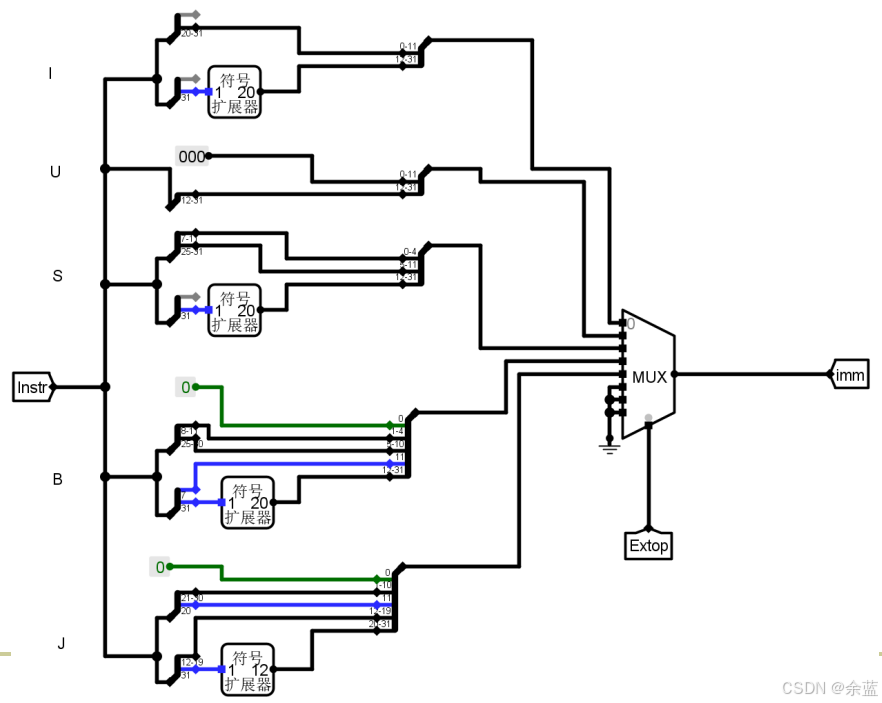

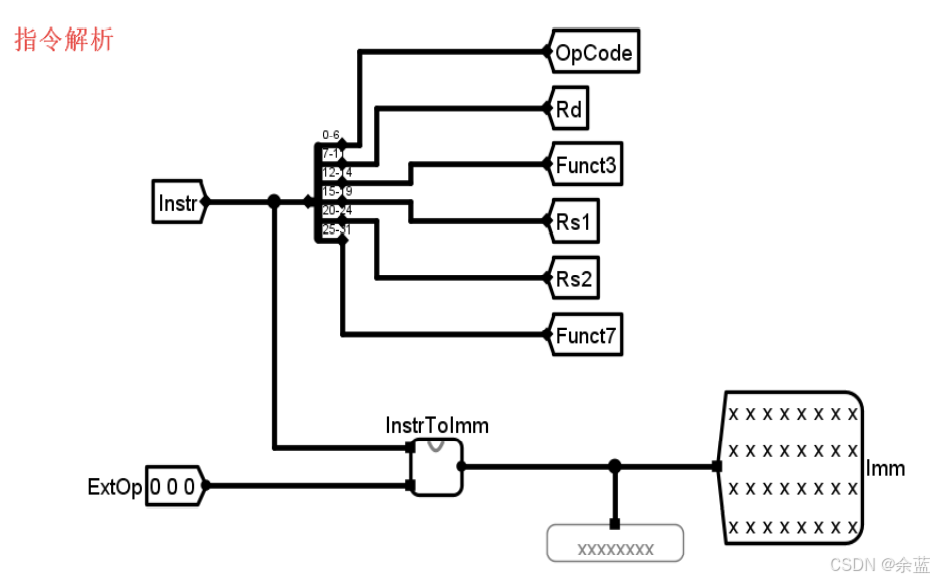

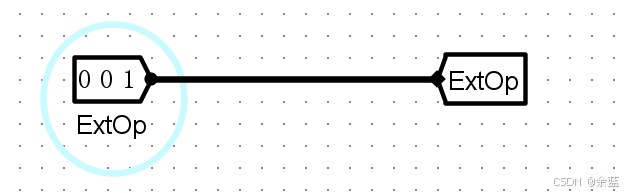

2、设计立即数扩展器,对指令中的立即数字段进行扩展生成32位立即数。参考电路如图所示:

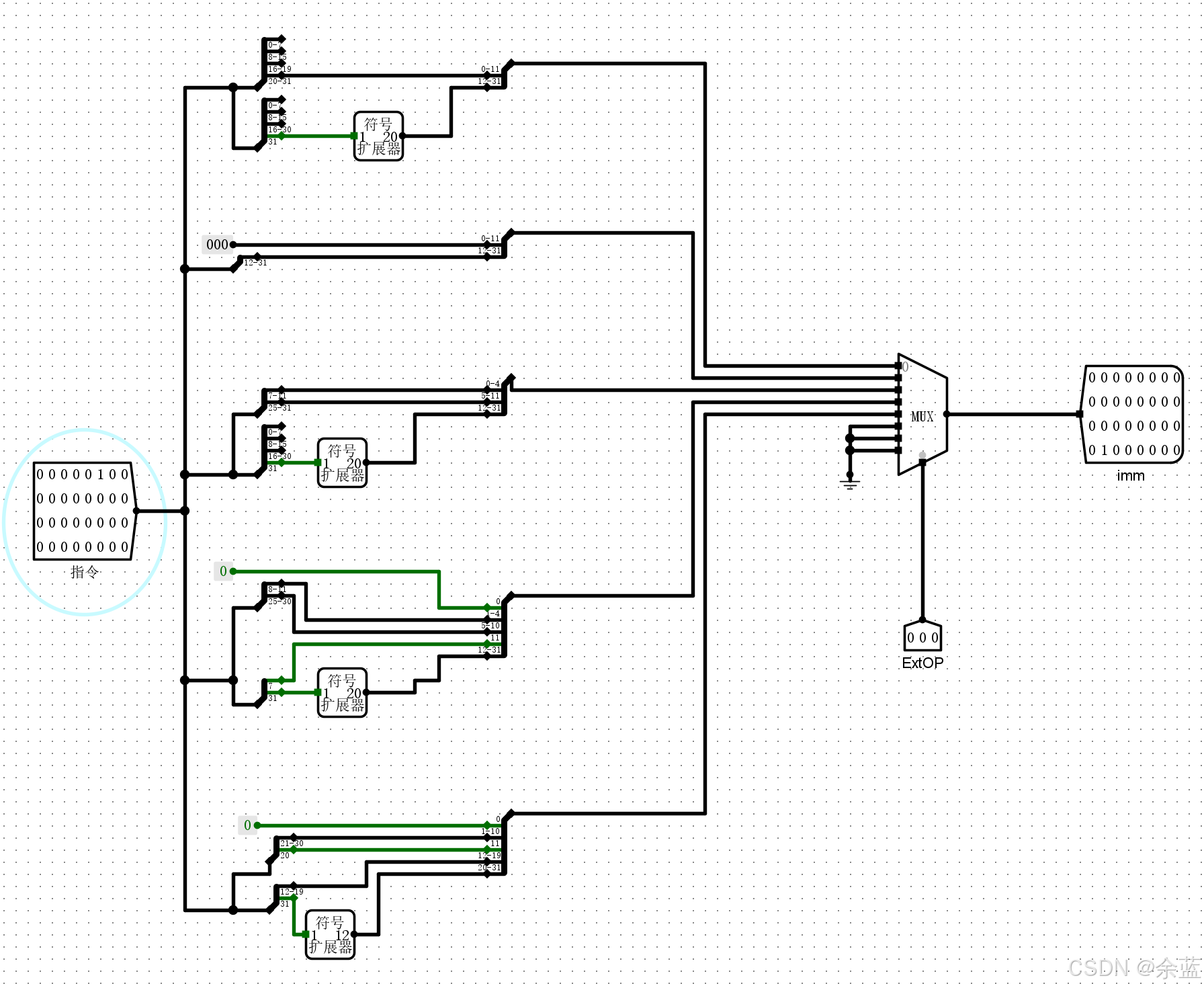

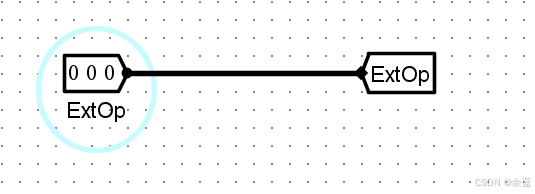

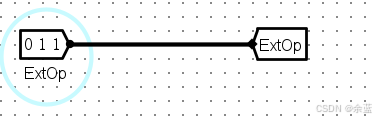

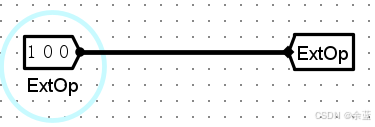

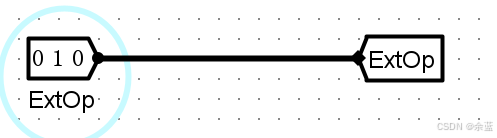

设计的电路如下图。利用分线器,实现将立即数字段扩展生成32位立即数imm输出。其中ExtOp选择哪种类型的立即数输出。

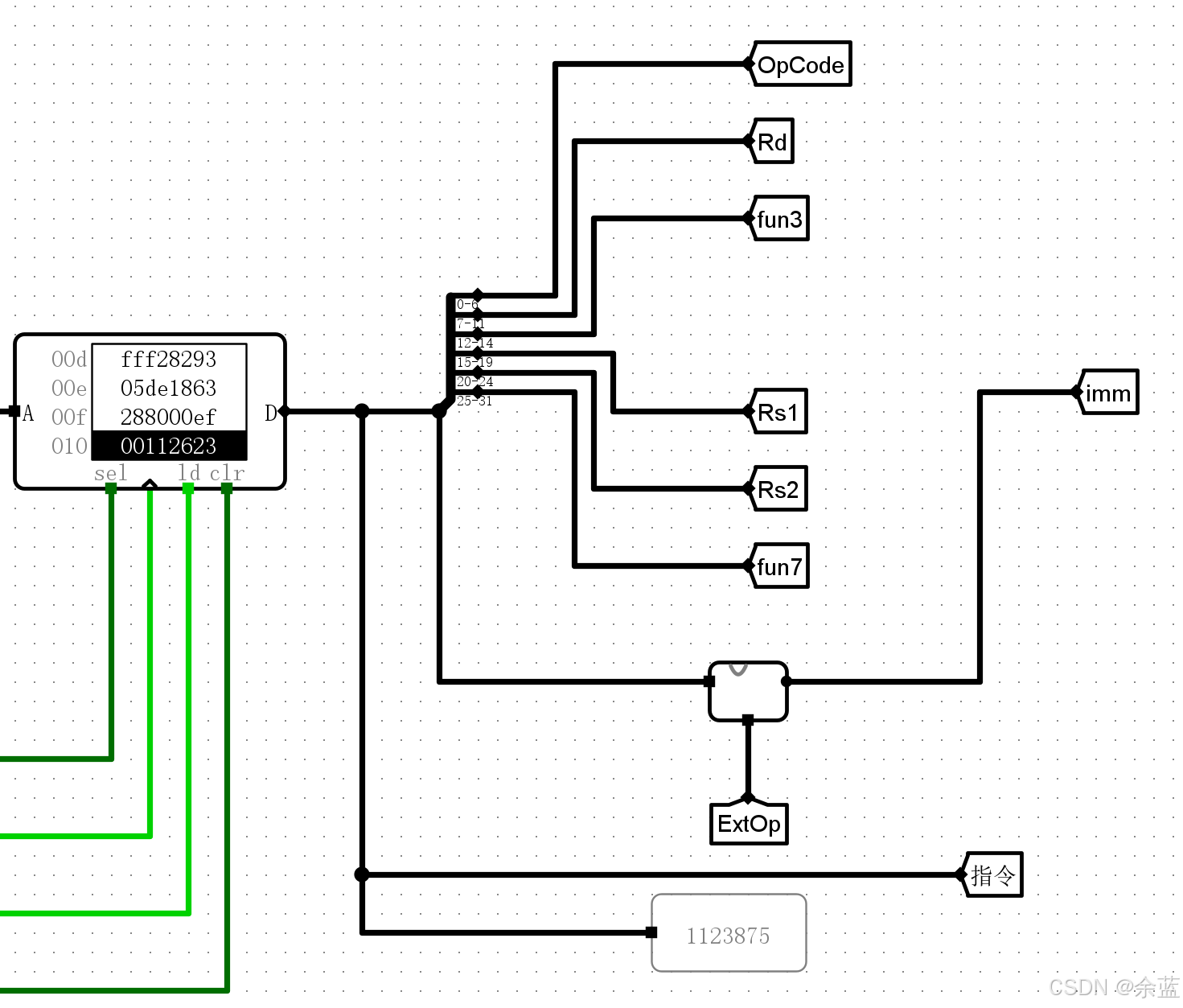

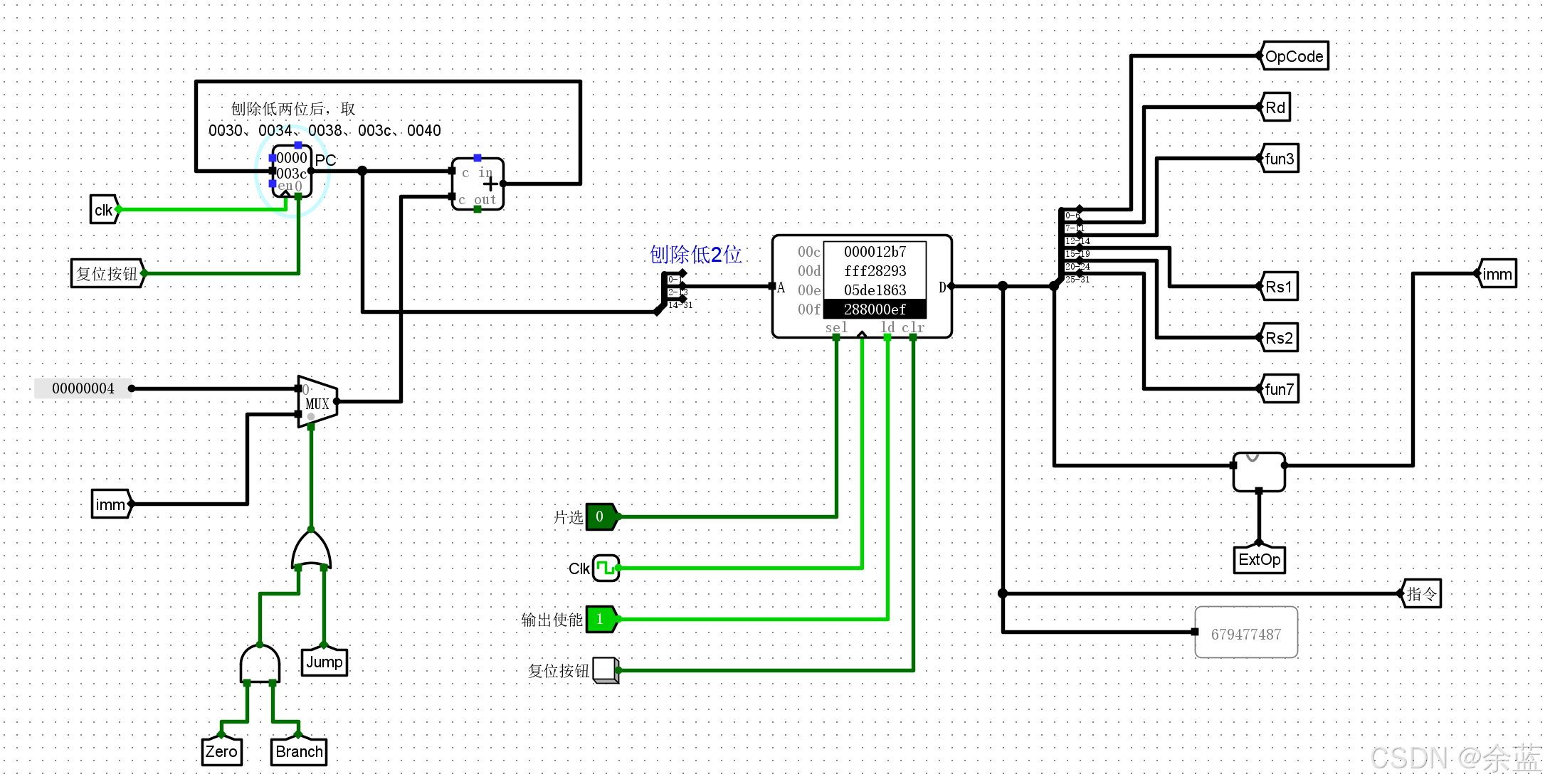

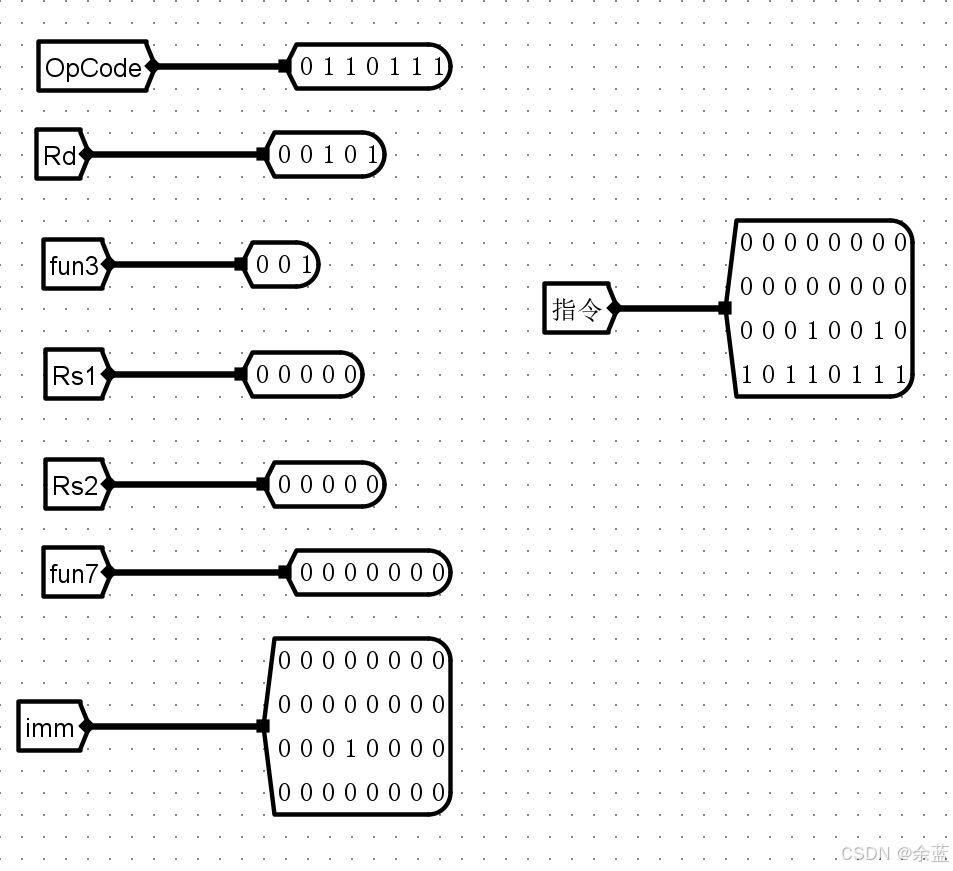

3、设计指令解析电路,将指令分解出opcode、rd、funct3、rs1、rs2和funct7 字段。参考电路如图所示:

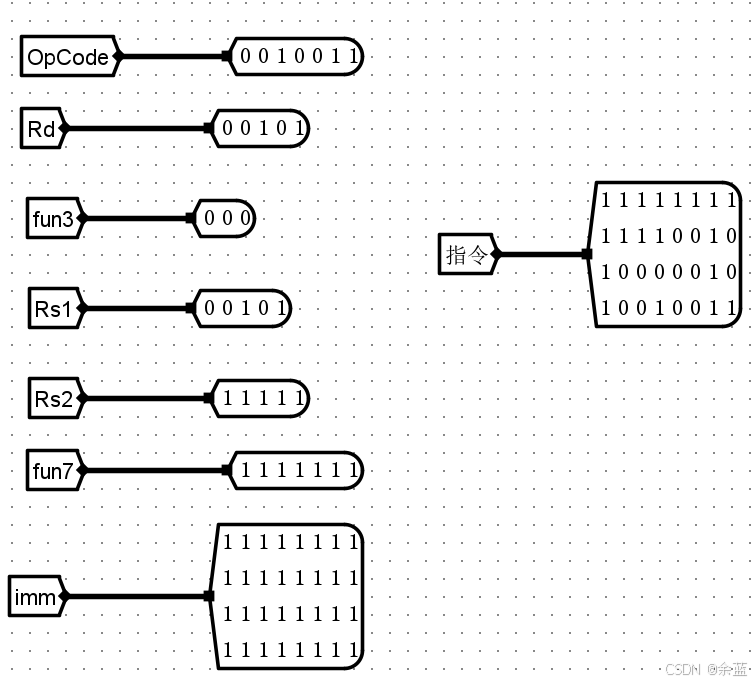

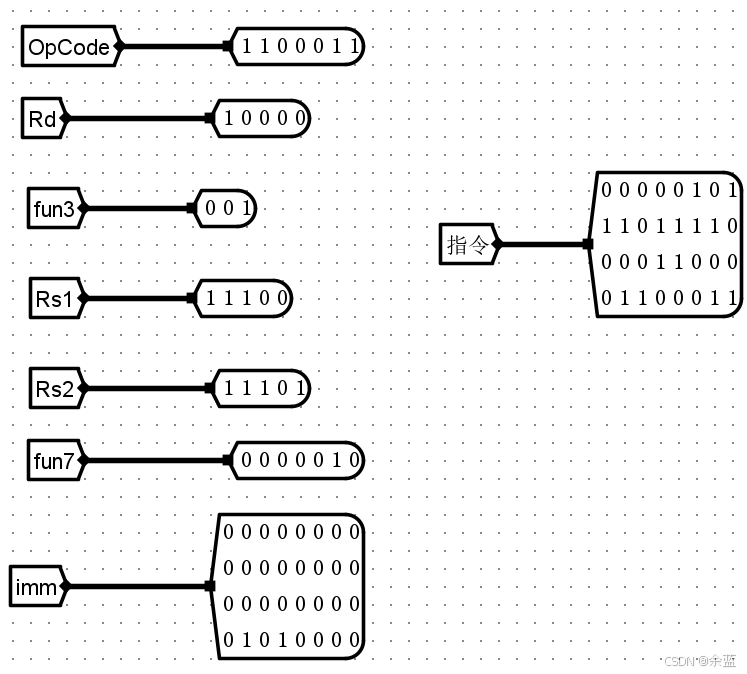

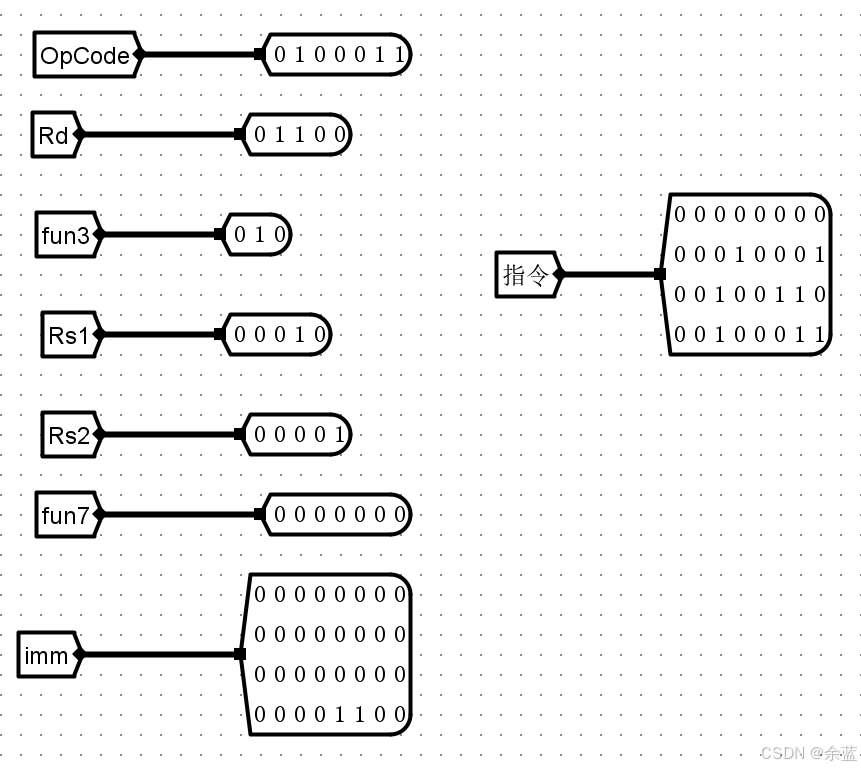

指令解析部分电路如下图,通过将存储器中第12单元开始的、刚才写入的指令输出到该部分电路中。然后通过分线器,将指令拆解,分为OpCode操作码、Rd等等。此外,还将封装的扩展器电路用于获取扩展后的立即数。

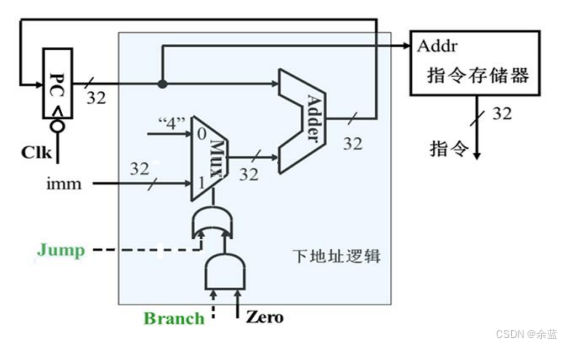

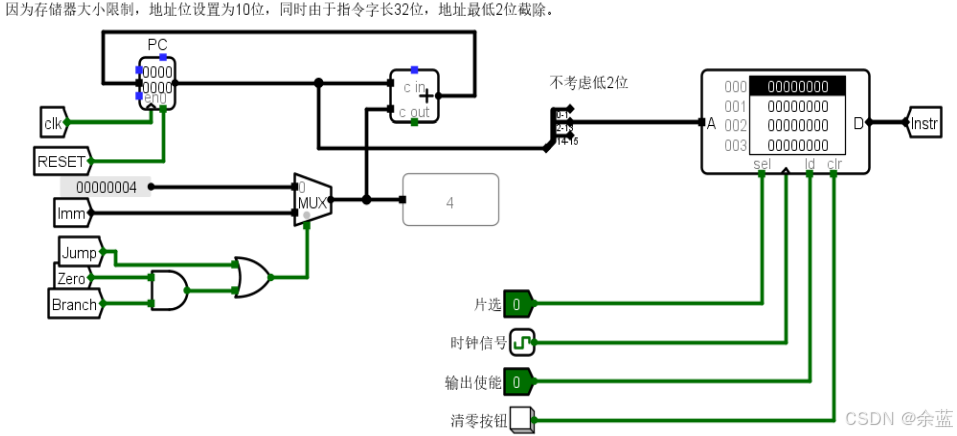

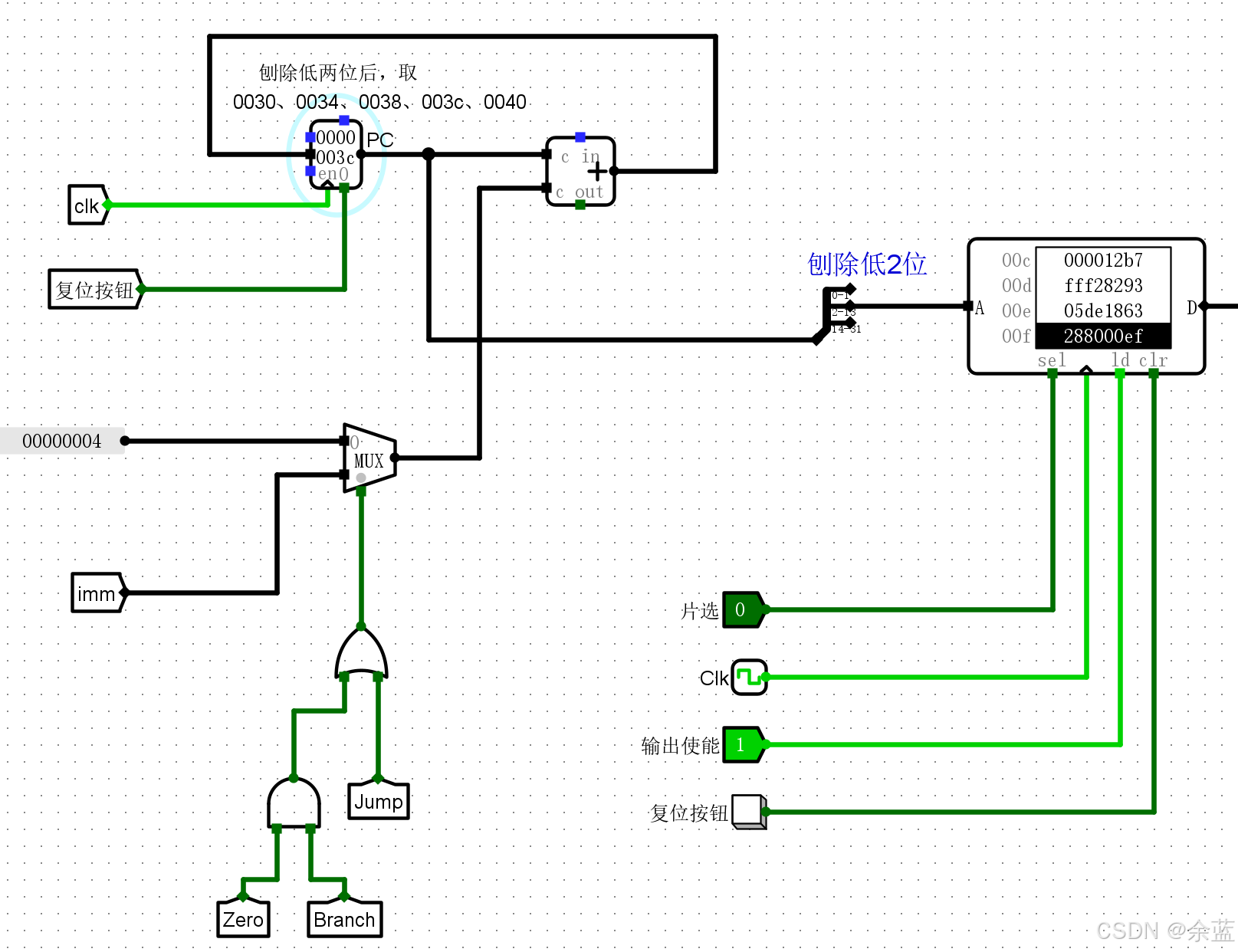

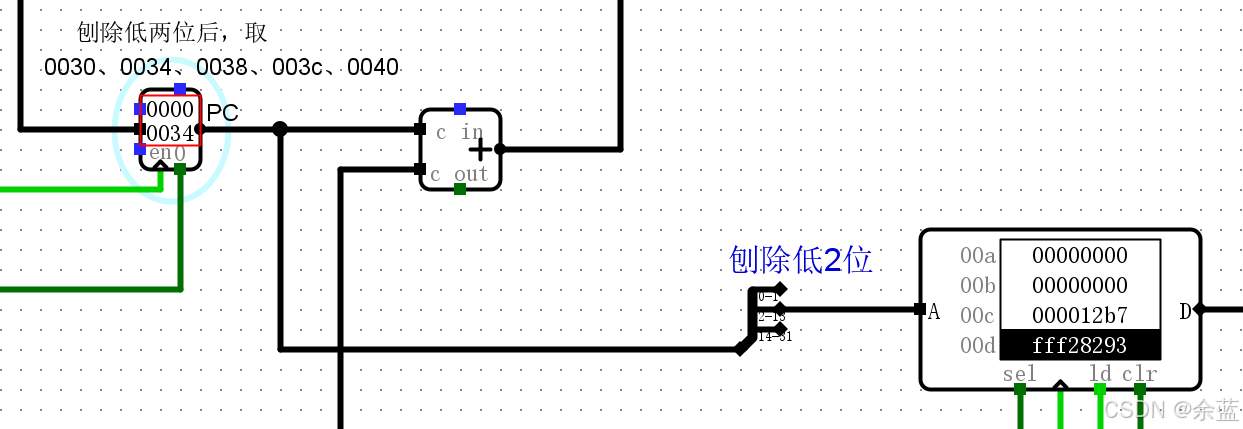

4、设计取指令部件,包括指令从存储器中的读取,PC的更新。其中,指令存储器可采用Logisim中的ROM组件实现,要求指令存储器容量为 16KB(地址位宽12位,即A[11:0],数据位宽32位,按字编址),指令字长为32位。

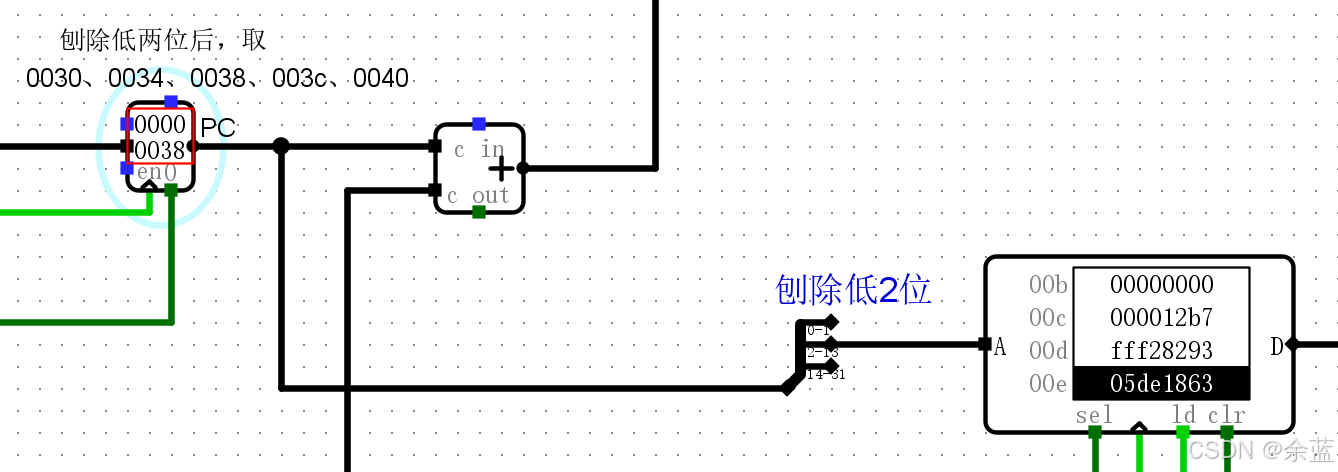

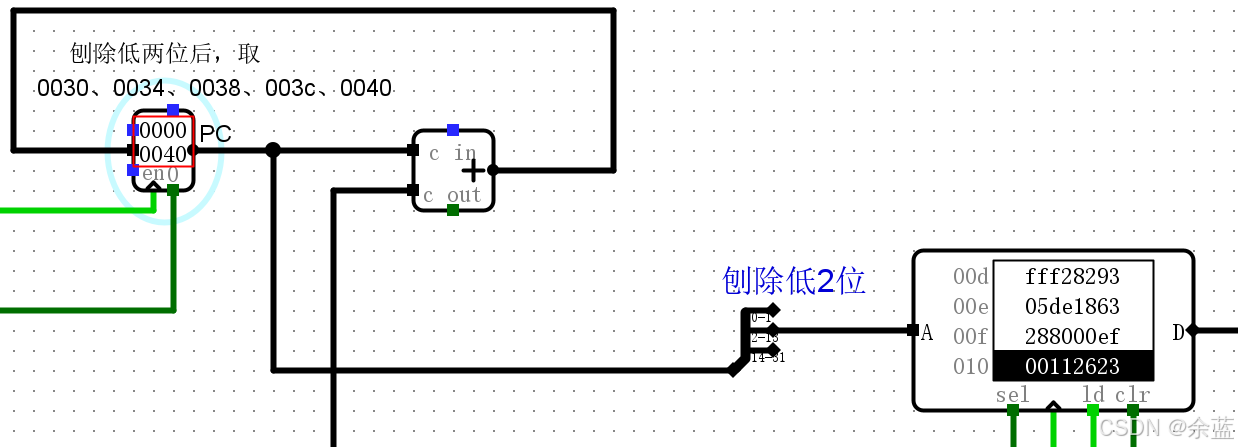

在程序设计中指令和数据寻址,都是以字节为单位,因而在Logisim中读取指令存储器时,最低2位地址舍弃;由于ROM地址编码定义为12位地址位宽,因而32位指令地址PC[31:0]中高18位地址也舍弃。只需把PC[13:2]赋值到A[11:0],其余的位皆无关。原理如图所示:

参考电路如图所示:

该部分电路如下图。

通过将寄存器中的PC连接到RAM存储器中,选择相应的地质单元,即可取出相应的指令了。

特别注意:由于低2位被刨除,所以,当要访问存储器中的第12号单元(即00c),则要重新考虑,当刨除第两位后,还要满足0000 0000 0000 1100,也就是把上面的式子左移两位,得0000 0000 0011 0000,所以第12位对应的PC为0030H,往后的地址也是这么推,分别是0034、0038、003c、0040

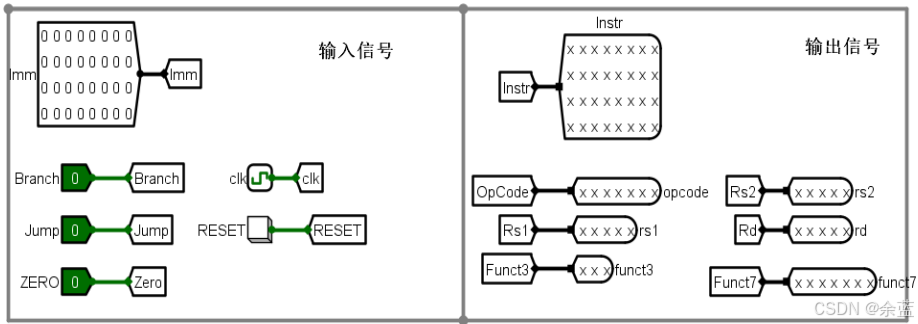

5、设计输入输出信号的观测窗口。为了便于检测输入输出数据是否正确,在主要电路图的上方设计观测窗口,采用隧道方式将信号引出,便于集中观察。参考电路如图所示:

电路图设计如下。

6、测试。在指令存储器上加载代码镜像文件,读取到指令存储器12处的指令时,观察输出结果,是否符合以下标准:

第1条 ExtOp设置为001:Opcode=0110111、rs2=00000、funct3=001、rd=00101、rs1=00000、 funct7=000000、Imm=0x00001000。

第2条 ExtOp设置为000: Opcode=0010011、rs2=11111、funct3=000、rd=00101、rs1=00101、funct7=1111111、Imm=0xffffffff。

第3条 ExtOp设置为011: Opcode=1100011、rs2=11101、funct3=001、rd=10000、rs1=11100、funct7=000010、Imm=0x00000050。

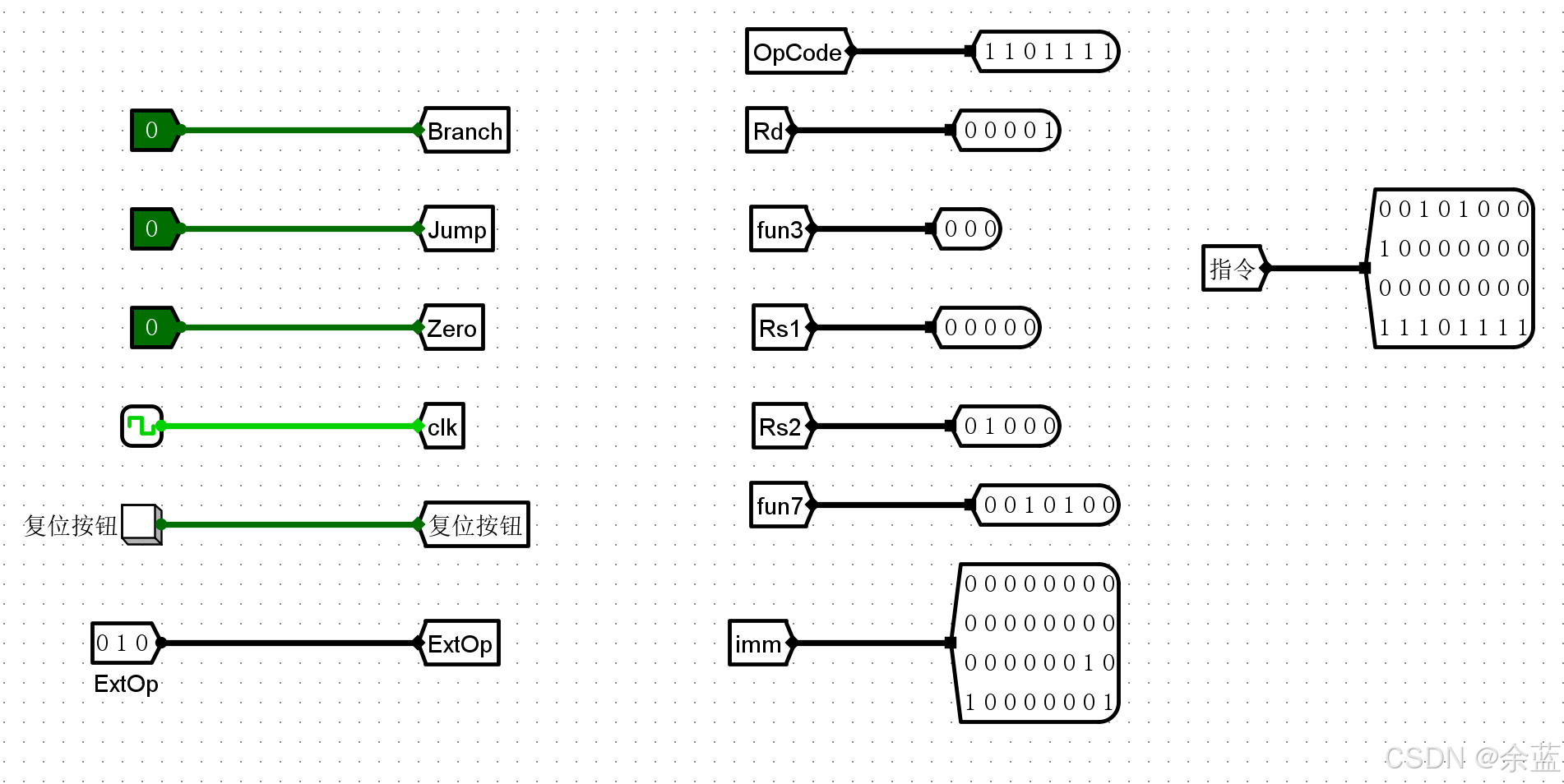

第4条 ExtOp设置为100:Opcode=110111、rs2=01000、funct3=000、rd=00001、rs1=00000、funct7=0010100、Imm=0x00000288。

第5条 ExtOp设置为010: Opcode=0100011、rs2=00001、funct3=010、rd=01100、rs1=00010、funct7=0000000、Imm=0x0000000c。

1选择第一条指令输出,并且将ExtOp设置为001,具体的输出如下图所示。

2选择第二条指令输出,并且将ExtOp设置为000,具体的输出如下图所示。

3选择第三条指令输出,并且将ExtOp设置为011,具体的输出如下图所示。

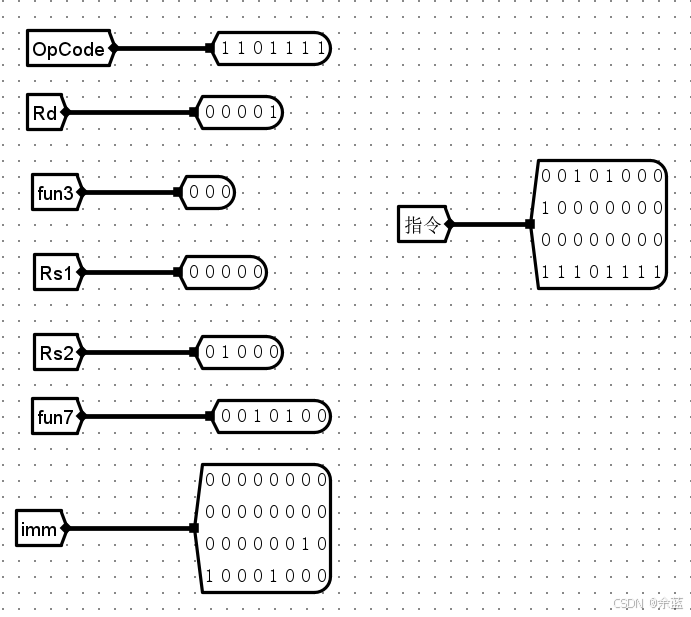

4选择第四条指令输出,并且将ExtOp设置为100,具体的输出如下图所示。

5选择第五条指令输出,并且将ExtOp设置为010,具体的输出如下图所示。

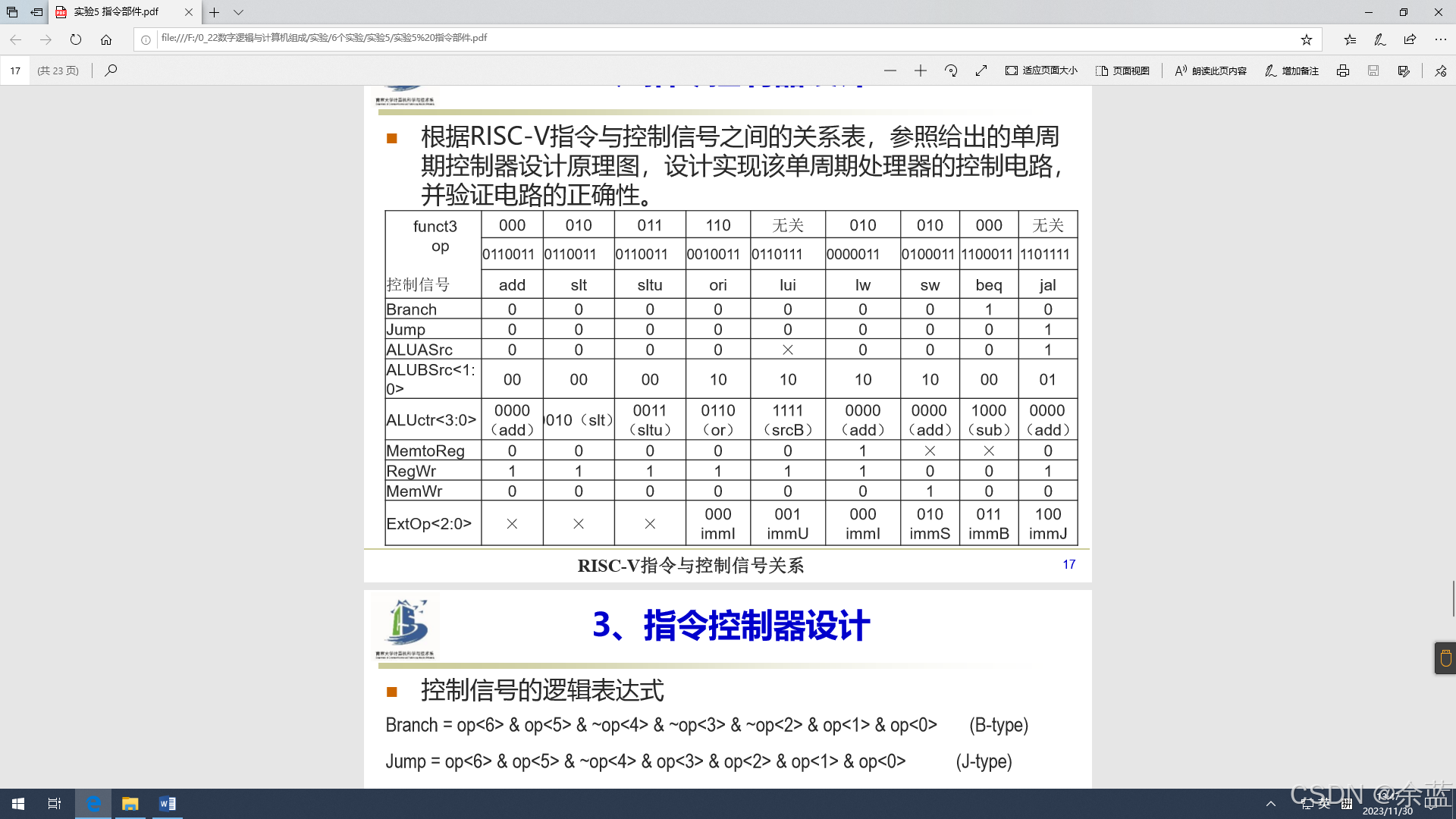

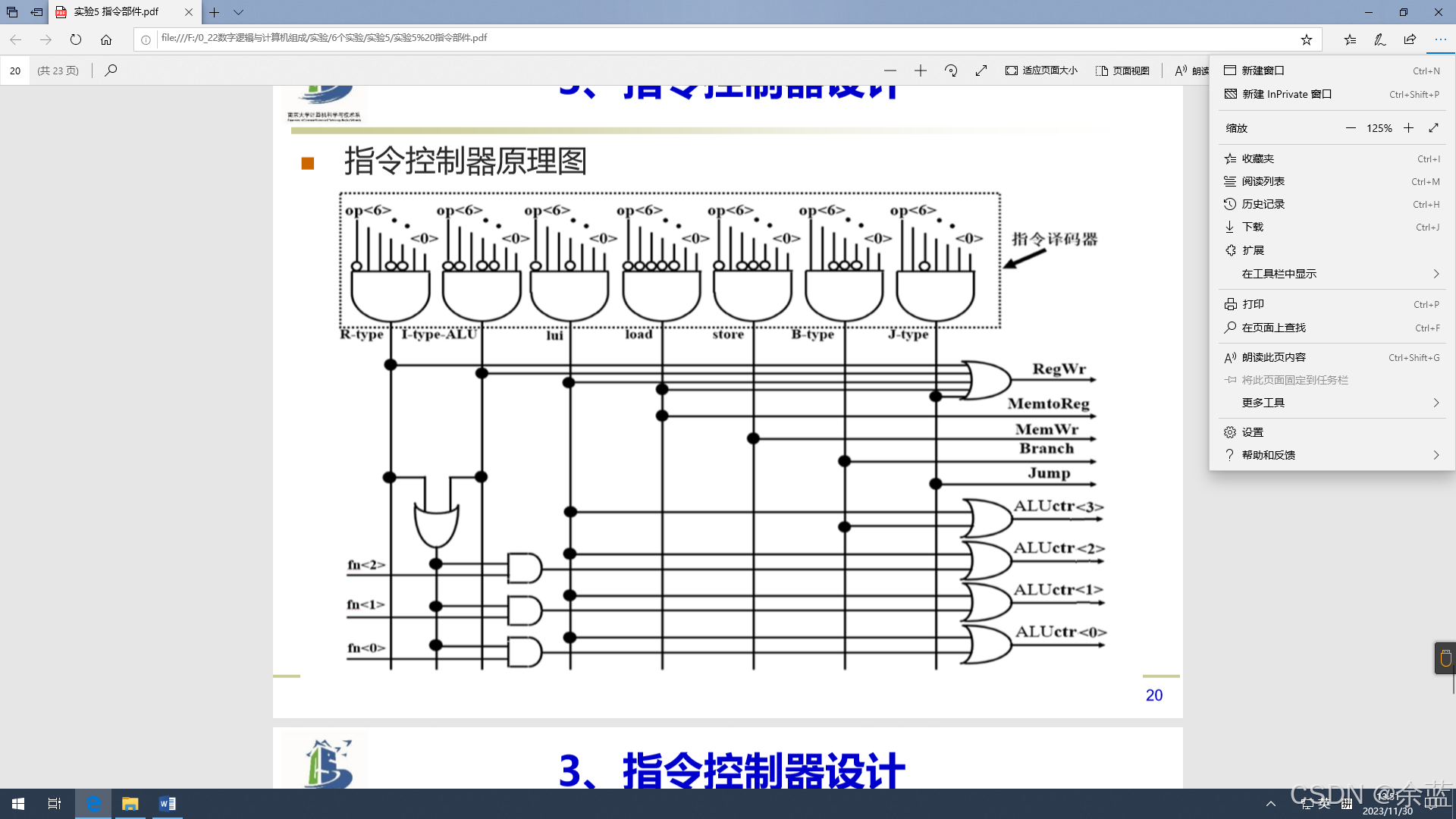

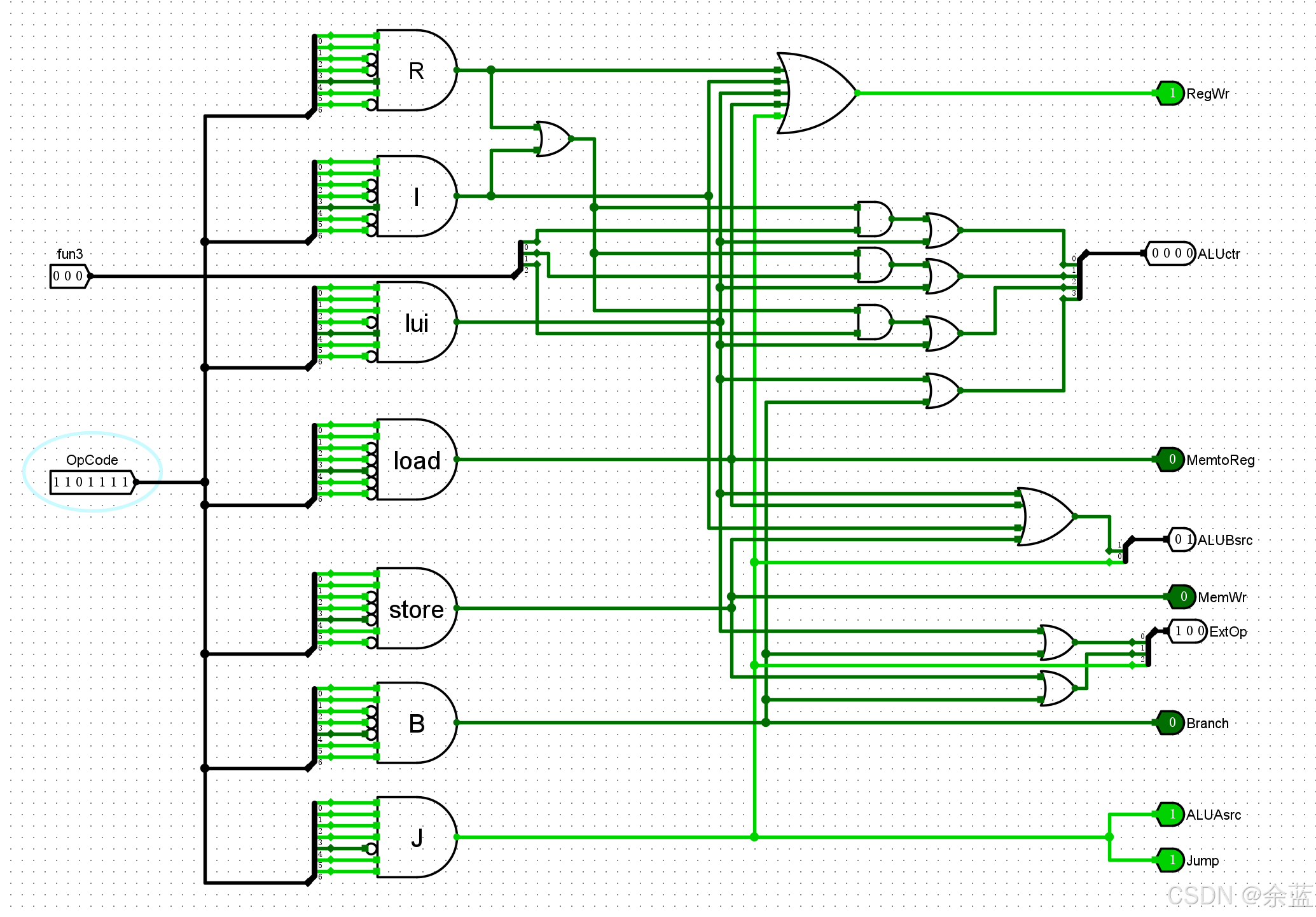

7、设计指令控制器。根据RISC-V指令与控制信号之间的关系表,参照给出的单周期控制器设计原理图,设计实现该单周期处理器的控制电路, 并验证电路的正确性。

指令控制器原理图

(注:此图中缺ALUASrc、ALUBSrc、ExtOp三个控制信号的生成电路,需补上)

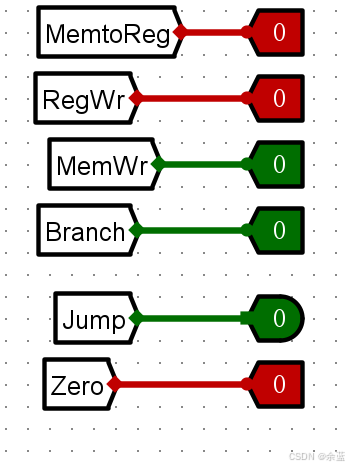

根据课本P236,表8.5中9条指令的控制信号取值的表,逻辑非常简单,效果如下图。

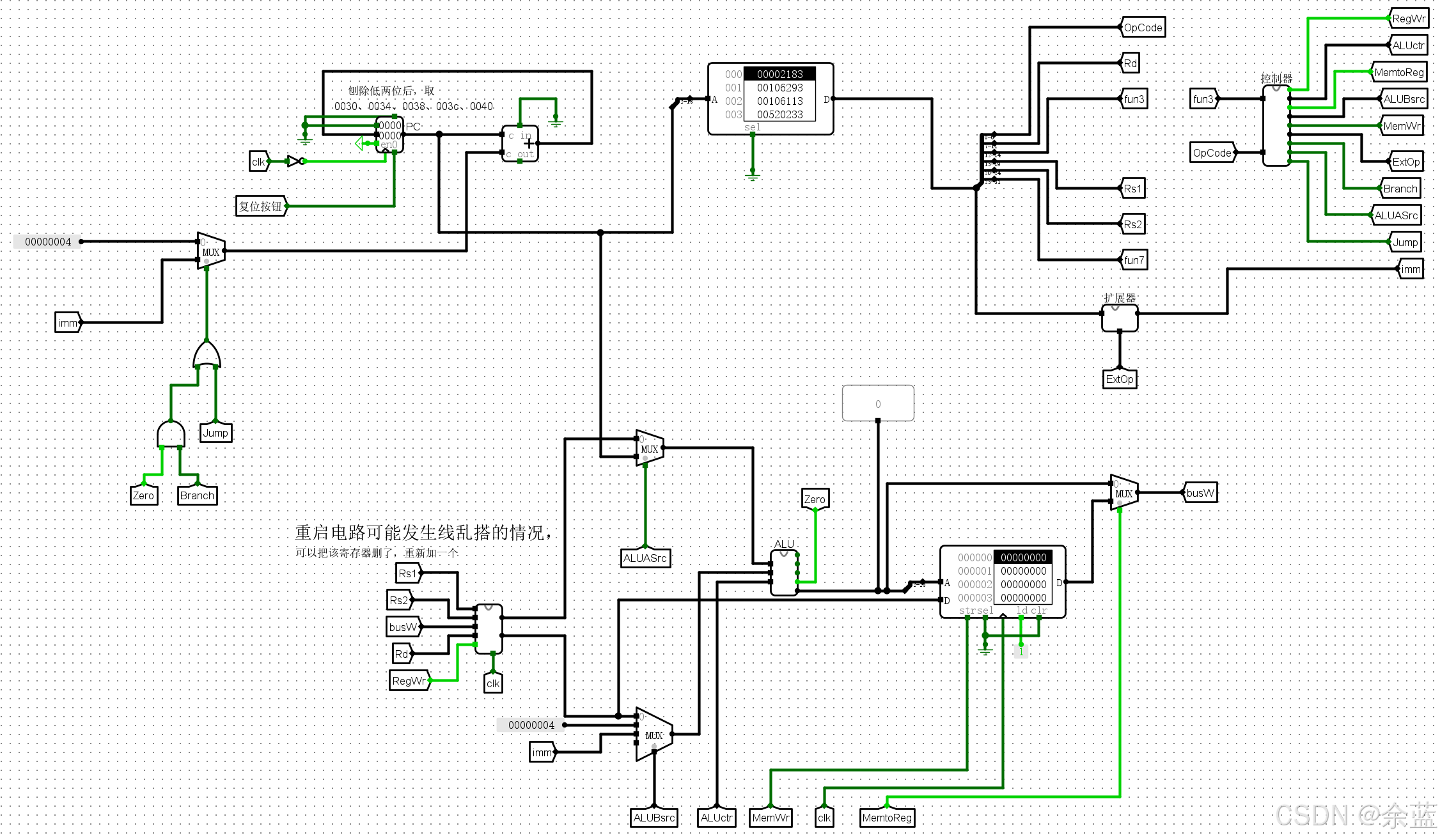

8、单周期CPU完整设计

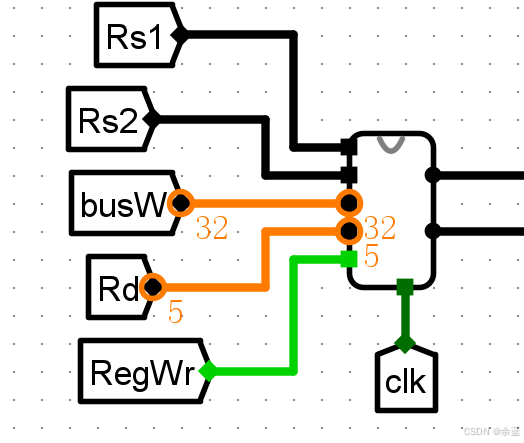

利用前面实验已经完成的取指令部件、寄存器堆部件、指令译码部件、立即数扩展部件、指令控制部件,连接数据通路,实现单周期CPU的电路图。

实验电路图如下。

包括PC(寄存器)、指令存储器(ROM)、扩展器、数据存储器(RAM),以及之前实验中完成的ALU和寄存器堆。

左上角为PC,它是一个寄存器,存储当前的PC值,输出端连接一个加法器,为了使PC+4抑或是PC+imm。当然,+4还是+imm是由PC 下方的多路选择器控制,当jump为0,则PC正常地一条一条指令执行,即PC+4.当jump=1,则PC+imm,无条件跳转。

中上方为指令存储器,将来会在RISC—V中编写好程序然后转换为 二进制指令,存入。它的输出端连接一个分线器,这是指令解析器,其设计参考了课本P199中的表,RISC-V指令格式。

利用解析出来的值,输入控制器中。

最后,控制器输出端口的各种值 如MEmWr、ALUCtr等,控制了访问主存、访问寄存器、生成跳转指令等功能。

各隧道如下。

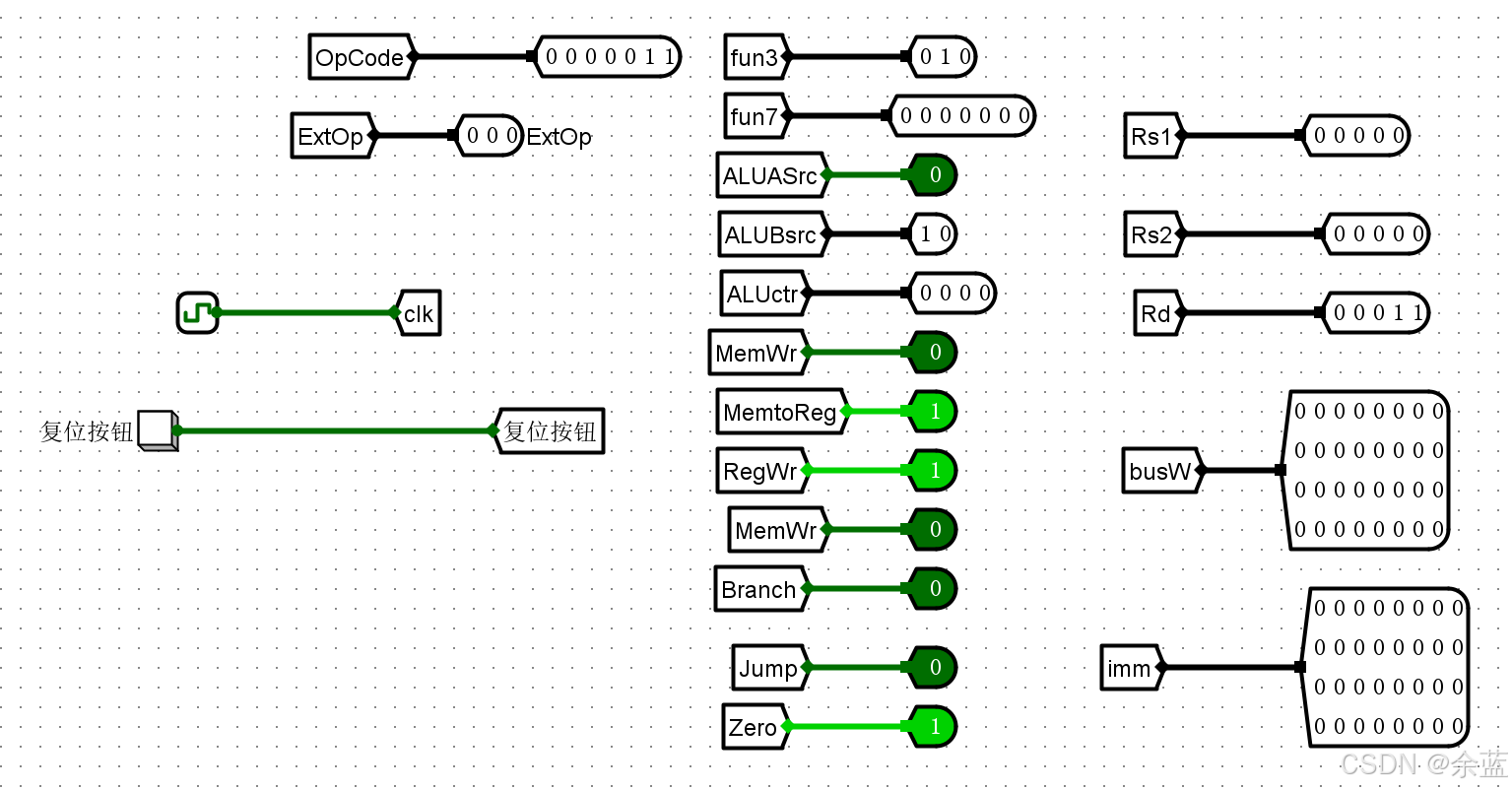

9、运行测试程序来验证处理器设计的正确性

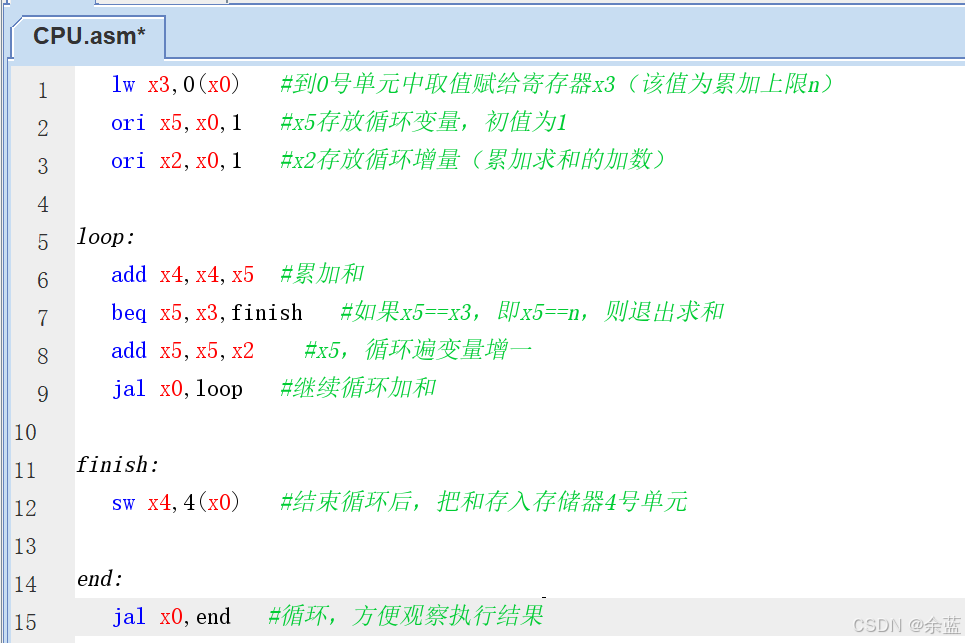

利用9条指令编写一个汇编源程序(如累加求和、排序等),在RARS模拟器中编译调试正确后转换为机器代码,写入指令存储器,启动程序执行,观察运行结果是否正确。

在RARS中编写累加求和的程序。

至于为什么要把累加和存放到主存第四单元,原因是指令中的主存地址被剔除了低两位,所以当指令要访问主存的1号单元,实际上是访问4号单元。

详细说就是,指令被刨除后,值仍为1,即0001,那么刨除之前一定是0001xx,这个1就是4了。

接着,把该程序转为机器代码。

编入程序存储器(ROM)中

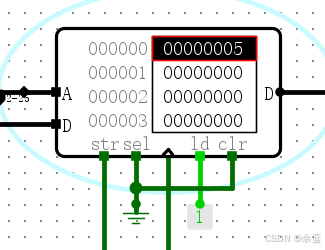

在主存0号单元写入累加上限n=5.运行(预期结果为15)。

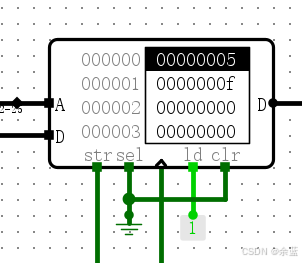

运行结束,一号单元为0000000f即15,正确。

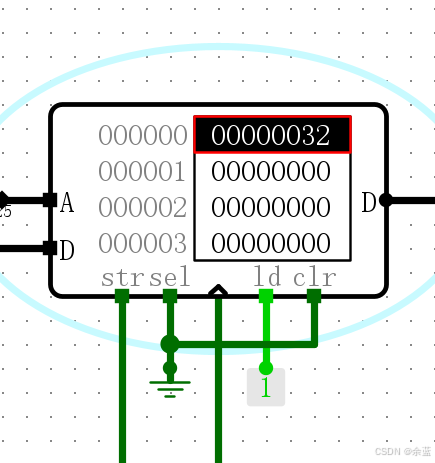

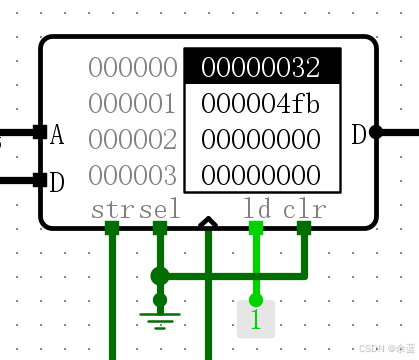

测试累加到50(0x00000032)。预期结果为1275(4fb)

结果为

四、实验步骤及结果

已放入每道题后面

五、分析与思考

1本实验是一个综合性强的实验,首先要求对前面的ALU运算功能熟悉,且要对寄存器堆的工作原理了解,而且还要先在实验三中的汇编语言编写中打下基础。

2实验中要 注意,连接 隧道时,要分清是输入还是输出,如果输入输出乱用,会发生数据冲突,即出现标红的线。

3 数据通路中寄存器、ALU或者其他功能单元的连接可能存在问题,导致数据传输或运算错误。总而言之,如果其中一个部件出现小问题,都有可能导致整个线路信号出现错误。所以,前期的连线应该逐步测试。

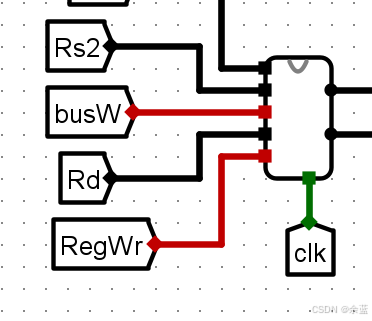

4由于电路比较复杂,所以很可能一不小心把两个端口连到了一块,从而导致错误。即因为在电路中创建了短路,即两个信号线被直接连接在一起。这可能导致电路异常行为,因为信号可能被直接短路到地或电源。比如下图的寄存器。

发生端口不匹配的原因不是别的,而是因为第三和第四个端口连接到了一块。

这种错误不易察觉,所以当出现了端口不匹配的时候,可以往这方面考虑一下。

5接着还有一个问题,就是寄存器的值是会累加的,所以在测试累加和实验时,在测试完一个后,应该重启logism。避免值的累加,导致结果错误。

1401

1401

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?