After completing this section, you should be able to

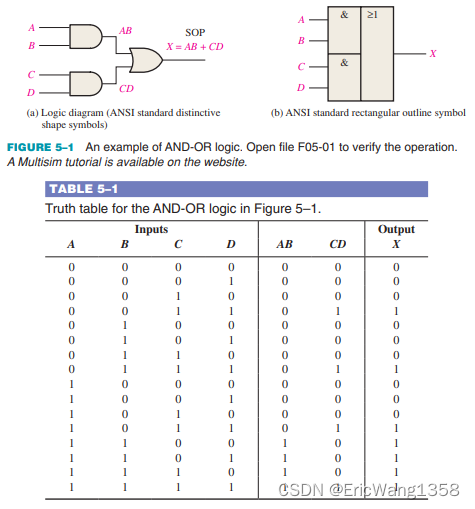

u Analyze and apply AND-OR circuits

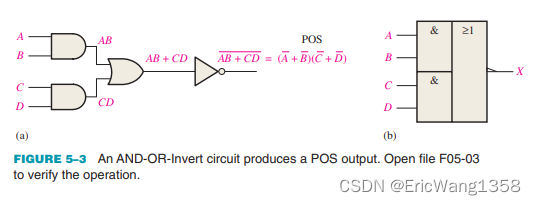

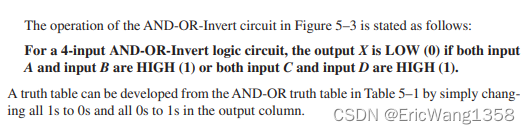

u Analyze and apply AND-OR-Invert circuits

u Analyze and apply exclusive-OR gates

u Analyze and apply exclusive-NOR gates

AND-OR Logic

AND-OR-Invert Logic

Exclusive-OR Logic

Exclusive-NOR Logic

[ECE] Number Systems, Operations, and Codes_Makeup-CSDN博客

这是一个电路图,展示了如何使用异或门(XOR gate)来实现一个4位原始二进制代码的偶校验位生成器。

在这个电路中,每个数据位(A0, A1, A2, A3)分别通过一系列的异或门连接。异或门的逻辑是这样的:如果两个输入不同,则输出1;如果两个输入相同,则输出0。对于偶校验位,我们希望在数据位的总数中有偶数个1,这样如果在任何数据传输中有一个位被错误地改变了,接收方可以通过校验位检测到错误。

电路的工作原理是:

- 首先,A0和A1通过一个异或门,产生一个中间结果。

- 这个中间结果再与A2通过另一个异或门,生成第二个中间结果。

- 最终,这个第二个中间结果与A3通过第三个异或门,输出最终的偶校验位。

如果输入数据位中有奇数个1,经过这些异或门的操作,最终的输出将会是1,使得包括校验位在内的总数变成偶数个1。如果输入数据位中有偶数个1,最终的输出将会是0。

例如:

- 如果输入是

1101(奇数个1),最终的偶校验位将会是1。 - 如果输入是

1010(偶数个1),最终的偶校验位将会是0。

这样,无论数据位的组合如何,最终的输出(包含数据位和偶校验位)总会有偶数个1,这就是所谓的偶校验。通过这种方式,我们可以在数据传输中加入一个简单的错误检测机制。如果在传输过程中由于某种原因(比如电磁干扰)造成一个位发生了变化,接收方可以通过检查所有位(包括校验位)的总和是否为偶数来判断数据是否有误

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?