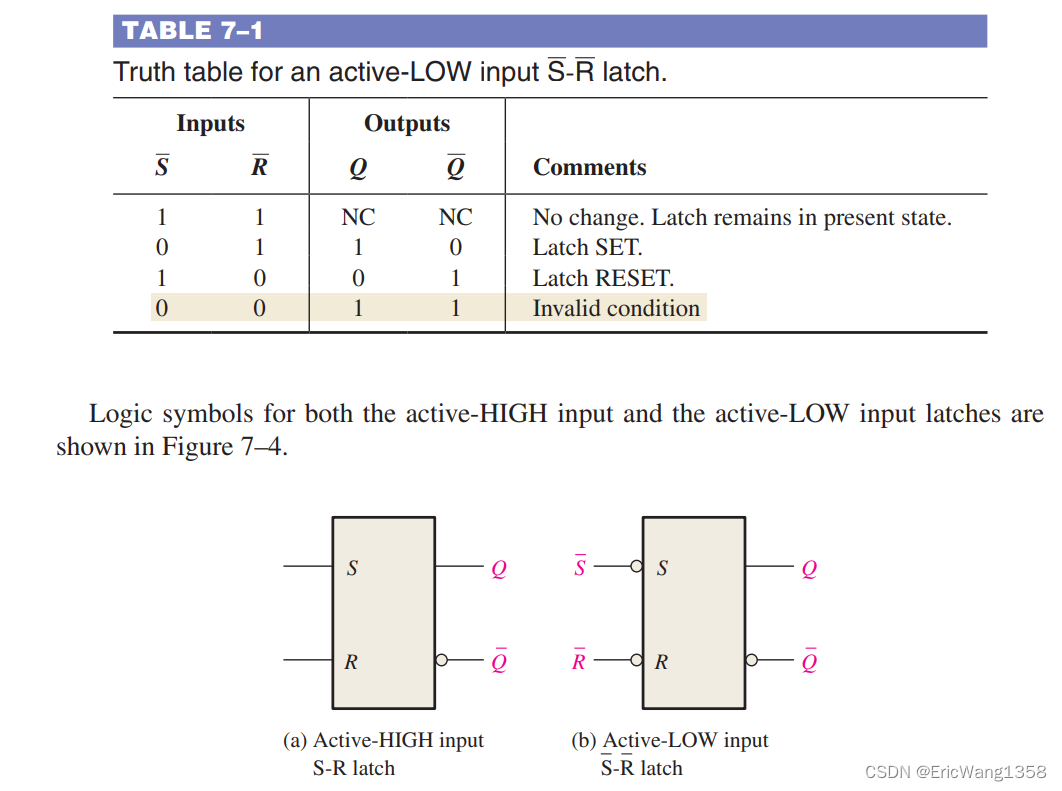

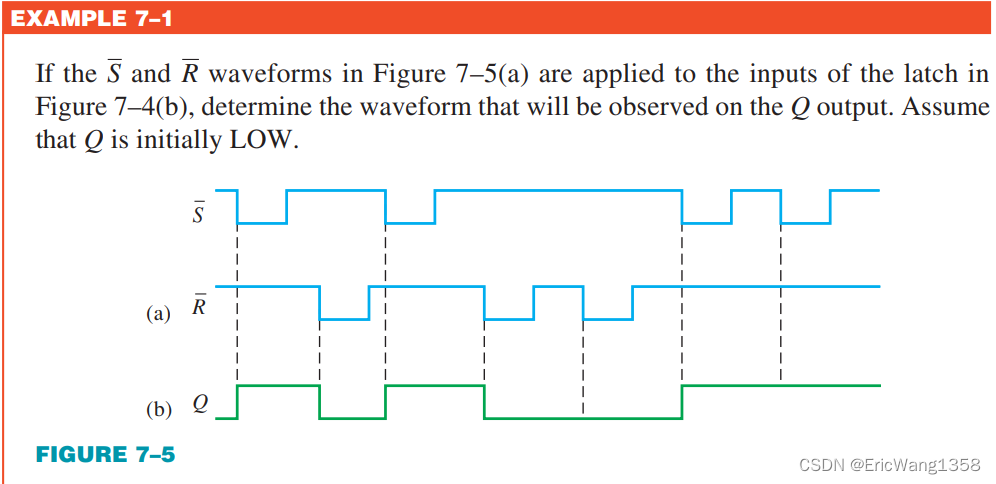

1.S and R

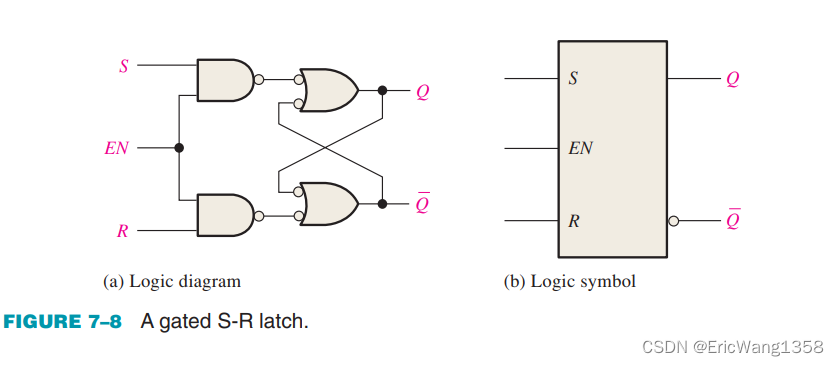

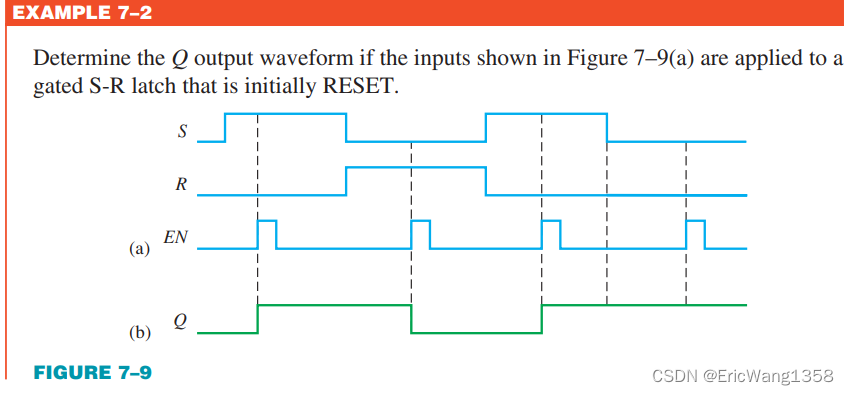

2. Gated S-R

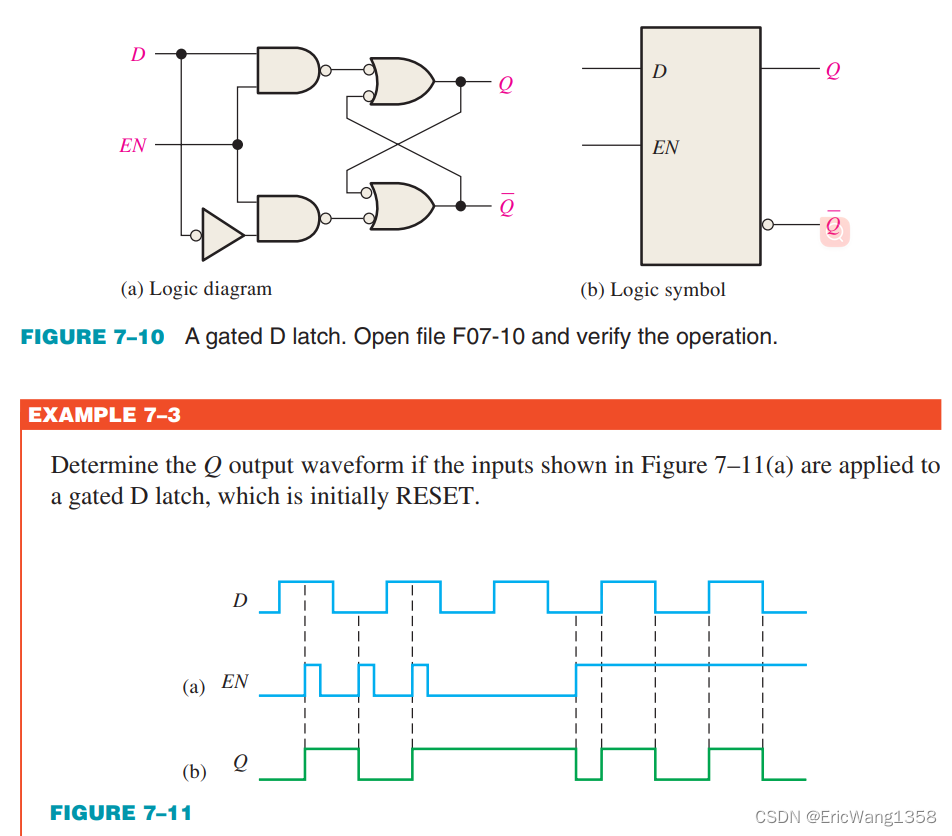

3. Gated D Latch

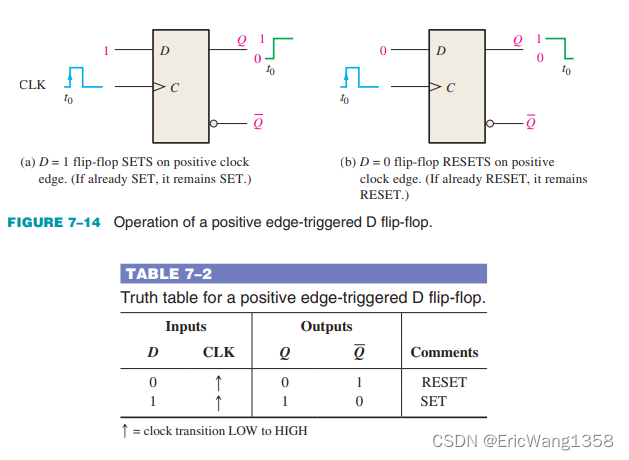

4. The D Flip-Flop

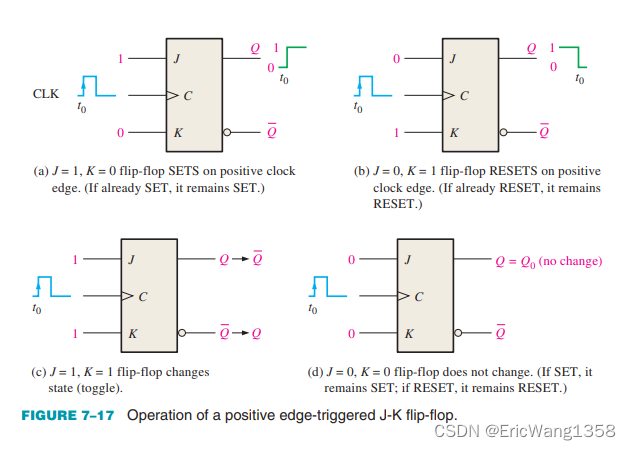

5.The J-K Flip-Flop

5.The J-K Flip-Flop

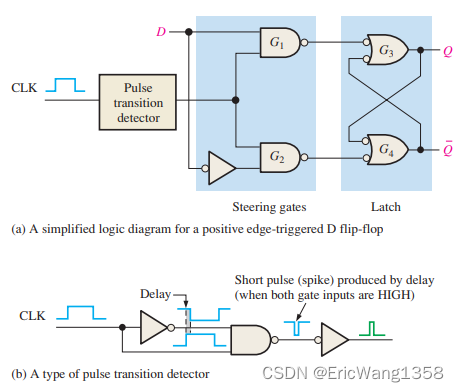

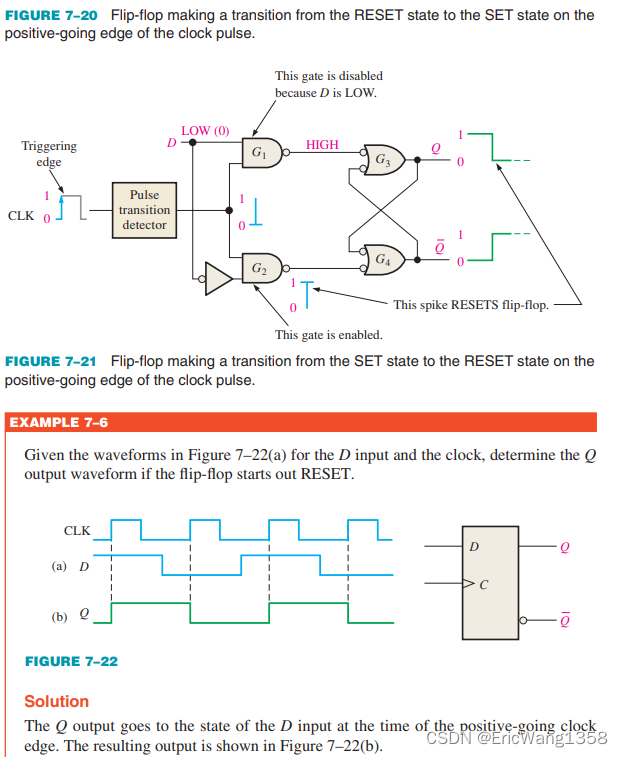

6. D Flip-Flop Edge triggering.

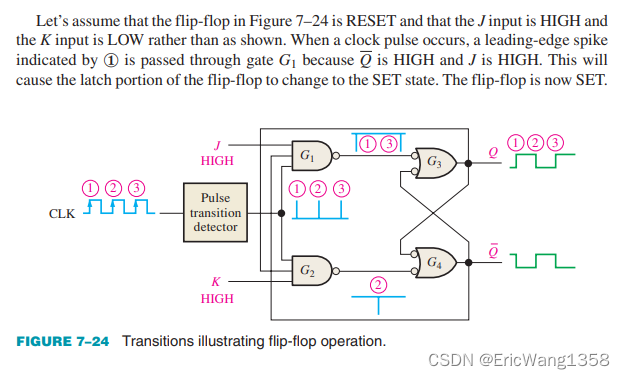

7.J-K Flip-Flop Edge triggering.

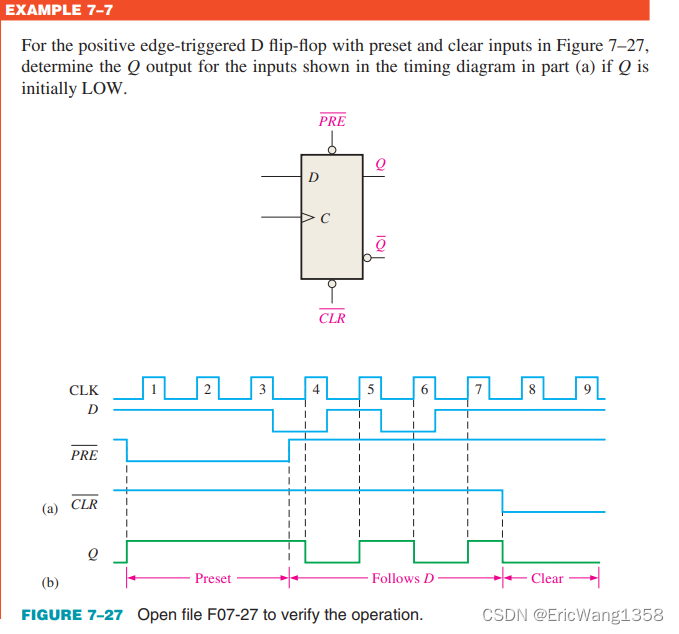

8. Asynchronous Preset and Clear Inputs

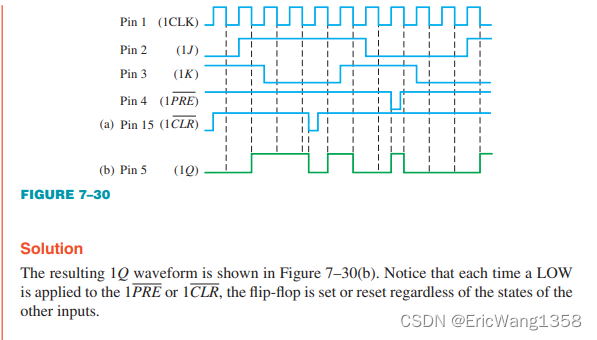

9. Implementation: J-K Flip-Flop

7–3 Flip-Flop Operating Characteristics

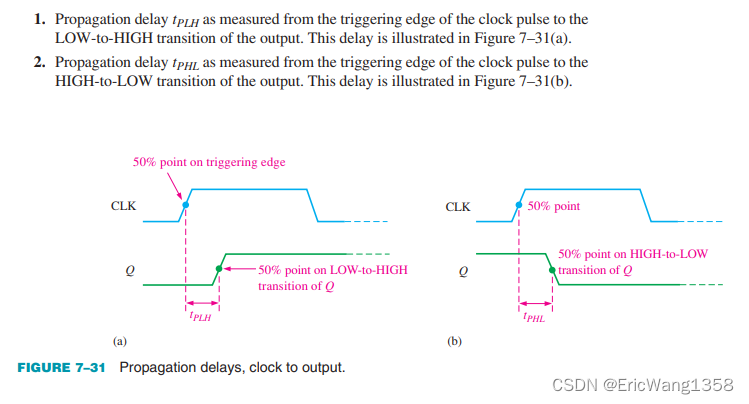

1.Propagation Delay Times

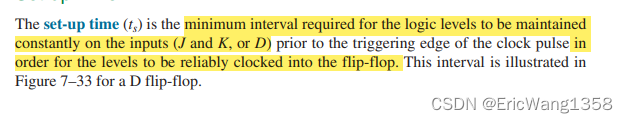

2.Set-up Time

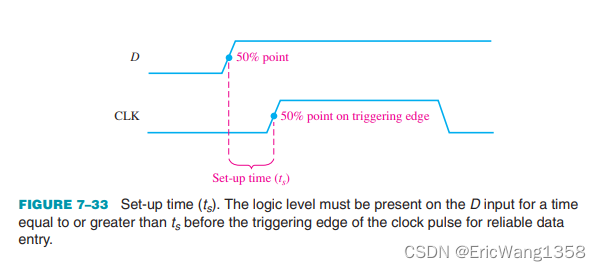

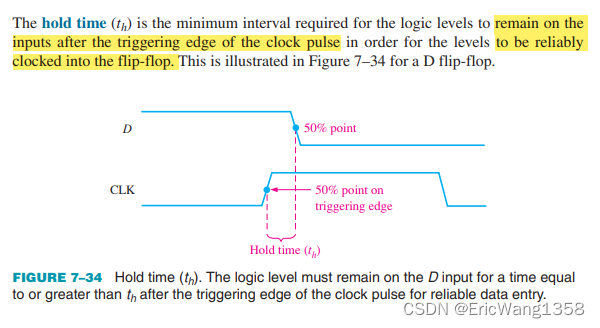

3.Hold Time

4.Maximum Clock Frequency

The maximum clock frequency (fmax) is the highest rate at which a flip-flop can be reliably triggered. At clock frequencies above the maximum, the flip-flop would be unable to respond quickly enough, and its operation would be impaired.

5.Pulse Widths

Minimum pulse widths (tW) for reliable operation are usually specified by the manufacturer for the clock, preset, and clear inputs. Typically, the clock is specified by its minimum HIGH time and its minimum LOW time

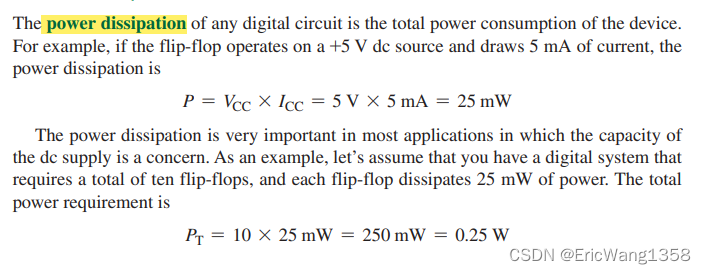

6.Power Dissipation

7–4 Flip-Flop Applications

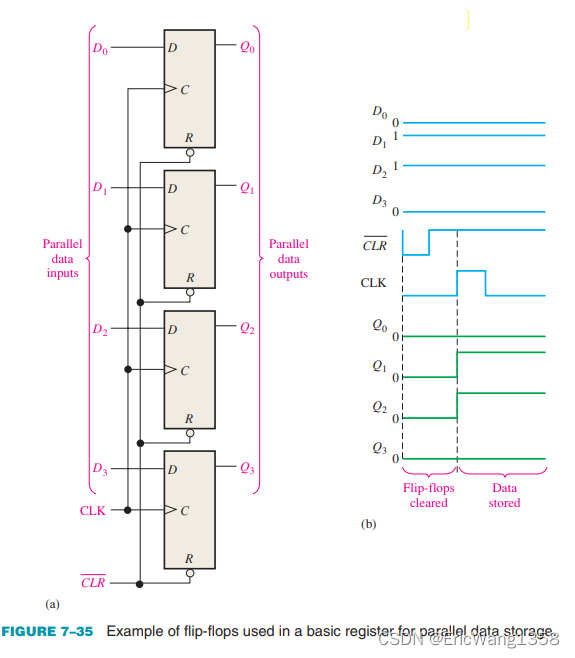

1.Parallel Data Storage

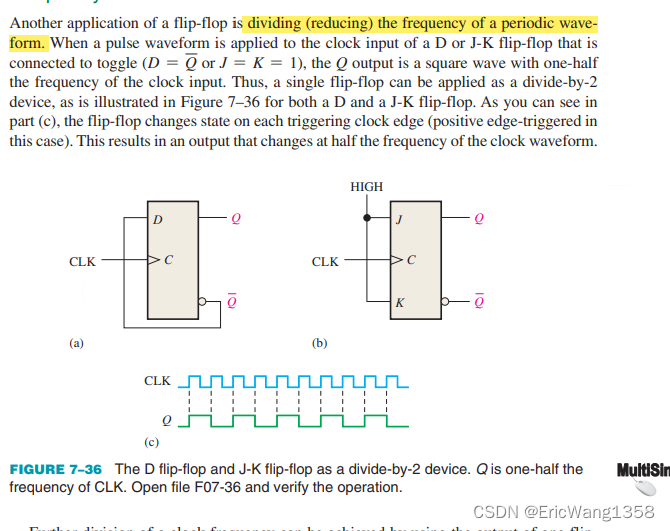

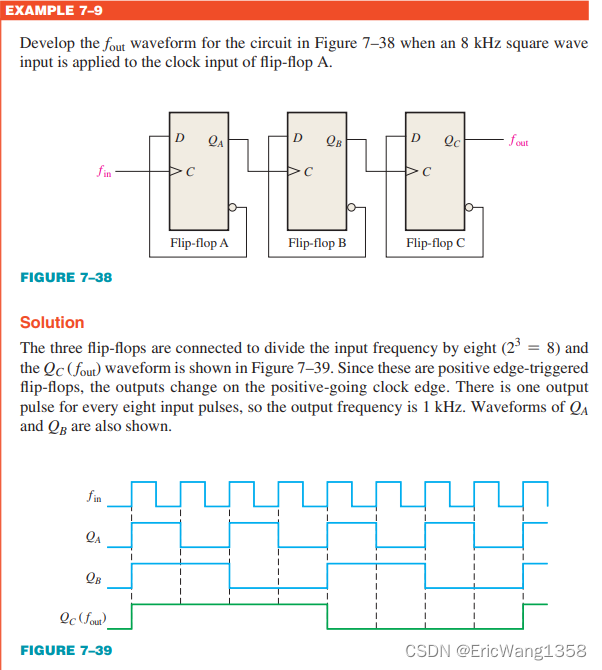

2.Frequency Division

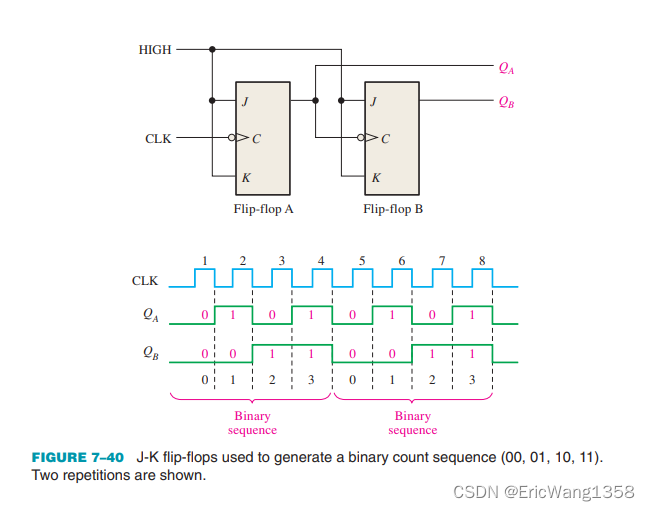

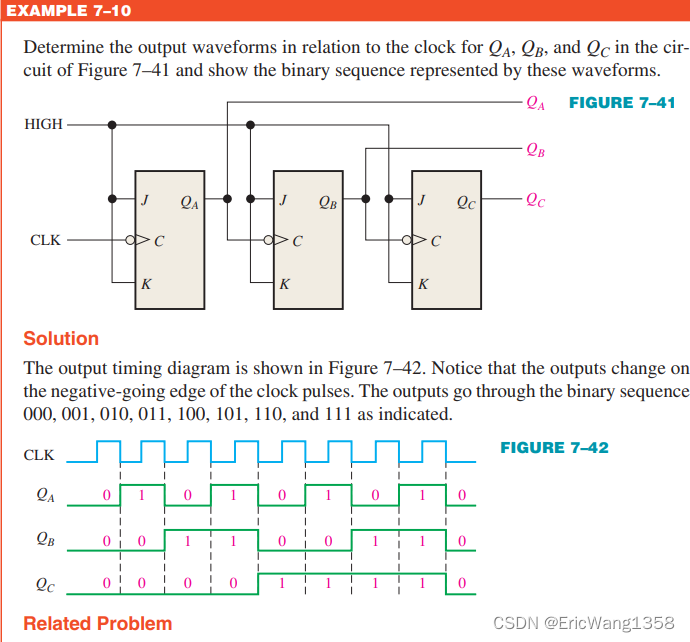

3.Counting

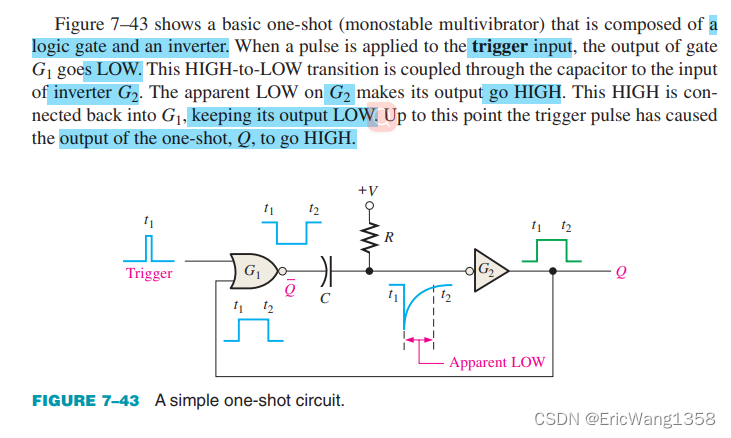

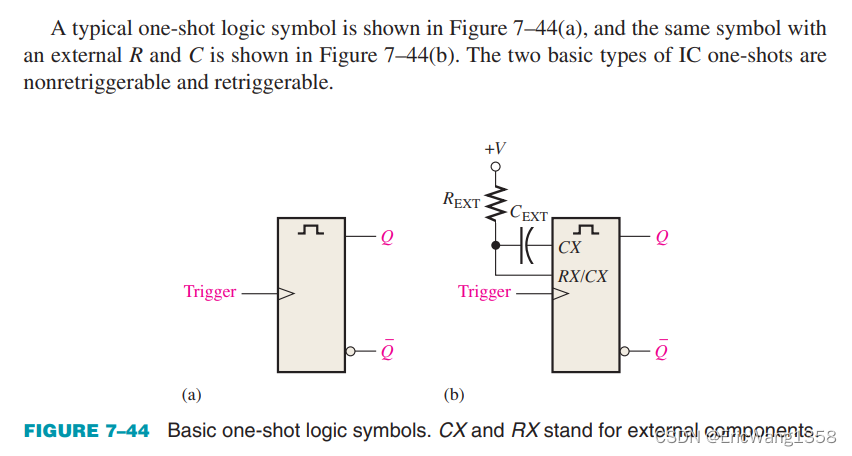

7–5 One-Shots

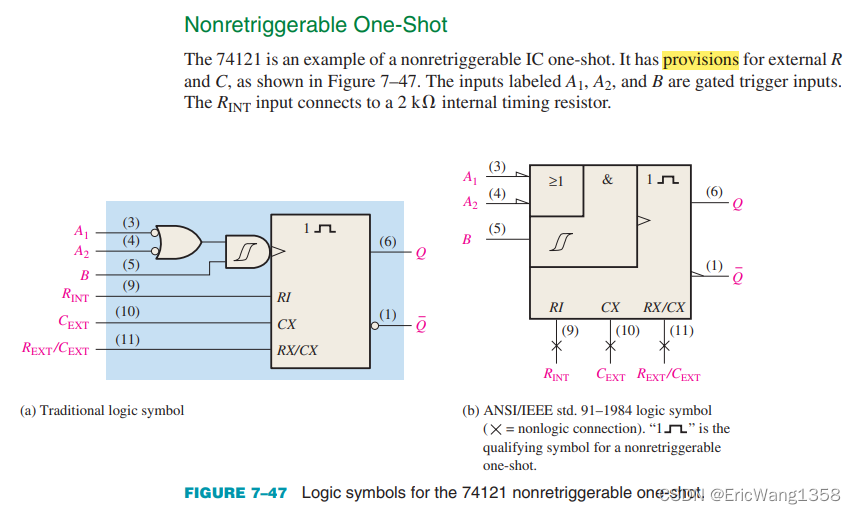

2. Nonretriggerable One-Shot

在这里,“provisions”是指集成电路(IC)74121提供了外部R(电阻)和C(电容)连接的可能性。这个词通常在技术文档中用来指“提供”或“预备”,在这个上下文中,它意味着这个IC设计上允许用户连接外部的电阻和电容,这样可以让用户根据需求设定时间参数。这些外部组件用来影响IC的触发时间特性。

在这里,“provisions”是指集成电路(IC)74121提供了外部R(电阻)和C(电容)连接的可能性。这个词通常在技术文档中用来指“提供”或“预备”,在这个上下文中,它意味着这个IC设计上允许用户连接外部的电阻和电容,这样可以让用户根据需求设定时间参数。这些外部组件用来影响IC的触发时间特性。

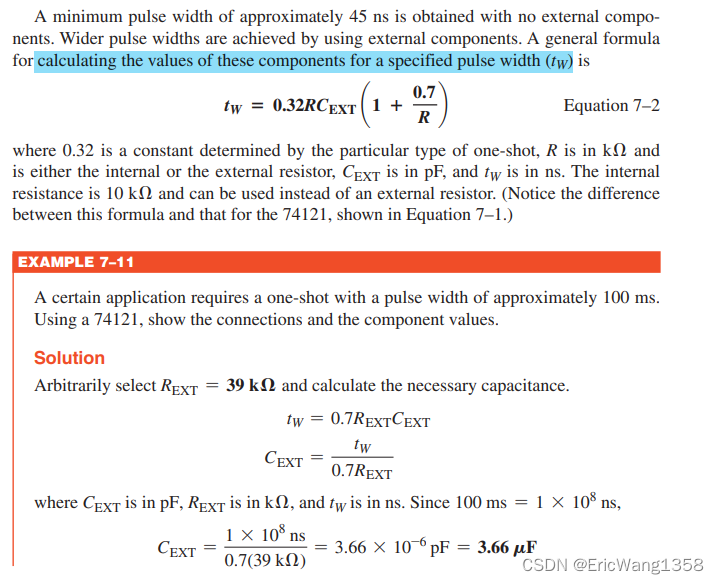

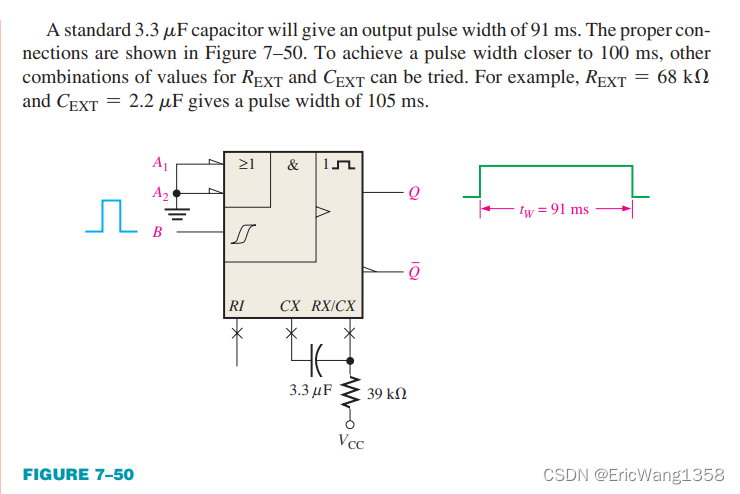

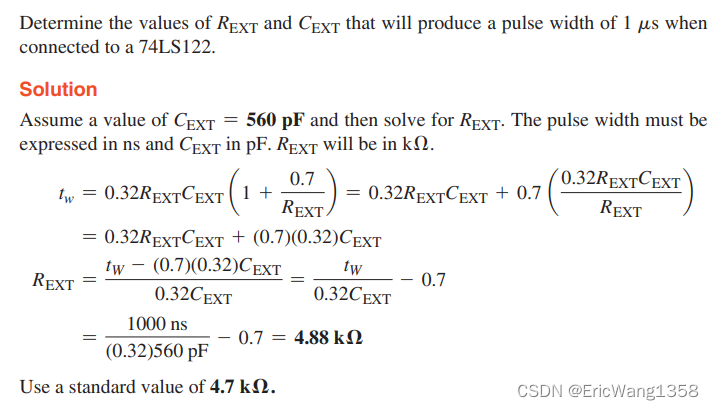

3.Setting the Pulse Width

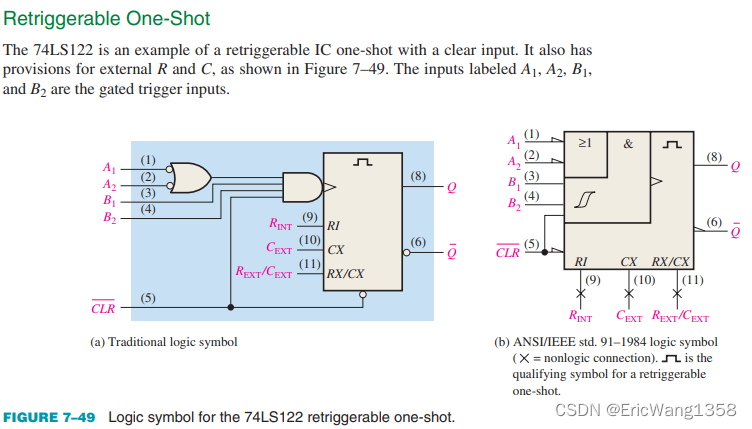

4. Retriggerable One-Shot

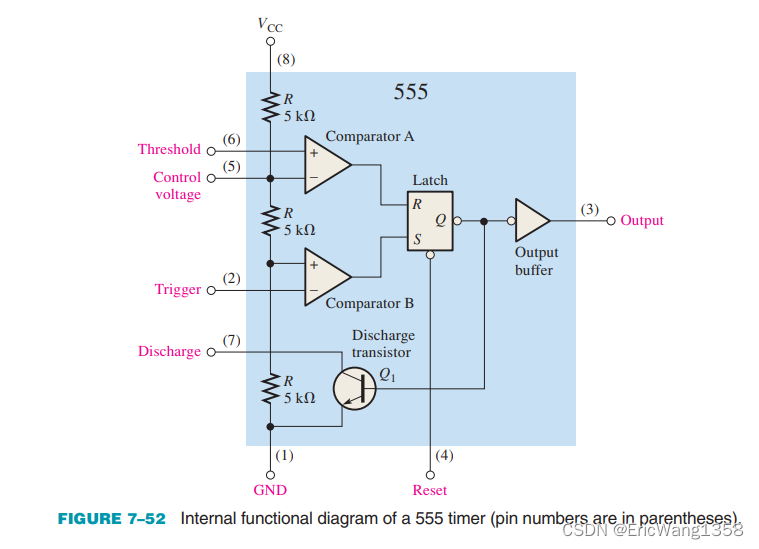

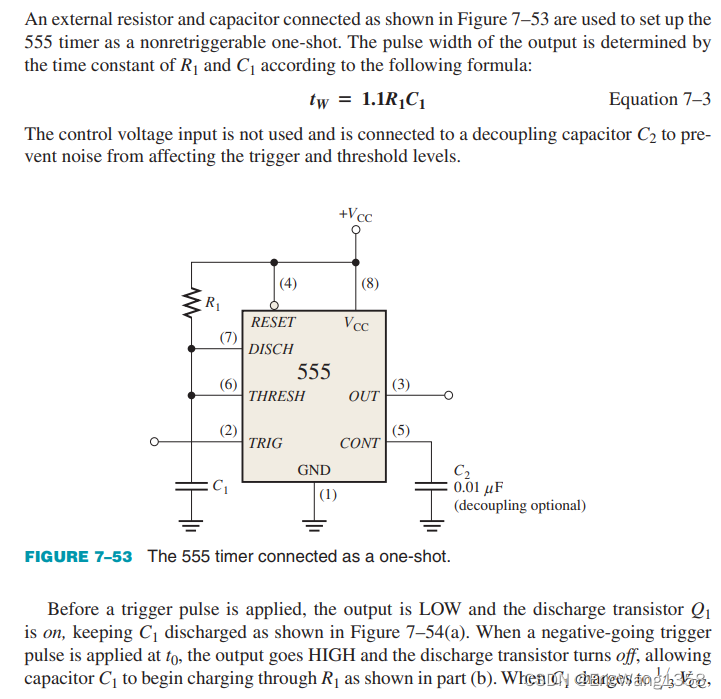

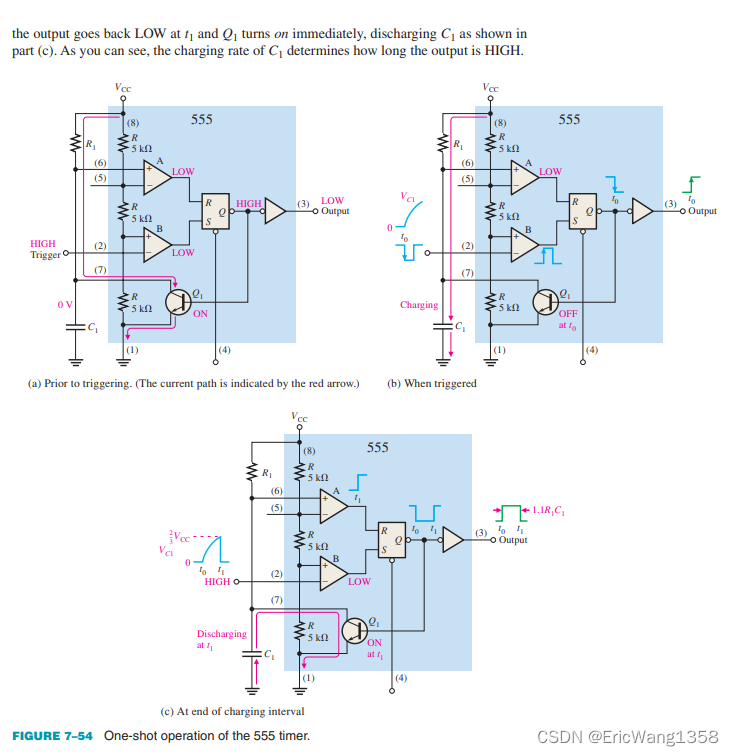

5.The 555 Timer as a One-Shot

5.The 555 Timer as a One-Shot

Monostable (One-Shot) Operation

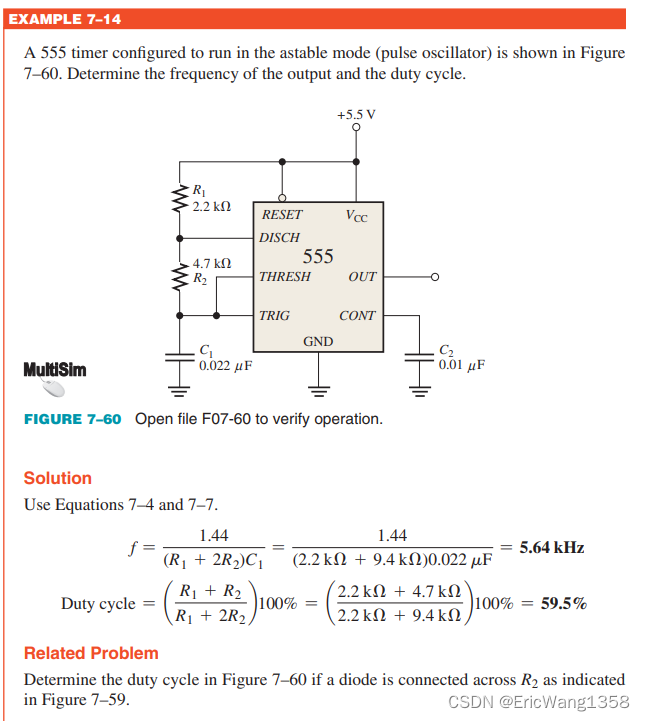

7–6 The Astable Multivibrator

7–6 The Astable Multivibrator

本文详细探讨了数字逻辑电路的关键组件如DFlip-Flop、J-KFlip-Flop以及它们的边缘触发版本,包括7-3Flip-Flop的特性如延迟时间和设置时间。此外,还涉及One-Shot的应用,如非重触发和可重触发,以及555定时器作为One-Shot的使用,以及Astable多谐振荡器的作用。

本文详细探讨了数字逻辑电路的关键组件如DFlip-Flop、J-KFlip-Flop以及它们的边缘触发版本,包括7-3Flip-Flop的特性如延迟时间和设置时间。此外,还涉及One-Shot的应用,如非重触发和可重触发,以及555定时器作为One-Shot的使用,以及Astable多谐振荡器的作用。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?