FPGA学习--Quartus Ⅱ实现3-8译码器设计

一、工程建立

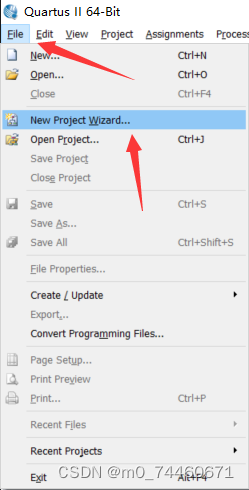

1、点击File中的New Project Wizard,新建一个工程

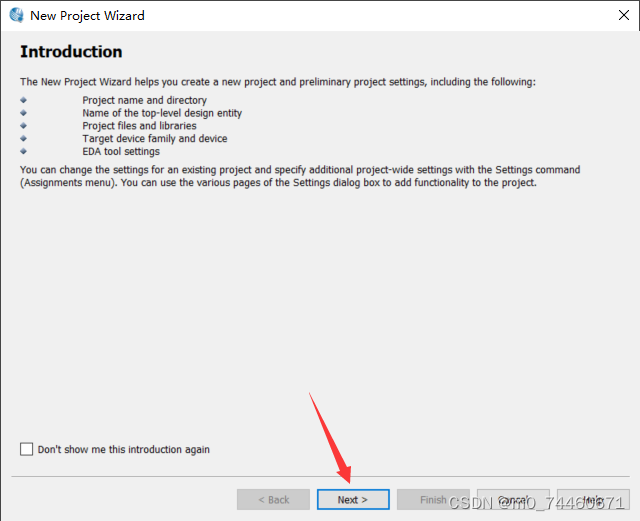

2、出现如下图所示的界面,直接点击Next,不需要其他操作

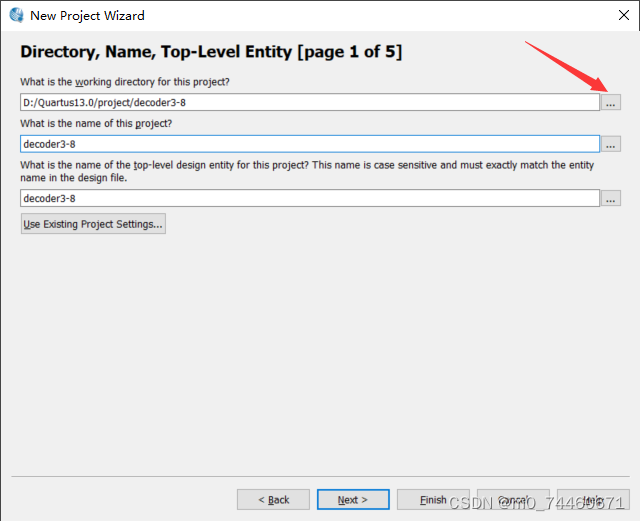

3、点击Next之后,出现以下界面,其中第一栏为工程路径,注意路径中不能出现中文!!!

第二栏为工程名,这次实现的为38译码器,工程名为decoder3-8。

第三栏为顶层名,一般在写了第二栏之后第三栏会自动与第二栏保持一致。

全部弄好之后点击Next

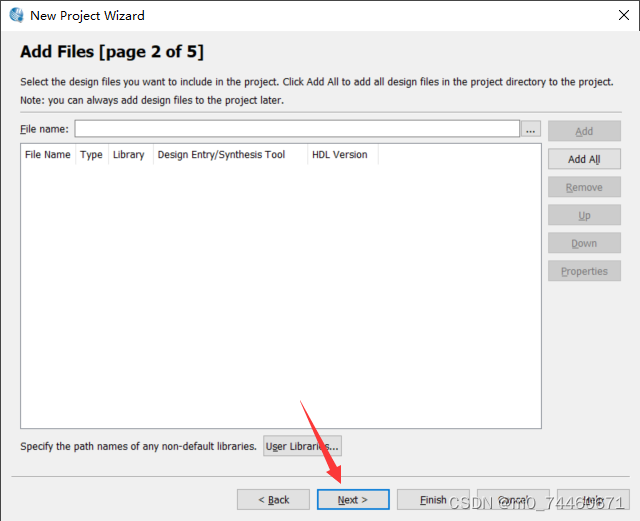

4、这个是添加设计代码的地方,不用管它,直接点击Next

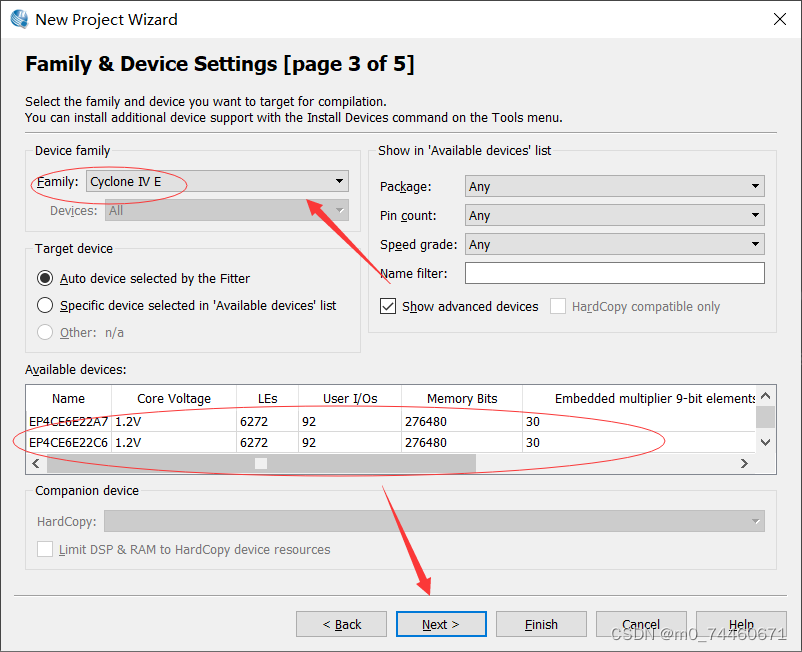

5、这个页面主要是选择开发芯片型号,而我们只需要仿真,所以直接点Next就行

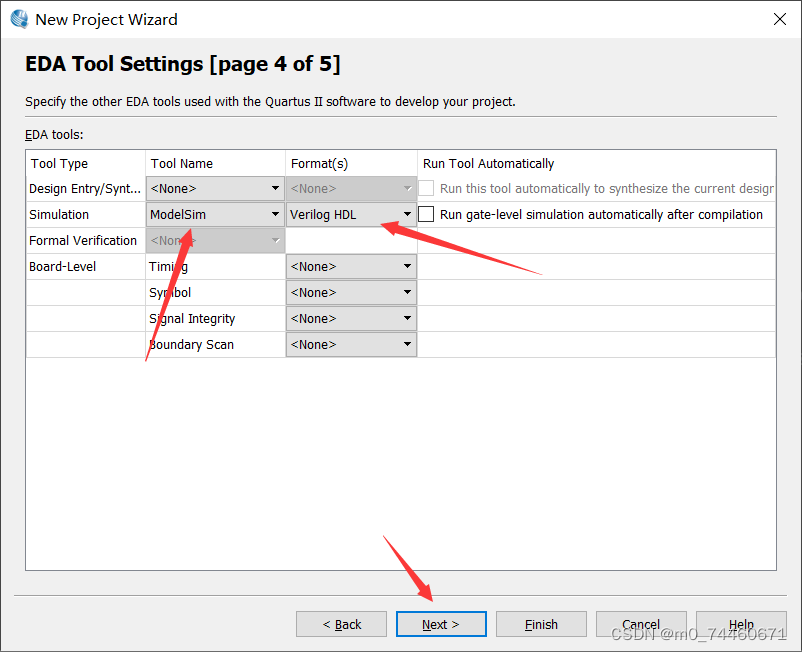

6、因为要调用modelsim仿真,所以这里仿真就选择modelsim,语言的话,我们使用的是verilog HDL。然后点击Next。

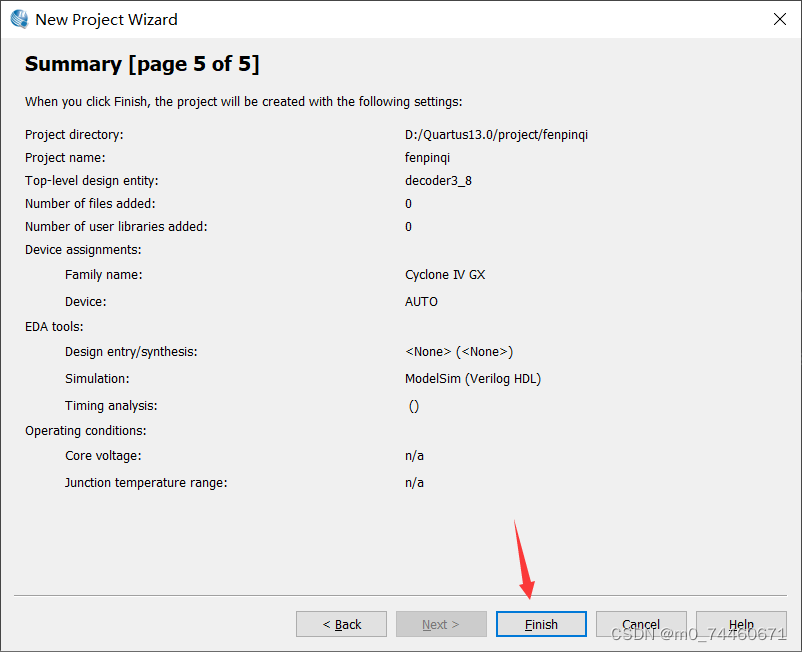

7、这个界面就是一个你的所选清单,直接点击Finish。

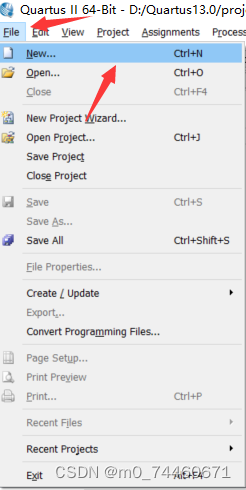

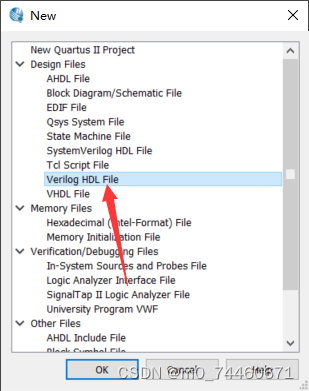

8、点击File-New,或者直接快捷键Ctrl+N,选择verilog HDL文件,这里我们的所有前期工作已经完成,后面就可以开始编程了

二、程序编写

下面是我写的38译码器的代码,你们稍微改一下就可以拿去用了

module decoder3_8(A1,A2,A3,out);

input A1;//输入信号A1

input A2;//输入信号A2

input A3;//输入信号A3

output reg [7:0]out;//8位输出信号

always@(A1,A2,A3)

begin

case({A1,A2,A3})

3'b000:out=8'b0000_0001;

3'b001:out=8'b0000_0010;

3'b010:out=8'b0000_0100;

3'b011:out=8'b0000_1000;

3'b100:out=8'b0001_0000;

3'b101:out=8'b0010_0000;

3'b110:out=8'b0100_0000;

3'b111:out=8'b1000_0000;

default:out=8'b0000_0000;

endcase

end

endmodule

编译

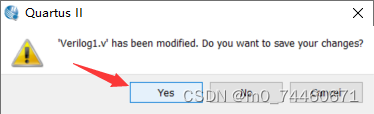

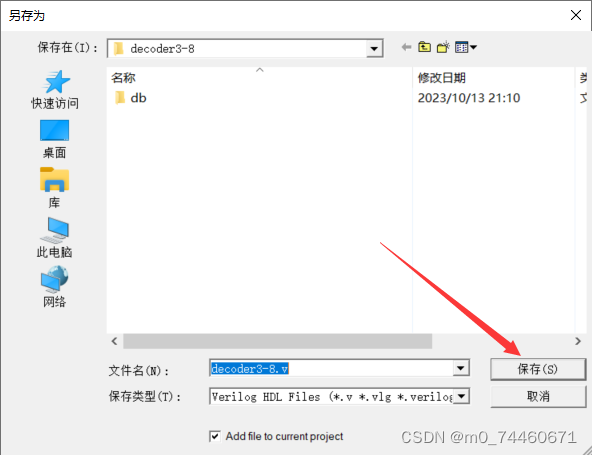

编译的步骤就按照下面的几个图就行了,这里就不多讲了

出现问题

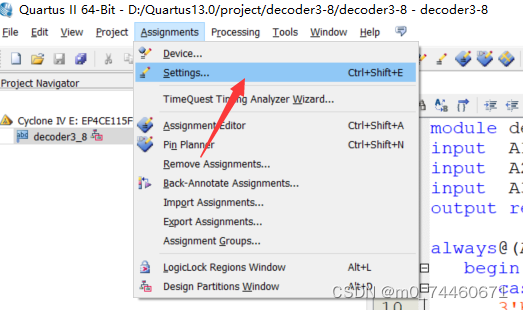

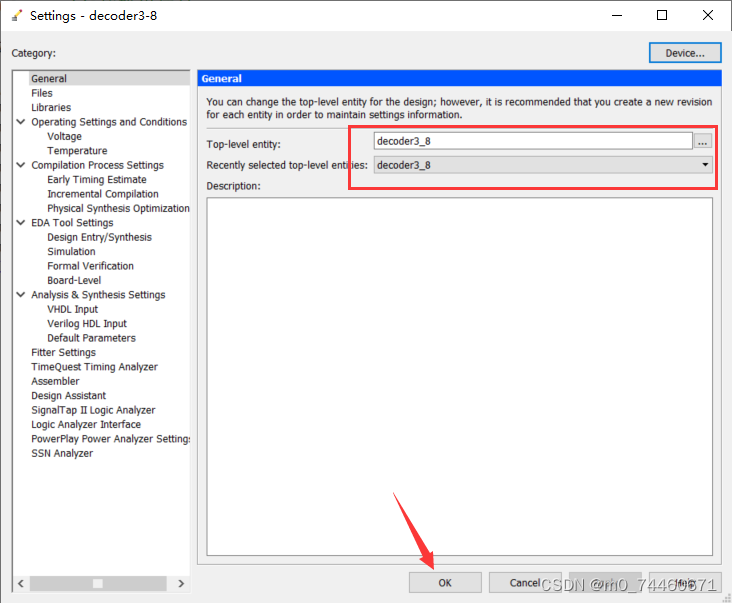

在编译过程中出现了一点问题,显示错误的是Error (12007): Top-level design entity "decoder3-8" is undefined

(有相同问题的可以按照下面给的方法试一试)

这里就需要修改顶层模块名字,方法:Assignments -> Settings -> Top-Level Entity ->Select your module,全完成之后点击OK,再重新编译就行了。

如下图所示

仿真

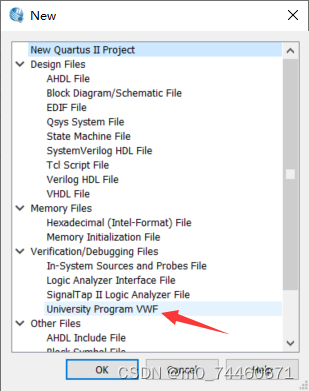

1、像之前一样的步骤建立University Program VWF文件,点击File-New,或者直接快捷键Ctrl+N,选择University Program VWF文件

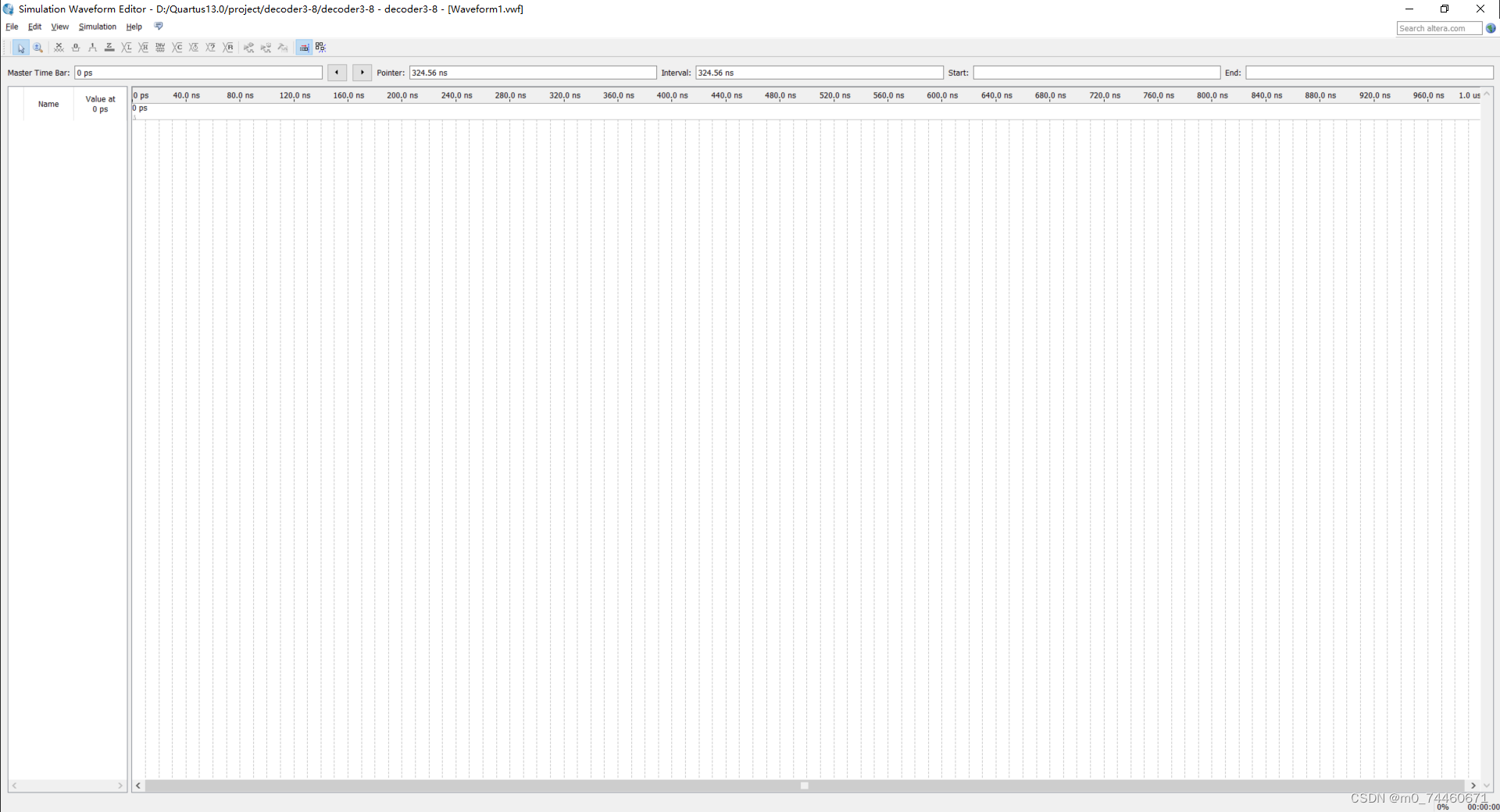

2、点了University Program VWF文件,就会跳出下面的界面

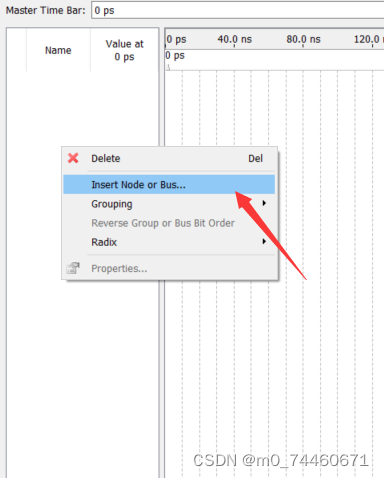

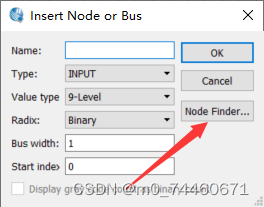

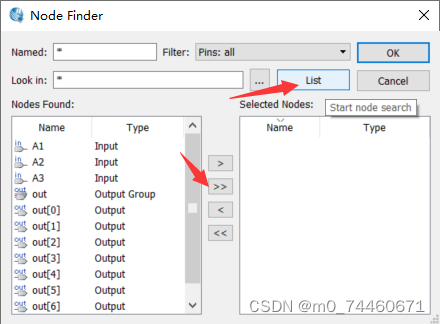

3、这时我们要在界面左侧Name一栏下面点击鼠标右键,选择第二个Insert Node or Bus 选项

然后选择Node Finder选项,点击list选项后,点击右移符号

这样我们就导入了输入和输出

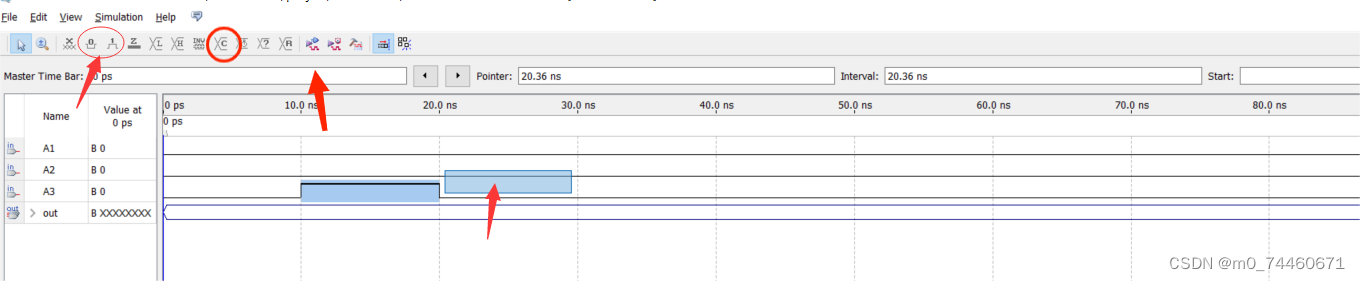

4、导入之后我们就开始给每一段的输入电平,然后进行仿真

这里介绍两种给电平的方法,第一种是选中一段输入,然后选择上面的高低电平(用细线圈出的0、1)

第二种是直接点击输入(A1、A2、A3),再点击(粗实线圈出的)C,自己选择进制,起始值,步进值以及每一段时长

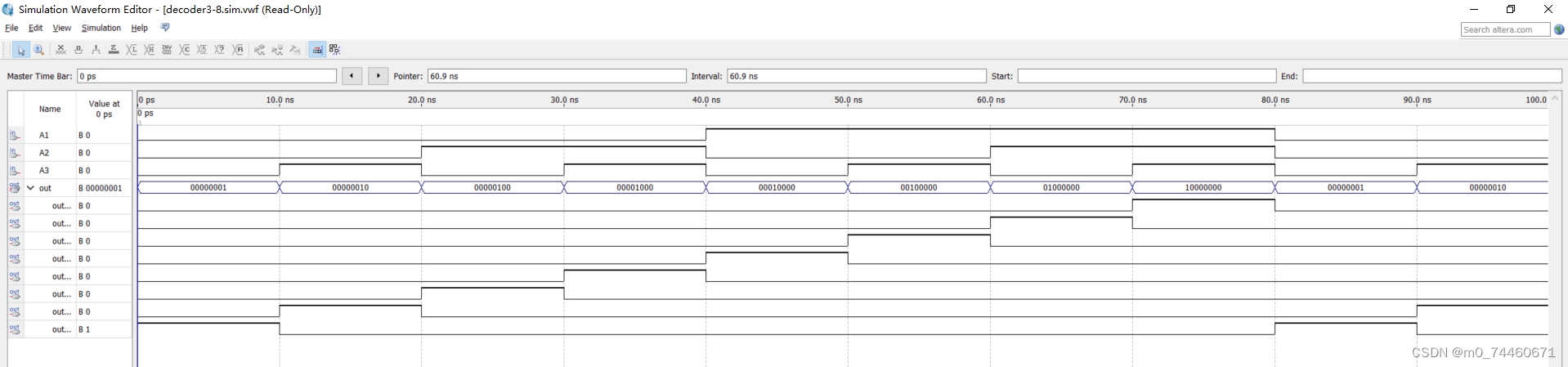

下面这个为最后的仿真结果

补充

作者我也是FPGA初学者,哪里有问题还请见谅,有问题的可以私信我

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?