在介绍模拟地与数字地之前先介绍一下地的含义

”地“我们一般指的是电位为0的地方,或者说是一个电位的参考点(也就是电压参考基点)

在电路设计,或者pcb设计中我们通常会遇到各种各样的地,比如模拟地,数字地,电源地,信号地,机壳地等等,下面稍微介绍一些这些地:

首先是数字地(DGND),又叫做逻辑地:通常是MCU 编码器,干簧管,蜂鸣器等这些数字电路所接的地 ;

模拟地(AGND):像运算放大器,ADC等这些模拟电路接的地就是模拟地;

电源地(PGND):电源模块所接的地就是电源地;

(上面三个一般是出现最多的)

其他还有

机壳地:指的是我们的外壳接地

信号地:各类传感器的地

交流地:电源为交流电源的电压参考基点

直流地:交流变直流时的电压参考基点

还有功率地等等,就不一一介绍了。

数字地和模拟地

接下来我们重点讲讲数字信号和模拟信号,还有数字信号与模拟信号之间是怎样相互影响的。

模拟信号是一串连续的电流或者电压的变化,对外界的敏感度比较高,很容易受到外界干扰

模拟信号特点:信号电平低,频带宽,容易受到外界干扰。

数字信号就是0,1的高低电平,很难受到干扰,数字信号可以产生多次谐波

数字信号 特点:电平幅度从0~1变化大,频率高,上升下降时间很短,谐波丰富,频域宽广,同时由于电平变化快,在电平翻转过程中会短暂的从电源吸入大电流造成公共路径的压降突变,容易产生噪声。

数字电路与模拟电路混合构成,数字信号里的多次谐波进入模拟信号里面就会非常影响模拟信号的工作,因此在布线时就需要考虑它们之间互相干扰问题,特别是地线上的干扰。

面对这种干扰,我查到的资料说的最多的就是单点接地,下面就介绍一下什么叫单点接地

单点接地

单点接地:模拟电路的地平面和数字电路的地平面中间只通过一个点进行连接或者模拟电路的地和数字电路的地分别同功率信号的地平面只通过一个点连接,它将多个地集中连接到一个共同的地点,来确保系统的安全性和可靠性。简单来说就是把模拟地,数字地,信号地等等全连在一点来减少干扰,一般来说,我们都是把电源地当作这个公共的地点。

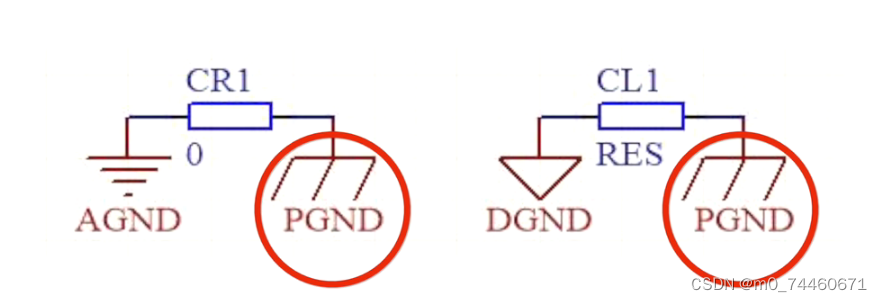

单点接地如上图所示,我们在两个地之间加上0欧电阻或者磁珠。

这里的话就需要选择0欧电阻还是磁珠了

一般的话,0欧电阻全频段都可以用,磁珠一般适用高频

0欧电阻和磁珠区别

0欧电阻上面有着阻值标识,符号就是电阻符号--阻性元件就是纯粹的电阻,但并不是真正意义上的0欧姆,而是阻值很小的一个电阻(阻值小于或等于50毫欧姆)

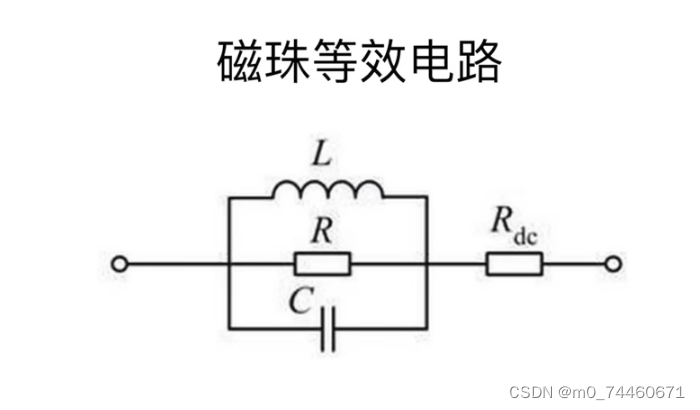

磁珠(铁氧体材料)上没有热门和显著的标识,我们浅显的可以把它看作一个电感,但是磁珠的特性和参数标注和我们平常使用的功率电感或者是谐振电路使用的电感是完全不一样的;

磁珠的主要作用是抗干扰,吸收高频的一个噪声和尖峰干扰

在所有磁珠的参数中都会有两个明显的参数,一个是频率,一个是电阻值,比如“1k欧姆,100兆赫兹”代表着该磁珠在100兆赫兹下所拥有的电阻值是1k欧姆,一般来是所拥有的电阻值都是比较大的,会是上百甚至上千欧姆,但是他们的直流电阻会比较小,往往只有0.05欧姆,所以磁珠也可以用在单点接地

铁氧体材料特点是导磁率高,可以是线圈绕组在高频的特性下电容值也非常小

铁氧体一般在高频情况下应用,因为他们在高频的时候阻抗会比较大,所以磁珠一般适用高频

磁珠等效电路模型我们可以理解为一个电感和一个电阻的并联,在低频的时候电阻被电感短路,此时电感上的损耗较小;在高频的时候,他的阻抗是随频率变化的,电感上的阻抗会非常大,迫使电流经过电阻,此时在电阻会产生一个热量功率上的损耗,这个损耗由于电阻特性会变成热量耗散出去,产生一个能量的转换

两者最大区别:能量的转换形式,一个是耗能元件,一个是储能元件,

1252

1252

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?