由于人工码字太慢,所以文章的更新会比较的慢,以太网接口系列估计要花个一两周时间才能更新完。

作为IP核手册翻译大师,接下来就真正开始翻译Xilinx的IP核手册了。

本系列将会分为:基本知识、接口的基本结构、IP核的配置、接口的测试与使用等章节。

上回说到设计接口所需要的一些基本知识,如果忘记了的可以回过头去看看⬇️。

十二点过九分:10G以太网接口(一):基本知识123 赞同 · 14 评论文章正在上传…重新上传取消

本篇文章主要讲讲10G以太网接口的基本结构,本质上还是属于该掌握的基本知识,还没有涉及到设计的部分。但是本部分大量参考自Xilinx的IP核手册,具体参考可详见文章末尾。

10G以太网接口基本结构

上篇文章简单说了接口的结构,我们知道以太网接口就是个搬运工,把MAC层来的数据报打包搬运到“货车上”(光纤等),或者是把“货车上”的卸下来拆了包装盒送到MAC层,对包装盒装的啥东西根本不关心。

介于笔者的目的是采用进行光纤通信的,所以选择的也是10GBASE-R标准作为讲述对象。

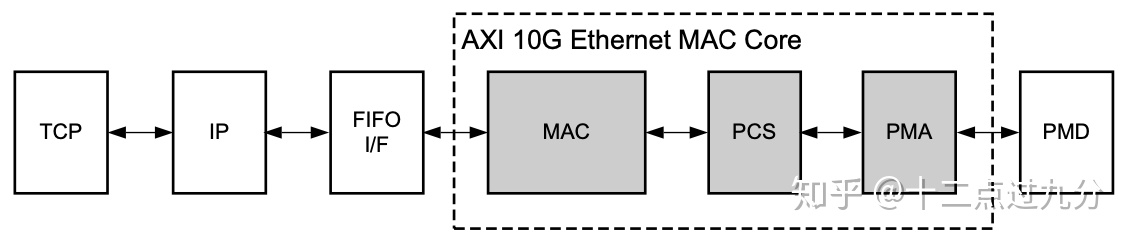

下图是一个以太网系统的典型结构图[1]。

Typical Ethernet System Architecture

从典型结构图中可以看出,接口的部分由PMD、PMA、PCS和MAC子层组成:

- 其中在设计当中PMD子层一般使用光模块代替,实现光电/电光转换,这样高速数据就可以在光纤中得以传输;

- 而接口的PMA、PCS和MAC的部分在设计中一般采用IP核实现设计,如上图中就采用了10G Ethernet Subsystem实现这部分设计。

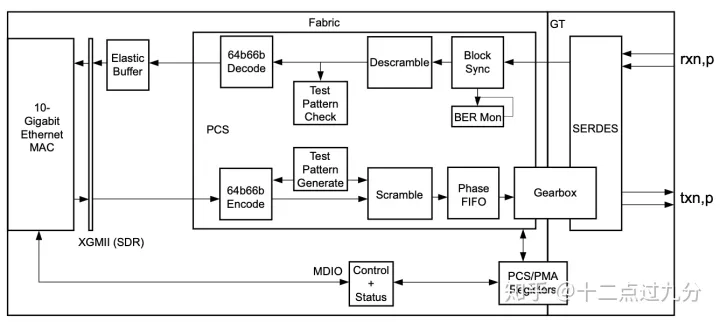

下图是Xilinx 文档PG157中的10GBASE-R标准的结构图[2],实质上对应的就是上面那个典型结构图中的PMA、PCS和MAC部分。

10GBASE-R 结构图

从上图中可以看出:

- PMA层对应就是GT部分,利用SerDes技术实现:对光模块来的数据(rxn,p)进行时钟恢复,并将串行信号转换为并行66bit位宽的数据,对应时钟为156.25 MHz,可计算出速率为10.3125 Gbps;对PCS层来的66bit位宽、156.25 MHz的数据转为串行数据(txn,p)再传输到光模块;

- PCS层如图所示包括64b/66b编解码器、绕码/解绕码等,该部分是为了将PMA层来的数据进行解绕码、将66b位宽解码成64b位宽,即转为64bit位宽、156.25 MHz的数据了;对MAC层来的数据进行信道编码(64b/66b编码)、绕码等操作送入信道传输;

- PCS子层与MAC子层之间使用XGMII接口连接,该接口传输的数据其实已经是完整的以太网帧数据(包括了前导码、FCS等部分)。如果自行设计MAC的话,可以直接将XGMII对接到MAC上;

- MAC部分将在下一小节详细讲述。

MAC层

让笔者自行设计MAC?

设计是不可能设计的,这辈子都不可能设计,只有使用Xilinx的MAC核才能维持得了生活。

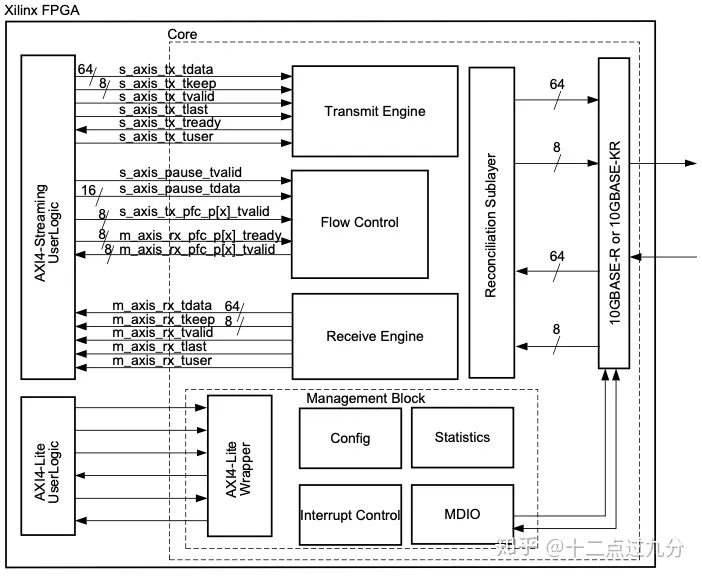

下图就是Xilinx文档PG157中的MAC核的结构[3]。

Xilinx 10G MAC核的结构

从上图中可以看出:

- MAC核基本上由数据传输引擎、流控制、MAC核配置和状态信号等部分组成;

- 数据传输引擎主要完成:将来自XGMII的数据,去掉前导码、起始符和帧校验序列(FCS),转为MAC帧(没有FCS的)传输到更高层,帧与帧之间有帧间隔;将MAC层的数据,计算FCS、增加前导码和起始符,封装的数据帧按照规则形成帧间隔,转为XGMII接口数据送到物理层用于传输;

- 至于什么是流控制目前还不清楚,之后了解后再补上,还望不吝赐教;

- 配置和状态信号主要用于配置MAC核的一些参数以及输出一些传输过程中的状态信号,这个在下篇文章会提到;

- 值得注意的是:Xilinx的很多IP核都采用AXI接口,至于什么是AXI接口可以参考下面的系列文章;

ljgibbs:深入 AXI4 总线(一)握手机制347 赞同 · 44 评论文章正在上传…重新上传取消

时钟结构

以上详解了接口的结构,接下来就是时钟。在使用中发现7系的芯片和UltraScale芯片对应的IP核有很大的出入,这个在之后的IP配置中会详解,这里只比较7系的IP核的时钟结构和UltraScale系列IP核的时钟结构。

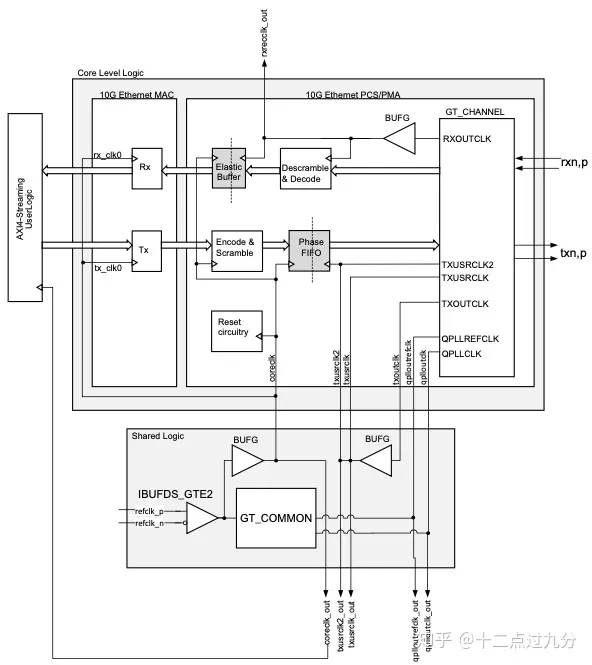

下面是7系芯片对应的IP核的时钟结构。

7系 时钟结构

值得注意的是:

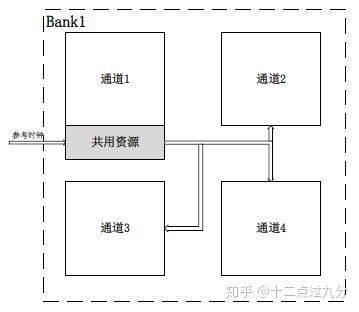

- 在7系中可以发现,如果使用10G Ethernet Subsystem IP核,它会有shared logic这样的结构。当然只使用一个10G口,那么可以直接无脑勾上,但是如果想做一个8*10G或者更多口的万兆交换机,如果每个都选上shared logic那么就会出现资源不足的情况,主要就是GTCOMMON和IBUFDS_ GTE2资源不足,解决方法就是:如下图所示,先配置一个带shared logic的IP核,再配置一个不带shared logic的IP核;然后10 G通道1例化使用这个带shared logic的IP核,通道2、3、4例化使用不带shared logic的IP核,这样实现4个10 G通道共用这部分资源,这其实也是Xilinx希望这么做的;

四个10G通道共用时钟资源图示

- 其他时钟就如图所示,IP核需要一对频率为156.25 MHz的差分参考钟,如果PCS/PMA和MAC都使用的话,coreclk_out就是供用户逻辑使用的时钟,同样为156.25 MHz;

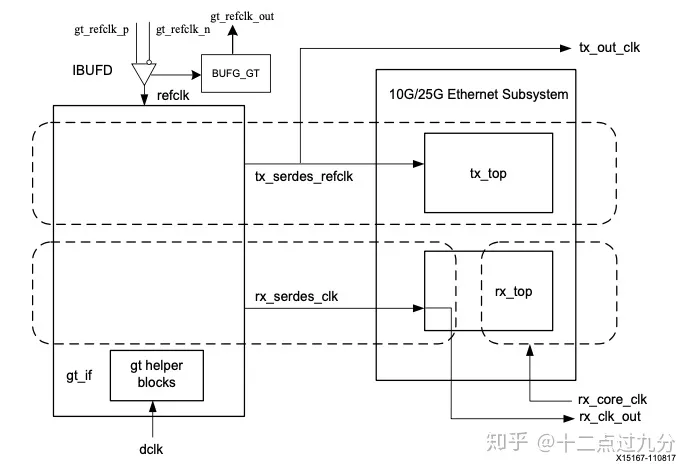

下面是UltraScale系列芯片对应IP核的时钟结构[4]。

UltraScale系列 时钟结构

值得注意的是:

- 与7系不同的是,它不用特意操作一番供多个10G口使用了,具体操作会在下篇文章说明;

- 同样它也需要一对差分钟,但是用户逻辑可以使用的时钟变成了tx和rx分开了,也就是必须按照手册去对应状态信号也好、以太网数据也好,是工作在哪个时钟域下的,如果有问题的话可能就要进行跨时钟处理了。

其他

上面其实也提到了,在实际设计过程中,使用Xilinx的芯片,由于7系和UltraScale系列的架构不同,对应的IP核也有所区别,使用这些IP核的过程中需要仔细阅读官方手册,笔者因为能力有限,也只是分享自己学习过程中的一些理解,看官方手册还是最为直接最为清楚的学习方式。

其他内容有待补充~

10G以太网接口(二):接口的基本结构 就介绍到这儿,(三)、(四)已更新⬇️。

十二点过九分:10G以太网接口(三):IP核的配置32 赞同 · 6 评论文章正在上传…重新上传取消

十二点过九分:10G以太网接口(四):测试与使用38 赞同 · 15 评论文章正在上传…重新上传取消

写在最后:

以上基本介绍了10G以太网接口的基本结构,当然不是说需要我们手撸RTL实现这样复杂的逻辑,需要掌握的是一些基本概念,这样在使用IP核实现设计的时候也能知道这个IP是怎么实现的。

当然,笔者作为新手,水平有限,还需要学习一个,还有不足之处还望批评指正~

本文详细介绍了10G以太网接口的基本结构,包括PMD、PMA、PCS和MAC子层,强调了光模块在接口中的作用以及Xilinx IP核在设计中的应用。MAC层由数据传输引擎、流控制等部分组成,时钟结构在7系和UltraScale芯片中有所不同,对于多接口共享资源提出了解决方案。

本文详细介绍了10G以太网接口的基本结构,包括PMD、PMA、PCS和MAC子层,强调了光模块在接口中的作用以及Xilinx IP核在设计中的应用。MAC层由数据传输引擎、流控制等部分组成,时钟结构在7系和UltraScale芯片中有所不同,对于多接口共享资源提出了解决方案。

6952

6952

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?