由于该系列文章阅读有顺序性,所以请跳转至该系列文章第一篇从头开始阅读,并按照文章末尾指示按顺序阅读,否则会云里雾里,传送门在此: https://blog.csdn.net/qq_33486907/article/details/110180317 《10G_Ethernet_01 万兆以太网设计引言》

目录

对 IP 进行快速验证, 充分利用 Example Design 是最省时省力的,只需要对代码进行很小的改动甚至无需进行改动就可以完成对 IP 的快速验证, 当然这得建立在对Example Design 和 Test Bench 有清晰的认识的情况下进行,如果还未了解请回顾前 3三篇博客的内容。

1 验证方案

在只有一个开发板的情况下,可采用该方案完成对 IP 核的测试验证, 方案如下图(方案以 10Gbase-R 为例):

方案中 Example Design 的模式应该设置为仿真测试中的 BIST 模式一样即可,关键点如下:

(1) 启用模式发生器和检查器;

(2) 串行接收器链路连接到发送器链路(直接使用光纤短接);

2 验证实验

本节以自环回验证为例,使用 XILINX 官方开发板 KC-705 对 IP 核进行验证;

(1) 建立一个自带 10G Ethernet Subsystem IP 核的工程, 特别注意在建立工程时,应选择 KC-705 开发板进行建立;

(2) 在建立的工程中,对 10G Ethernet Subsystem 创建 Example Design;

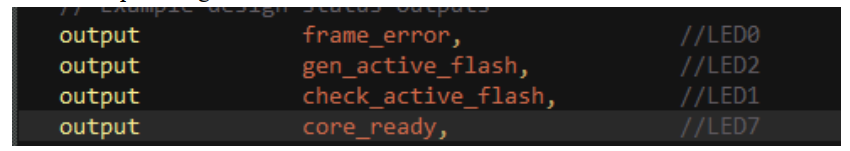

(3) 打开 Example Design 进行 RUN IMPLEMENTED,并进入 IMPLEMENTED DESIGN 的工作界面, 打开 IO PLANNING,这时会发现所有的有关模式配置的管脚已经映射到了开发板上的 DIP 管脚上,同时所有的状态输出管脚全部映射到了开发板的 LED上。

(4)剩下的工作只是 GTX 的参考时钟和 GTX 的通道管脚没有进行配置,只需要把这一步配置做好即可, 这里要注意 FPGA 中 GTX 参考时钟入口与收发器通道的匹配性,具体管脚配置将在给出的 Example Design(定制好的)中给出,关于参考时钟的给定方式

也有多种,可以使用外部信号源,也可以使用板子内部的晶振给定(需要修改一定的代码), 不过有由于 KC-705 板卡的拥有该时钟源的 BANK 和接口的电平与 GTX 收发器的BANK 的电平不匹配,所以采用了外部时钟源输入的方式, 见实物验证图, 图中的同轴

线缆提供了参考时钟, 同时也提供了使用板卡内晶振提供参考时钟的方案,见板卡内参考时钟方案图;(注: 前 3 章内容中有讲解 PHY 的内容,其实 PHY 中 PMA 部分实际是使用的就是 GTX 收发器, 相关内容将在《7 Series FPGAs Transceivers Wizard IP 的验证》中进行讲解)

(5)管脚配置好后,即可生成 bit 文件下载到板卡上进行验证, 验证时注观察相应LED 灯的变化即可, 如图所示:

根据 Example Design(定制好的)的配置,可轻易看出 IP 是否准备好, 帧发生器有没有在进行正常的数据帧发送, 帧检查器有没有在进行正常的数据帧检查,已经是否有发现错误的数据帧。

事物验证图

板卡内参考时钟方案图

(6)以上的相关配置内容,还需要结合 KC-705 开发板的向导资料和原理图等进行。 同时该验证也是众多验证方法方案中的一种而已;

3 如何验证自研板卡的 10G 以太网的功能

上一节中, 采用了自环回的方案讲解了 10G 以太网 IP 的快速验证,那么该方法也同样适用于验证自研板卡硬件是否存在功能性错误; 如果自研板卡与官方开发板类似,拥有 DIP 开关、 连接上下拉电阻的 IO 口、 LED 灯等, 只需要合理分配 Example Design 的模式管脚和状态管脚,即可使 Example Design 进入相应的模式; 如果自研板卡不具备这些条件,则需要对 Example Design 进行一定的移植工作, 例如通过修改代码来达到配置Example Design 模式的目的,以及通过插入片上逻辑分析仪观察状态信号等。

3.1 PCS 环回的作用

在使用 Example Design 测试自研板卡存在问题时, 可能无法定位到底是那一级出现了问题,这时可以启用 PCS 环回, 帧生成器生成帧插入 TX_FIFO,然后通过PCS 环回, 串行链路上没有数据,这样可以将问题定位到外部链路上。

3.2 对误码率的测试

针对测试外部路径的方法这里还可以采用 Integrated Bit Error Ratio Tester 7Series GTX Transceivers 的方案,具体内容将在《7 系列 GTX 收发器集成误码率测试仪》的方案中更新。

4 设计资源传送门

到这里,产生了该系列博客的第一个设计资源,传送门在此: https://download.csdn.net/download/qq_33486907/13196358 《基于FPGA的万兆以太网示例设计 》与上一章节的资源相同。

5 总结

Example Design 实现了以太网数据帧的组帧,包括前导码、 MAC 地址、 CRC 校验码等, 但是这只是实现了 TCP/IP 协议的一部分, 这样的数据帧在自定义数据的网络中已经能够实现数据的收发,但是使用在标准的以太网中功能还不够强大, 后续更新的章

节将以 10G Ethernet system 为核心构建完善的 TCP/IP 协议, 同时会讲解更多涉及到 10G Ethernet system IP 的知识, 以及 TCP/IP 协议方面的知识, 包含如下内容:

使用硬件描述语言构建的 UDP 协议 IP, 并支持 AXI-Stream 协议,实现与 10GEthernet system 系统的无缝对接, 同时支持 ARP 协议,自动获取对端 MAC 地址, 实现多点组网。(支持 UDP 协议、 ARP 协议)

下一篇传送门在此: 《TCP/IP协议简介》

6064

6064

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?