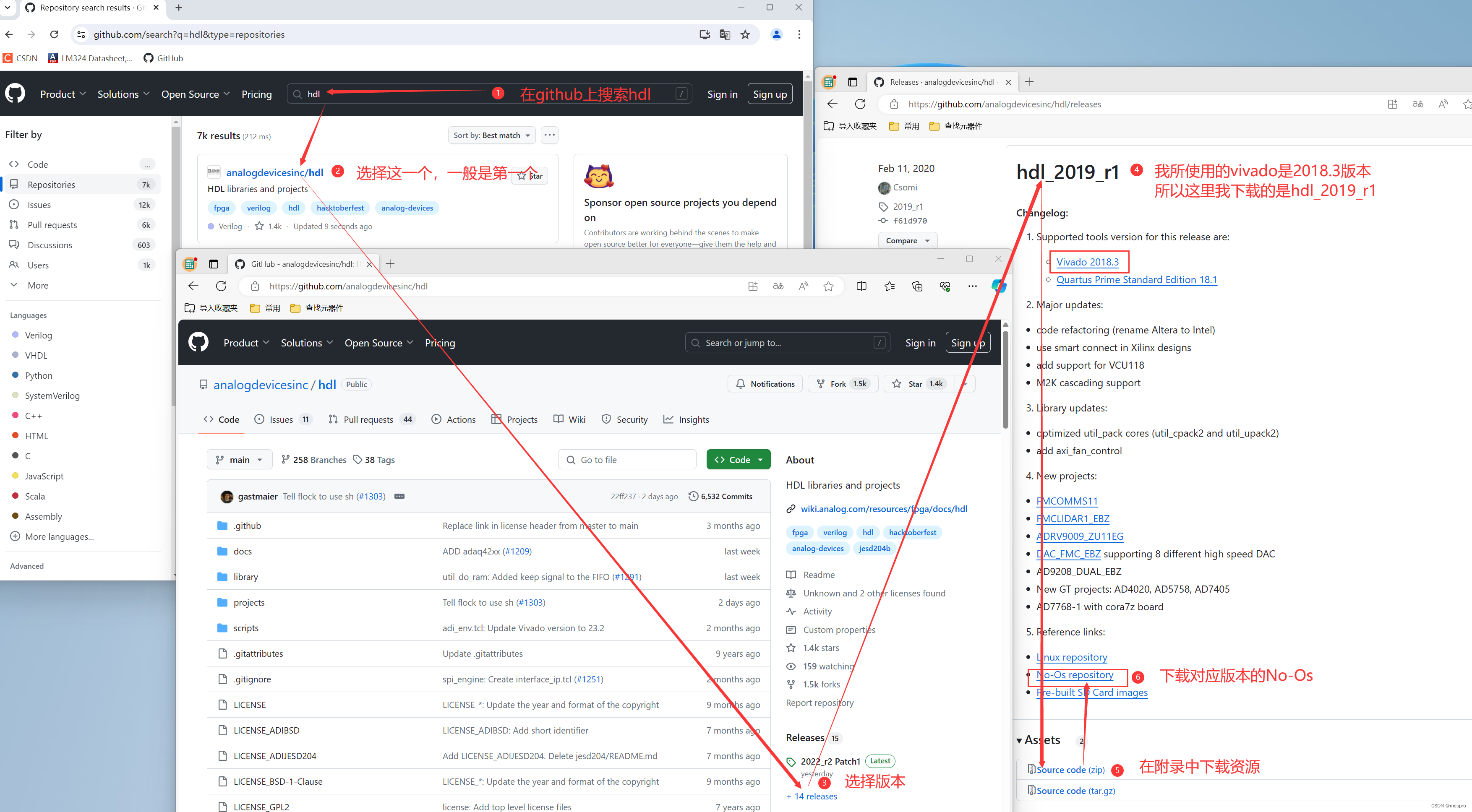

首先需要在github上下载两个文件,本例程用到的文件以及最终文件,我都会放在网盘里面,地址在本文的末尾,需要自行提取

在github上搜索hdl选择第一个-->选择版本-->我所使用的vivado是2018.3版本,所以这里我下载的是hdl_2019_r1-->在附录中下载资源-->下载对应版本的No-Os

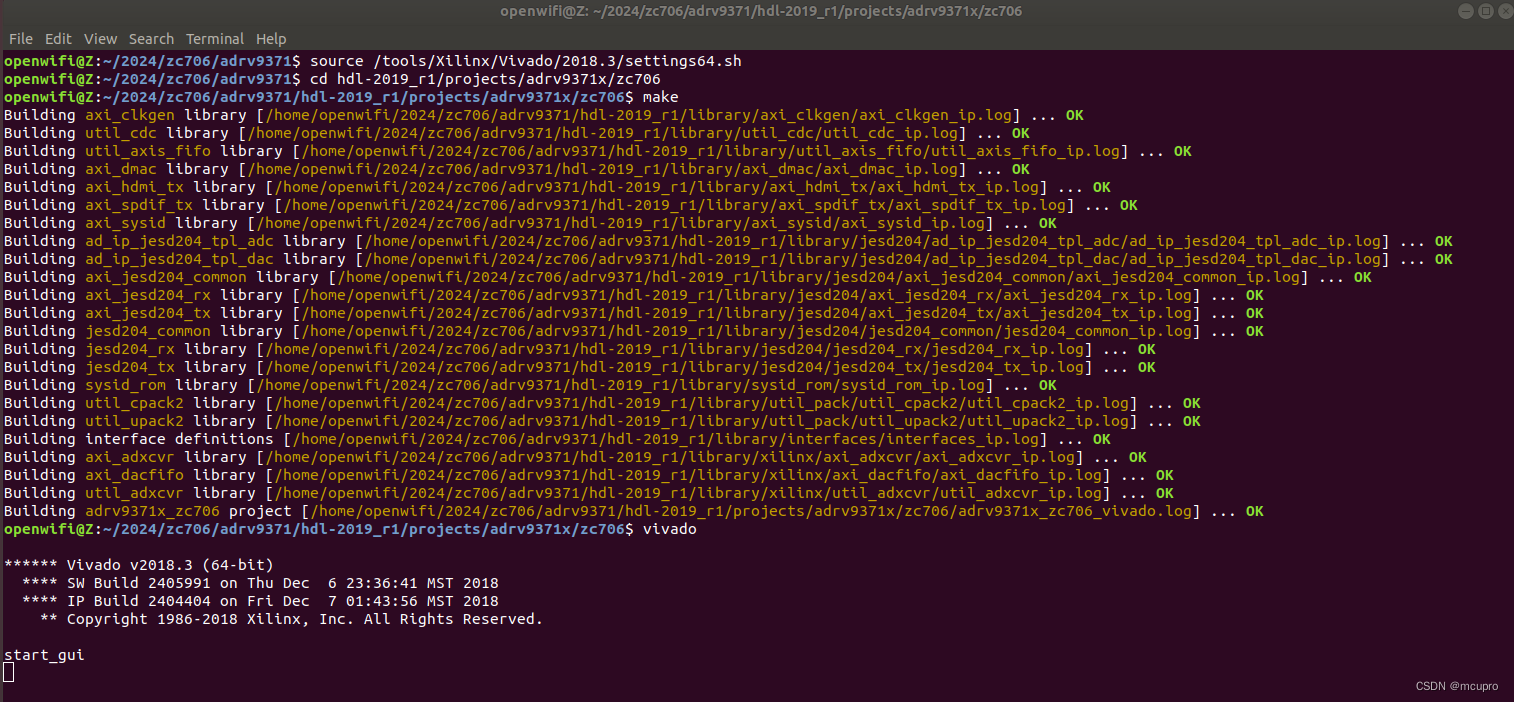

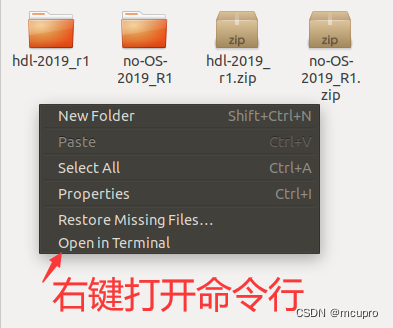

把下载好的资源复制到虚拟机里解压缩,右键打开命令行

设置环境变量-->进入项目目录-->编译-->打开vivado

source /tools/Xilinx/Vivado/2018.3/settings64.sh

cd hdl-2019_r1/projects/adrv9371x/zc706

make

vivado

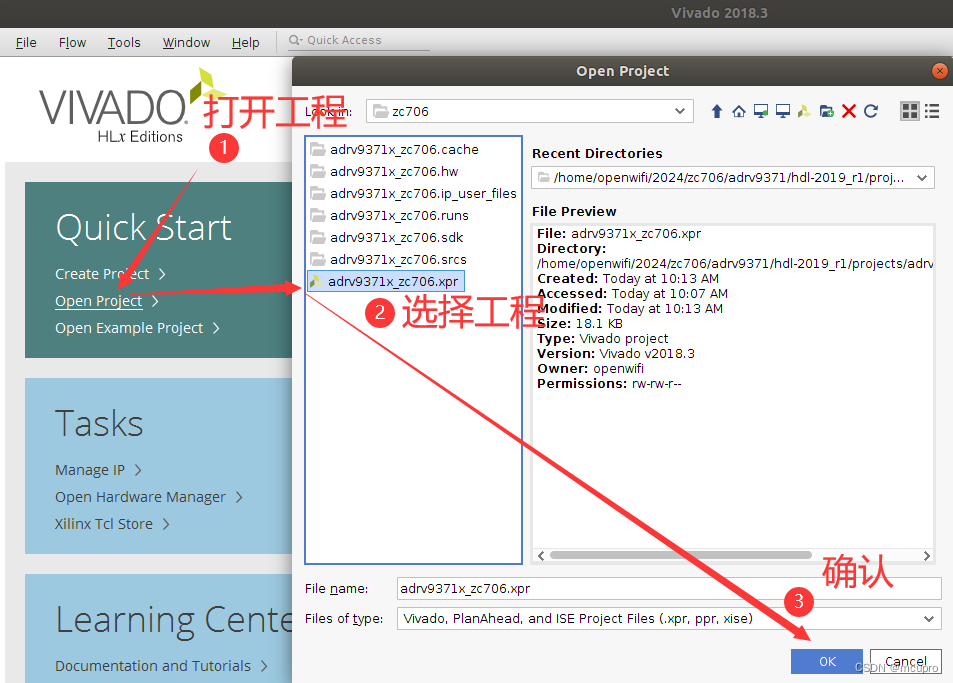

打开工程-->选择工程-->确定

不需要修改直接编译

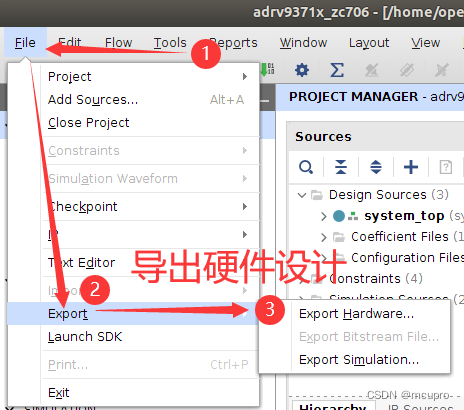

导出硬件设计,后续弹出的提示都选择确认

打开SDK,后续弹出的提示都选择确认

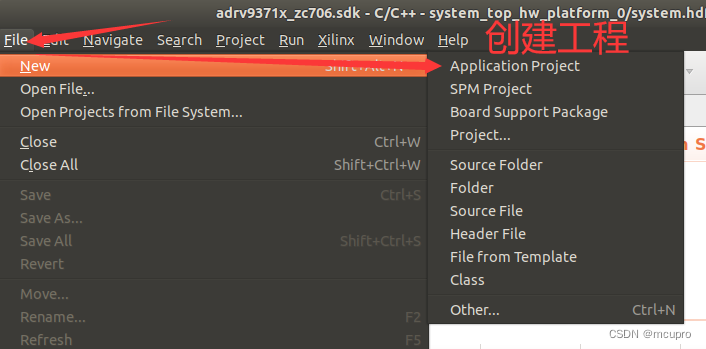

新建项目

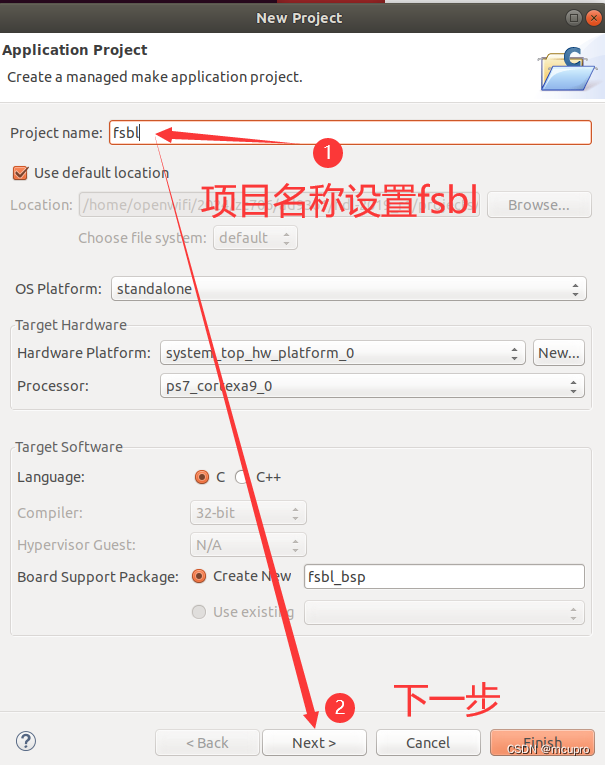

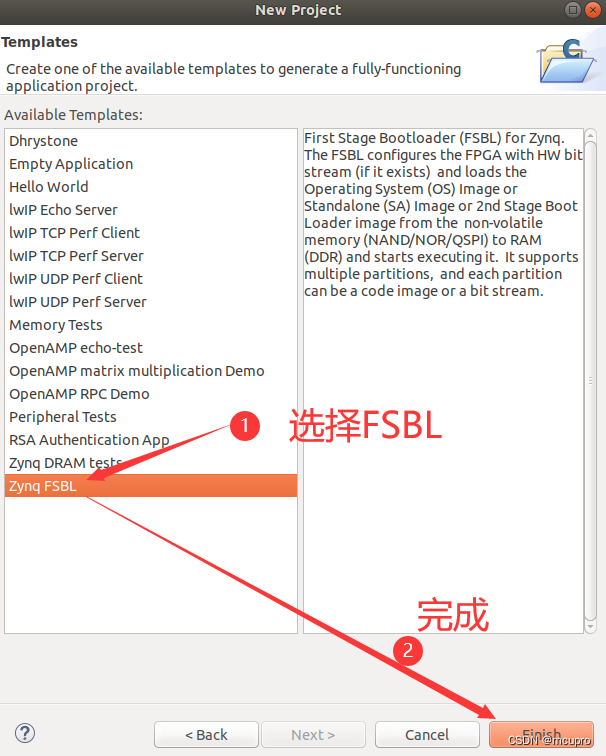

项目名称设置为fsbl-->next-->选择FSBL-->完成。注意SDK不要关闭,后续需要用其生成BOOT.bin

回到最开始的目录,右键再次打开一个命令行窗口

设置环境变量-->进入工程目录-->复制硬件设计文件-->编译工程,等待编译成功

source /tools/Xilinx/Vivado/2018.3/settings64.sh

cd no-OS-2019_R1/projects/ad9371/

cp ../../../hdl-2019_r1/projects/adrv9371x/zc706/adrv9371x_zc706.sdk/system_top.hdf .

make

回到最开始的目录,右键再次打开一个命令行窗口

创建file文件夹-->进入文件夹-->复制fsbl文件-->复制bit文件-->复制elf文件

mkdir file

cd file

cp ../hdl-2019_r1/projects/adrv9371x/zc706/adrv9371x_zc706.sdk/fsbl/Debug/fsbl.elf .

cp ../hdl-2019_r1/projects/adrv9371x/zc706/adrv9371x_zc706.runs/impl_1/system_top.bit .

cp ../no-OS-2019_R1/projects/ad9371/build/release.elf .

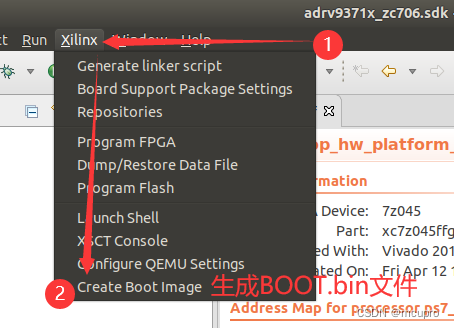

回到SDK,生成BOOT文件

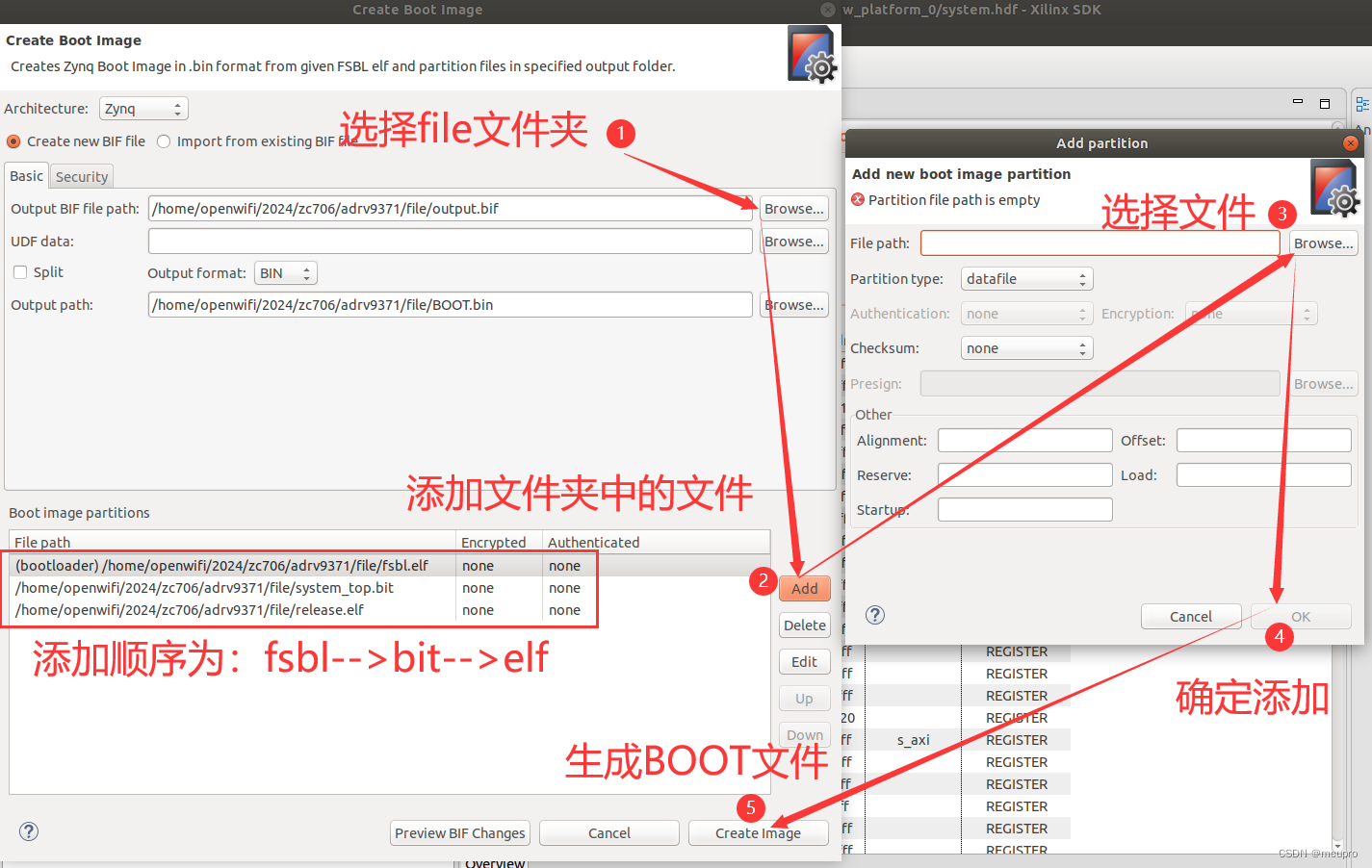

选择file文件夹-->按照顺序添加file中的文件(顺序为:fsbl-->bit-->elf)-->生成BOOT文件

打开file文件夹复制BOOT.bin文件到SD卡中,插入开发板,接好电源,串口线,安装好ADRV9371模块,启动模式设置为SD卡启动

打开串口助手软件,开启电源等待串口打印信息,最后输出Done表示成功

Please wait...

WARNING: AD9528_initialize() issues. Possible cause: REF_CLK not connected.

rx_clkgen: MMCM-PLL locked (122880000 Hz)

tx_clkgen: MMCM-PLL locked (122880000 Hz)

rx_os_clkgen: MMCM-PLL locked (122880000 Hz)

MCS successful

CLKPLL locked

AD9371 ARM version 5.2.2

PLLs locked

Calibrations completed successfully

tx_adxcvr: OK (4915200 kHz)

rx_adxcvr: OK (4915200 kHz)

rx_os_adxcvr: OK (4915200 kHz)

rx_jesd status:

Link is enabled

Measured Link Clock: 122.865 MHz

Reported Link Clock: 122.880 MHz

Lane rate: 4915.200 MHz

Lane rate / 40: 122.880 MHz

Link status: DATA

SYSREF captured: Yes

SYSREF alignment error: No

rx_jesd lane 0 status:

Errors: 0

CGS state: DATA

Initial Frame Synchronization: Yes

Lane Latency: 1 Multi-frames and 73 Octets

Initial Lane Alignment Sequence: Yes

DID: 0, BID: 0, LID: 0, L: 2, SCR: 1, F: 4

K: 32, M: 4, N: 16, CS: 0, N': 16, S: 1, HD: 0

FCHK: 0x47, CF: 0

ADJCNT: 0, PHADJ: 0, ADJDIR: 0, JESDV: 1, SUBCLASS: 1

FC: 4915200 kHz

rx_jesd lane 1 status:

Errors: 1

CGS state: DATA

Initial Frame Synchronization: Yes

Lane Latency: 1 Multi-frames and 74 Octets

Initial Lane Alignment Sequence: Yes

DID: 0, BID: 0, LID: 1, L: 2, SCR: 1, F: 4

K: 32, M: 4, N: 16, CS: 0, N': 16, S: 1, HD: 0

FCHK: 0x48, CF: 0

ADJCNT: 0, PHADJ: 0, ADJDIR: 0, JESDV: 1, SUBCLASS: 1

FC: 4915200 kHz

tx_jesd status:

Link is enabled

Measured Link Clock: 122.865 MHz

Reported Link Clock: 122.880 MHz

Lane rate: 4915.200 MHz

Lane rate / 40: 122.880 MHz

SYNC~: deasserted

Link status: DATA

SYSREF captured: Yes

SYSREF alignment error: No

rx_os_jesd status:

Link is enabled

Measured Link Clock: 122.864 MHz

Reported Link Clock: 122.880 MHz

Lane rate: 4915.200 MHz

Lane rate / 40: 122.880 MHz

Link status: DATA

SYSREF captured: Yes

SYSREF alignment error: No

rx_os_jesd lane 0 status:

Errors: 0

CGS state: DATA

Initial Frame Synchronization: Yes

Lane Latency: 2 Multi-frames and 8 Octets

Initial Lane Alignment Sequence: Yes

DID: 0, BID: 0, LID: 0, L: 2, SCR: 1, F: 2

K: 32, M: 2, N: 16, CS: 0, N': 16, S: 1, HD: 0

FCHK: 0x43, CF: 0

ADJCNT: 0, PHADJ: 0, ADJDIR: 0, JESDV: 1, SUBCLASS: 1

FC: 4915200 kHz

rx_os_jesd lane 1 status:

Errors: 0

CGS state: DATA

Initial Frame Synchronization: Yes

Lane Latency: 2 Multi-frames and 6 Octets

Initial Lane Alignment Sequence: Yes

DID: 0, BID: 0, LID: 1, L: 2, SCR: 1, F: 2

K: 32, M: 2, N: 16, CS: 0, N': 16, S: 1, HD: 0

FCHK: 0x44, CF: 0

ADJCNT: 0, PHADJ: 0, ADJDIR: 0, JESDV: 1, SUBCLASS: 1

FC: 4915200 kHz

tx_dac: Successfully initialized (245730590 Hz)

rx_adc: Successfully initialized (122865295 Hz)

rx_obs_adc: Successfully initialized (245730590 Hz)

Done资源分享

整个项目最终文件与BOOT.bin

项目及BOOT.bin

链接:https://pan.baidu.com/s/1oxcjD2flhFfdV8PWVnOh_w

提取码:g31r

虚拟机镜像,内置vivado2018.3版本

链接:https://pan.baidu.com/s/13LNnIGnK-PFoAzuVh-1g-g

提取码:v06p

本文详细描述了如何在GitHub上下载必要的资源,设置Vivado环境,编译ADRV9371X项目,生成BOOT.bin文件,并将它加载到开发板的过程,包括虚拟机的使用和SDK操作步骤。

本文详细描述了如何在GitHub上下载必要的资源,设置Vivado环境,编译ADRV9371X项目,生成BOOT.bin文件,并将它加载到开发板的过程,包括虚拟机的使用和SDK操作步骤。

1644

1644

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?