目标

使用ZC706开发板上面的三个LED灯来做这个实验,完成一个静态区域控制LED0以1/4S的周期进行闪烁。两个动态区域实现LED2和LED3闪烁时间的动态配置。

过程

先看下ZC706 PL LED的电路原理图:

LED这里只用到了三个,直接接到了PL上。

再看下ZC706的时钟系统,主要目的是实现多块区域的重配置,因此选择一个最简单的全局时钟。

这下好了,想着是用一个简单的时钟,可惜除了PS时钟以外,全是差分时钟。(墨菲定律了)那就尝试下用差分时钟。

先写好约束文件:

#diff clock

set_property PACKAGE_PIN H9 [get_ports clk_p]

set_property IOSTANDARD DIFF_SSTL15 [get_ports clk_p]

set_property DIFF_TERM TRUE [get_ports clk_p]

set_property DIFF_TERM TRUE [get_ports clk_n]

#led0 1.5V

set_property PACKAGE_PIN G2 [get_ports led0]

#led1 1.5V

set_property PACKAGE_PIN A17 [get_ports led1]

#led2 2.5V

set_property PACKAGE_PIN W21 [get_ports led2]

set_property IOSTANDARD LVCMOS18 [get_ports led1]

set_property IOSTANDARD LVCMOS25 [get_ports led2]

set_property IOSTANDARD LVCMOS18 [get_ports led0]

对差分时钟只需要约束一个管脚就可以了,内部会自动识别到。

下面是顶层头文件:

module static(

input clk_p,

input clk_n,

output led0,

output led1,

output led2

);

parameter SYS_CLK = 200000000/4;

reg [32:0] cnt =32'b0;

wire clk;

IBUFGDS u_ibufds

(

.I(clk_p),

.IB(clk_n),

.O(clk)

);

always @(posedge clk)

begin

if(cnt > SYS_CLK)

cnt<=1'b0;

else

cnt<=cnt+1'b1;

end

assign led0 = (cnt>SYS_CLK/2)?1'b0:1'b1;

part1 u_part1

(

.clk(clk),

.led1(led1)

);

part2 u_part2

(

.clock(clk),

.led2(led2)

);

endmodule

差分时钟的引入需要用到 IBUFGDS,可以把它理解成一个差分时钟转成单端时钟的转换器。差分时钟是用来抵消外界的电磁干扰的,在芯片内部还需要转换成正常的单端时钟。

下面是画好的静态区域:

对于动态加载不懂的同学,可以看看我之前写过的zynq实现动态加载 里面有很清楚的描述。

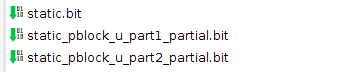

到这一步就可以生成bitstream了。完成以后,先看看目标文件夹中的内容:

可以看到一共有三个文件,第一个是静态分区+默认动态分区的bitstream文件。第二个和第三个分别是两个动态分区的文件。能看到这三个文件,我觉得这个实验已经成功了,所以写的时候看到这三个文件就开心的去做饭了☺。

回来验证一下刚才做的事情:

下载static.bit文件到开发板。

不过万万没想到,这一步花了一下午的时间。因为是第一次使用zc706开发板,而且也是第一次在linux环境下开发的。所以当调试器不能正常连接的时候,一直在找USB驱动的问题,忽略了开发板上的拨码开关,结果抱怨了一下午ubuntu 18.04。想到一件事情,最近腾讯官方出来QQ for Linux,体验了一下,结果是:QQ回到了当年的QICQ。这让我想到一个职场的画面,老马让手下出一个linux版本的QQ。老马认为这件事非常简单,不就是编译一个版本出来,结果QQ是用VS开发的,移植到Linux很麻烦,但是只拿了老马认为编译个版本的钱。所以最后事情做的很糟。结果老马认为他的手下做事不认真,他的手下确认为老马没有领导能力,不能看清开发的难度,自以为是。

这个问题怎么解决呢?假设有这么一个人,老马很信任他,他又很懂开发。这样就能很好的协调这种事情。这可能就是项目经理的重要性了。

ZC706 JTAG电路

为什么要把这个单列一节,想想是太大意了,再想想也不光是大意,因为第一次用zc706又是第一次用linux开发zynq,这就像是嵌入式开发中,软件硬件都有问题,你该怎么办☺

之前对嵌入式有个很好的形容,说软件开发和硬件开发的都像是在翻土,每一步都能看见效果,而且能够平稳的前进。但是搞嵌入式驱动就像是在破冰,可能一直没有动静,可能迎刃而解。介于这种情况嵌入式驱动工程师一定要保持头脑清醒。思路一定要开,但是还得专,你的每一个动作,必须要得出一个结论,来否定你之前的假设,知道你的假设成立。

看上图的SW4,直接决定了JTAG的链接方式;

10:platform usb

01:digilent

11:JTAG 20 PIN

这下清醒了,可以做最后的试验了。

分别下载上午搞定的三个文件,看到小灯如期的闪起来。好啦,本周结束。

结论

1、搞嵌入式最有意思的地方就是:你可能对一个现象有千万种想法,然后你开始用大量的时间,让自己只剩下对这个现象只有一种想法,这就是嵌入式工程师眼中的真理。

2、可以批判的看待Ubuntu、vivado、linux这些大型软件。但是一定有一个能经得住推敲的理由。不要因为自己搞不定或者是简单的猜想就说 “这个软件设计的真垃圾 搞不懂设计人员怎么想的”。

1654

1654

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?