最近要做一个核密度图,使用默认参数生成的图是矩形且核密度晕圈看起来很小,不够美观,通过一番学习,学会如何修改参数生成美观漂亮的图,现将操作方法整理出来,希望能对同学们有所帮助。

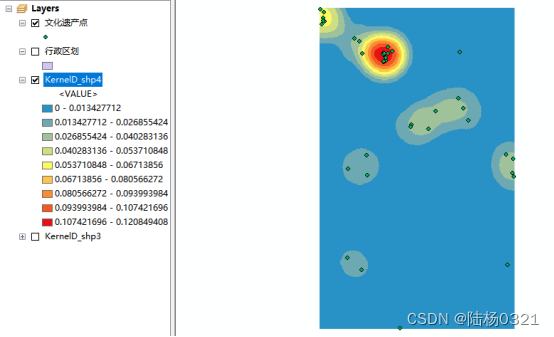

默认参数生成的核密度分布图

数据准备:

1.用于生成核密度的点图层数据,本次使用文化遗产点图层来做示例;

2.核密度指定导出范围,本次使用行政区划面图层来做示例;

操作步骤:

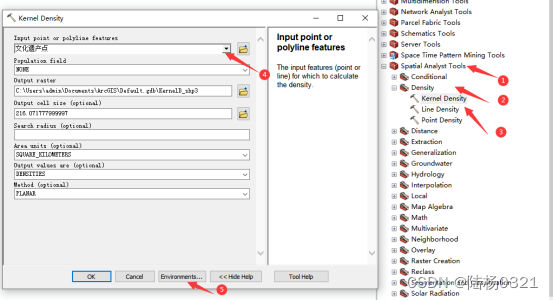

1.生成指定面范围

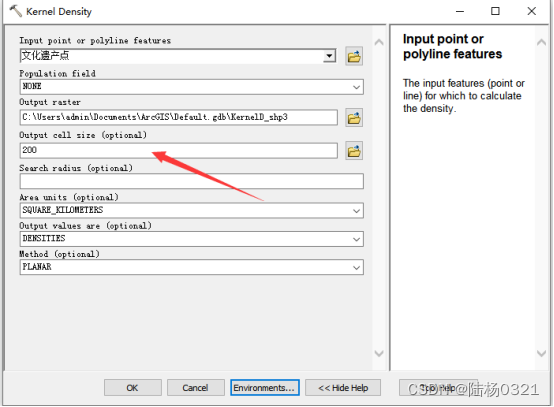

单击Spatial Analyst Tools(空间分析)——Density(密度分析)——Kernel Density(核密度)工具,弹出核密度工具框,在位置4输入需要做核密度分析的文化遗产点图层数据,如下图所示:

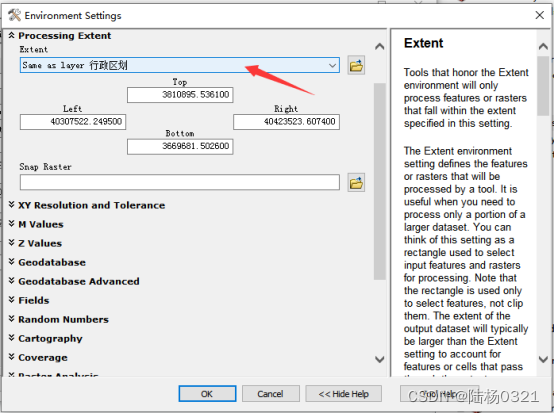

单击位置5环境,在弹出的环境框中Procession Extent(处理范围)——Extent(范围),选择“与行政区划图层相同”,如下图所示:

范围设置

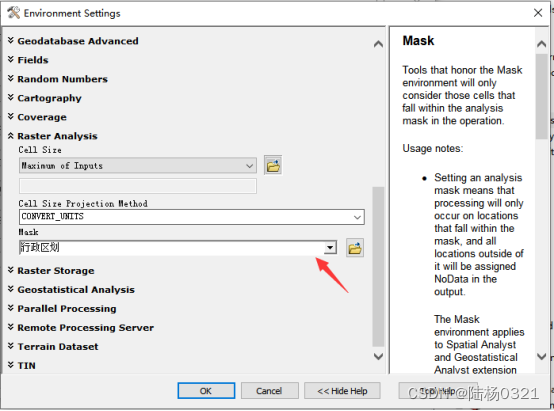

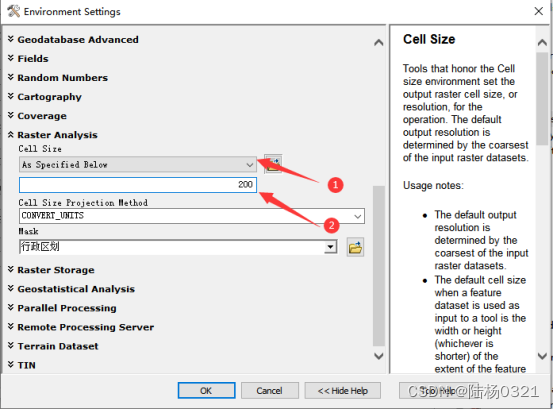

在弹出的环境框中Raster Analysls(栅格分析)——Mask(掩膜),选择“行政区划”,如下图所示:

掩膜参数设置

设置好参数后点ok可以直接回到“核密度”页面框。

2.指定像元大小

在弹出的环境框中Raster Analysls(栅格分析)——Cell Size(像元大小),选择“As Specified Below(如下面指定的数)”,在下面框中输入像大小,如下图所示:

像元参数设置方法1

像元设置好后,点ok,返回“核密度”页面框,在Output cell size(输出像元大小)显示像元已设置成功,也可以直接在这个位置修改像元大小,如下图所示:

像元参数设置方法2

3.样式设置

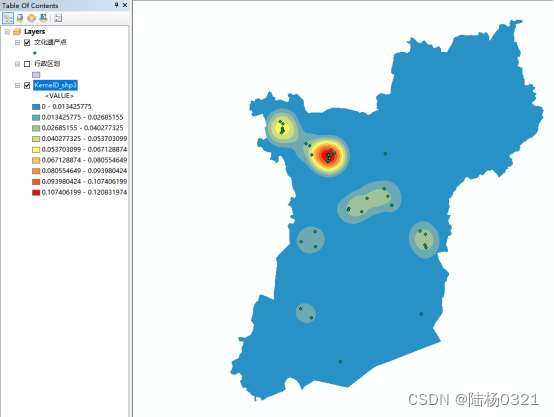

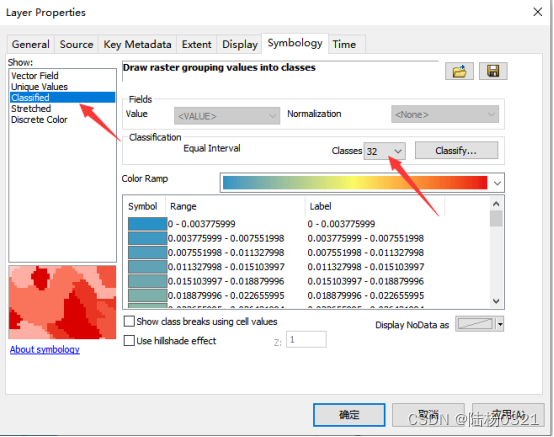

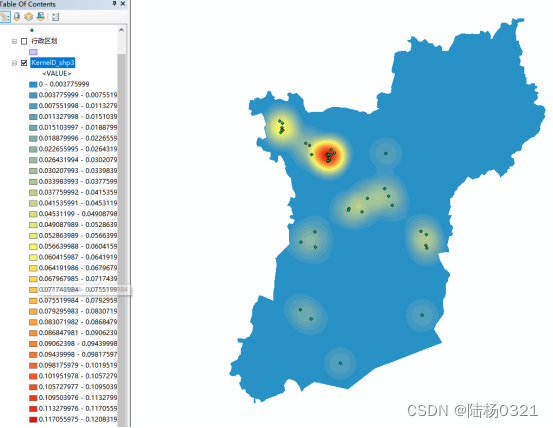

点击ok确定后,生成核密度图,如下图,生成的图默认是分为9类,从地图图示上看不太美观,我们可以从图层属性——符号设置,重新划分类数,分类越多图幅越美观。

调整样式前的核密度分布图

符号设置

调整样式后的核密度分布图

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?