目录

2.5 队列为空时的 JSQR 上下文队列示例( JQM=0 的情况)

2.6 队列为空时的 JSQR 上下文队列示例( JQM=1 的情况)

概述

本文主要介绍STM32H750外设ADC之注入转换的上下文队列的相关内容,包括配置上下文队列的方法,相关寄存器的功能介绍等。

1 注入转换的上下文队列

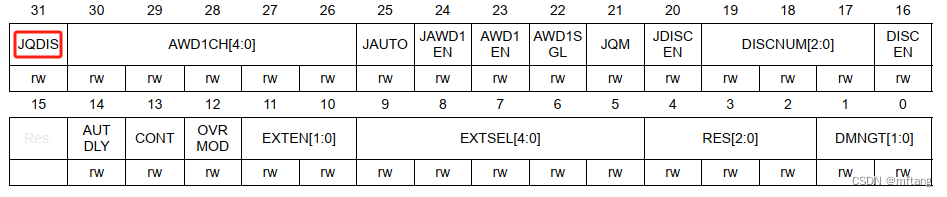

1.1 配置ADCx_CFGR 中JQDIS

实现上下文队列可为下一个注入转换序列准备多达 2 个上下文。必须将 ADCx_CFGR 寄存器的 JQDIS 位复位才能使能此功能。上下文队列使能时,只能进行硬件触发转换。

位 31 JQDIS:注入队列禁止 (Injected Queue disable)

这些位由软件置 1 和清零,用于禁止注入队列机制:

0:使能注入队列

1:禁止注入队列

注: 仅当 ADSTART=0 且 JADSTART=0 时(这可确保当前未进行常规转换、也未进行注入转换),才允许通过软件对此位执行写操作。将 JQDIS 位置 1 或复位会导致注入队列被清空, JSQR 寄存器也会被清空

1.2 注入触发ADCx_JSQR

该上下文包括:

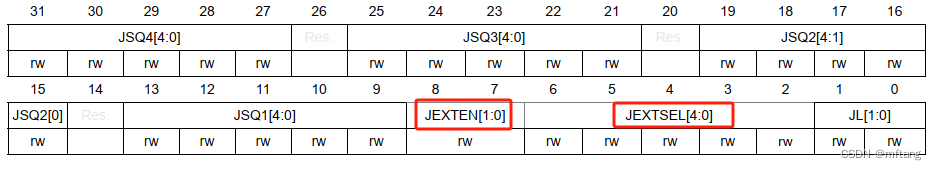

1)注入触发的配置( ADCx_JSQR 寄存器中的 JEXTEN[1:0] 位和 JEXTSEL[4:0] 位)

位 8:7 JEXTEN[1:0]:注入通道的外部触发使能和极性选择 (External Trigger Enable and Polarity Selection for injected channels)

通过软件将这些位置 1 和清零可选择外部触发极性和使能注入组的触发。

00:如果 JQDIS=0(队列使能),同时禁止硬件和软件触发检测

00:如果 JQDIS=1(队列禁止),禁止硬件触发检测(可通过软件启动转换)

01:在上升沿执行硬件触发检测

10:在下降沿执行硬件触发检测

11:在上升沿和下降沿都执行硬件触发检测

注: ADC 使能后 (ADEN=1),允许随时通过软件写入这些位。如果 JQM=1 且上下文队列为空,则会在内部禁止注入序列的软件和硬件触发位 6:2 JEXTSEL[4:0]:注入组的外部触发选择 (External Trigger Selection for injected group)

这些位可选择用于触发注入组转换的外部事件。

00000:事件 0

00001:事件 1

00010:事件 2

00011:事件 3

00100:事件 4

00101:事件 5

00110:事件 6

00111:事件 7

...

11111:事件 31:

注: ADC 使能后 (ADEN=1),允许随时通过软件写入这些位

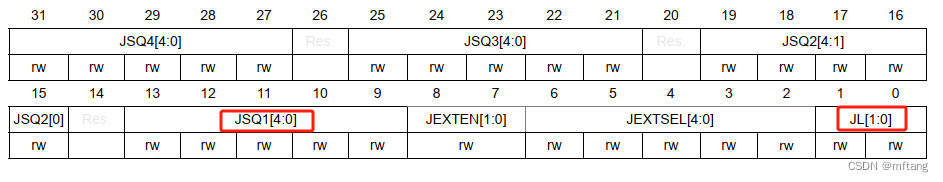

2)注入序列的定义( ADCx_JSQR 寄存器中的 JSQx[4:0] 位和 JL[1:0] 位)

位 13:9 JSQ1[4:0]: 注入序列中的第一次转换 (1st conversion in the injected sequence)

通过软件写入这些位,并将通道编号 (0..19) 分配为注入转换序列中的第一次转换。

注: ADC 使能后 (ADEN=1),允许随时通过软件写入这些位。

位 1:0 JL[1:0]: 注入通道序列长度 (Injected channel sequence length)

通过软件写入这些位可定义注入通道转换序列中的转换总数。

00: 1 次转换

01: 2 次转换

10: 3 次转换

11: 4 次转换

注: ADC 使能后 (ADEN=1),允许随时通过软件写入这些位。

1.3 ADCx_JSQR中的缓冲区

上下文的所有参数都会在 ADCx_JSQR 这一寄存器中定义,该寄存器会实现一个双缓冲区队

列,可缓冲多达 2 组参数。

1)JSQR 寄存器可随时写入,正在进行注入转换时也不例外。

2)每个写入到 JSQR 寄存器中的数据均会存储在上下文队列中。

3)队列开始时为空,对 JSQR 寄存器进行的第一次写访问时会立即更改上下文,随即 ADC会准备好接收注入触发。

4)注入序列完成后,队列会被占用,上下文会根据队列中存储的后续 JSQR 参数进行更改。这一新的上下文会用于下一个注入转换序列。

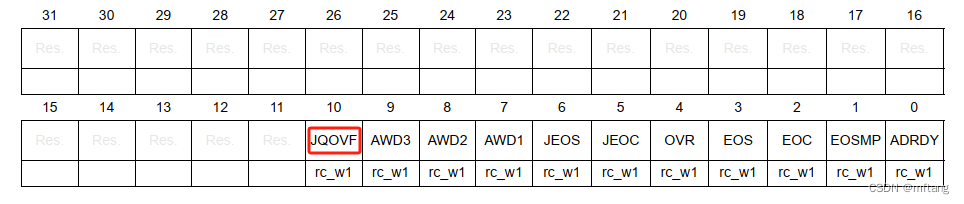

5)如果在队列已满的情况下向 JSQR 寄存器执行写操作,会发生队列溢出。这种溢出情况会通过 JQOVF 标志置为有效来指示。发生溢出时,会忽略造成溢出的 JSQR 寄存器写访问,并且上下文队列保持不变。如果 JQOVFIE 位置 1,可产生中断。

ADC x 中断和状态寄存器 (ADCx_ISR)( x=1 到 3)

ADC x interrupt and status register

偏移地址: 0x00

复位值: 0x0000 0000位 10 JQOVF:注入上下文队列溢出 (Injected context queue overflow)

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

692

692

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?