slave从OUT FIFO中拿到data后(阻塞语句),放到总线上,然后等待preadyDelay规定的cycle后将pready有效。pready有效后,可以随机撤销或者保持1的状态。

slave从mem中拿到data后,放到总线上,然后等待preadyDelay规定的cycle后将pready有效。pready有效后,可以随机撤销或者保持1的状态。

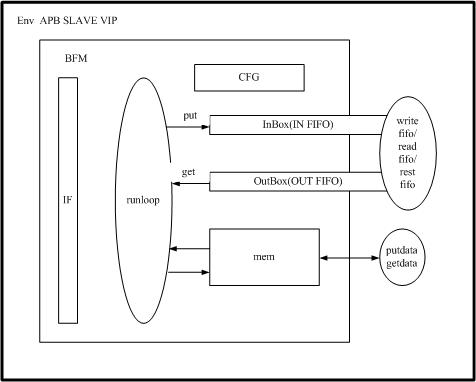

env中提供了访问InBox mailbox, 和 OutBox mailbox的函数,以及访问mem的函数,当然包括一些用于配置的函数。

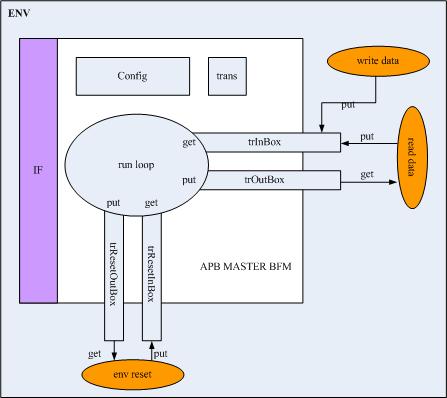

下面介绍一下master的blockdiagram

补充说明:

在各个task的定义时,第一个动作便是ClockAlign

task clockAlign();

wait(sync_posedge.triggered);

endtask时间的消耗也可以采用如下方式,mailbox.peek(tr).

总结:

在写bus function model时,salve model通常会有一块internal memory。 通常需要InBox和OutBox这样的mailbox来实习BFM和外界ENV的通信。ENV中一般用read write函数实现mailbox的通信。当然视情况,某些情况下你也可以用depth为

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

743

743

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?