根据SV标准手册《IEEE Standard for SystemVerilog》ASSERTION章节整理出SVA的基本概念,并加以个人理解,记录于此,以便回顾。

1. assertion types

| Assertion Types | ||

| immediate | simple | assert (expression) |

|

|

| assume (expression) |

|

|

| cover (expression) |

|

| defered | assert #0 | final (expression) |

|

|

| assume #0 | final (expression) |

|

|

| cover #0 | final (expression) |

| concurrent |

| assert property (property_spec) |

|

|

| assume property (property_spec) |

|

|

| cover property (property_spec) | sequence (expression) |

|

|

| restrict property (property_spec) |

| others |

| expect (property_spec) |

| Assertion Type Items Definition | |

| assertion | 断言描述系统行为,主要用于“”验证系统行为“”,也能用于“提供功能覆盖率以确认激励没有违反要求”。

理论上,用verilog也可以实现断言,但是由于其抽象层次不高,编写代价会很大。不同公司可以编写自己的一套断言基本单元,这犹如造车轮,原理简单,工作繁琐,容易出错,不便统一。所以,我们需要一套共通的、抽象层次更高的语法,SV断言的前身由此诞生。SV的发明者,正是V的发明者。

断言是从软件测试中沿用过来的一个概念,正如class也是从软件沿用过来的一样。因此,验证工程师真的算是半个码农、半个硅农。 |

| immediate | 立即断言,遵循仿真时间语义,执行起来像过程快,主要用于仿真验证 |

| concurrent | 并发断言,基于时钟语义,对表达式进行采样。为不同的设计、验证工具提供共通的语义,如形式验证工具、仿真验证工具。 |

| simple | 断言发生,指令立即执行,like "if" |

| defered | 断言发生,指令延迟执行 |

| assert | 仿真工具:检查规则 形式验证:检查规则 |

| assume | 仿真工具:检查规则 形式验证:假设前提,用于产生激励 |

| cover | 仿真工具:覆盖率统计 形式验证: |

| restrict | 仿真工具: 形式验证:约束限制 |

| expect | allows waiting on a property evaluation,similar to "wait" |

immediate assertion

deferred immediate assertion 可用于抑制毛刺导致的假报告,且可以被多个程序块同时调用,故感觉比simple immediate assertion 更适用于组合逻辑功能检查。 defer有两种,#0 适用于组合逻辑信号之间的检查,final适用于含组合逻辑信号与触发器信号的检查。理解defer,就是理解flush point,需要先理解verilog simulation regions。

concurrent assertion

concurrent --> clock sample --> expression --> sequence --> property --> assertion (sample 时钟沿之前)

详见16.14,后续补充

16.14.1 Assert statement

16.14.2 Assume statement

16.14.3 Cover statement

16.14.4 Restrict statement

16.14.5 Using concurrent assertion statements outside procedural code

16.14.6 Embedding concurrent assertions in procedural code

16.14.6.1 Arguments to procedural concurrent assertions

16.14.6.2 Procedural assertion flush points

16.14.6.3 Procedural concurrent assertions and glitches

16.14.6.4 Disabling procedural concurrent assertions

16.14.7 Inferred value functions

$inferred_clock

$inferred_disable

16.14.8 Nonvacuous evaluations

2. boolean expression

断言的本质是逻辑推理,逻辑值在时间上排列组合,形成sequence,再组合形成property。所以,布尔表达式是组成断言的原子。

boolean expression在断言中可以出现在很多地方,除了sequence、clocking event、disable iff等,在sequence中是clock based sample。

3. sequence

sequence operation

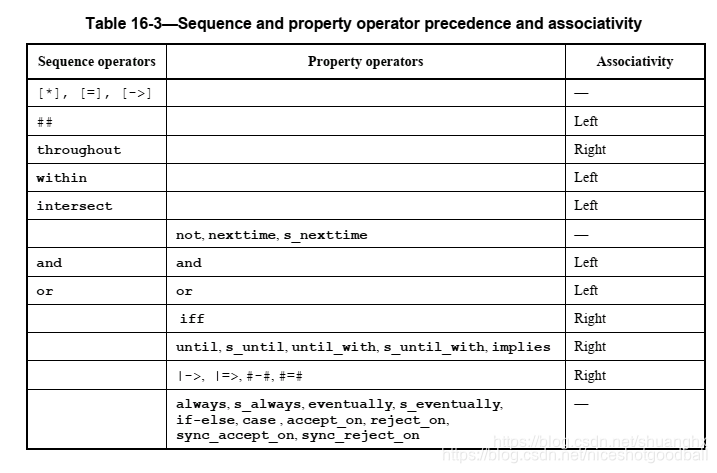

property刻画系统的行为(特性),通常是时序行为。时序行为的基本组件是sequence,通过sequence operation得到比sequence复杂的行为,即property。sequence operation 是SVA的强大优势,相比于用Verilog实现相同功能,更加简洁容易,因为它具有更高的抽象层级。

local variable

subroutines

断言的本质是“检查系统行为“,更具体来说就是“匹配sequence”。验证工具的首要工作是匹配sequence,此外还能顺带做一些运算、判断,来增强其检查能力。要再匹配sequence的过程中兼备运算、判断能力,就需要variable,and then subroutines。

| declaration formal argument | sequence | 略 |

| event | 略 | |

| untyped | 略 | |

| local variable | 略 | |

| delay | ##m ##[m:n] $ ##[ *] ##[+] | 略 |

| repeat | [* m:n] $ [*] [+] | (a ##2 b)[*1:5] is equivalent to (a ##2 b) |

| [->] | a ##1 b [->2:10] ##1 c is equivalent to a ##1 ((!b[*0:$] ##1 b) [*2:10]) ##1 c | |

| [=] | a ##1 b [=2:10] ##1 c is equivalent to a ##1 ((!b [*0:$] ##1 b) [*2:10]) ##1 !b[*0:$] ##1 c | |

| sample vale function | $sample | 比直接采用变量更准确,涉及到simulation regions: reactive regions |

| $rose $fell | 略 | |

| $stable $changed | 略 | |

| $past | 略 | |

| $rose_gclk ... | 略 | |

| $rising_gclk ... $future_gclk | 略 | |

| operate | and | 起点相同 |

| intersect | 起点终点相同(与and相似) | |

| or | 略 | |

| first_match | 略 | |

| dist throughout | (exp) throughout seq is equivalent to (exp) [*0:$] intersect seq

| |

| within | seq1 within seq2 is equivalent to (1[*0:$] ##1 seq1 ##1 1[*0:$]) intersect seq2 | |

| method | triggered | 利用序列终点来构造更复杂的序列 (用intersect也能实现同样的功能,需要适当调整序列起点之间的间隔范围,稍微麻烦,不够直观方便而已,仿真效率可能也会低一点)

|

| local variables | local variables | (a[->1], x += data)[*4] ##1 b ##1 c && (data_out == x); 变量可以传出sequence给上层环境使用,也可在sequence property内部使用。 |

| call sub-routines | call sub-routines | (b[->1], w = f, $display("b after a with v = %h, w = %h\n", v, w)); |

4. property

断言的本质是,检查系统行为。

| property_declaration | property property_identifier [ ( [ property_port_list ] ) ] ; | 16.12.20 Property examples |

| property_spec | [clocking_event ] [ disable iff ( expression_or_dist ) ] property_expr | 略 |

| property_expr | strong ( sequence_expr ) weak ( sequence_expr ) | 略 |

| not and or | 略 | |

| |-> |=> | sequence_expr |=> property_expr is equivalent to the following: | |

| #-# #=# | 后续补充 | |

| if else case endcase | 略 | |

| implies iff | 略 | |

| nexttime s_nexttime always s_always eventually s_eventually until s_ until until_with s_until_with | 后续补充 | |

| accept_on reject_on sync_accept_on sync_reject_on | 后续补充 |

| 其他系统函数(不全) | ||||

| $fatal | $error | $warning | $info |

|

| $assertoff | $asserton | $assertkill |

|

|

| $onehot | $onehot0 | $isunknown | $countones |

|

5. clock resolution

multiclock

clocking blocks

如果说逻辑的原子是布尔表达式,那时序的原子就是clock。逻辑、时序是sequence的两个组成维度,布尔表达式、时钟是并发断言的两种元素。

| clock | Multiclock | Multiclock sequence sequence mult_s;

Property with a multiclock sequence property mult_p1;

Property with multiclock implication property mult_p3;

sequence_instance.matched |

| Clock resolution | 后续补充 | |

| clocking block If a variable used in a concurrent assertion is a clocking block variable, it will be sampled only in the | Examples: clocking cb_with_input @(posedge clk); |

6. disable iff resolution

在系统中,除了时钟,还有一个信号非常重要,那就是复位。在复位期间,数据无效,行为无效,检查无效,故断言无效。由此,我们需要一种断言的disable机制。这种机制就是disable iff, 它的建模方式和RTL设计中复位信号的建模方式很像,很简单。

| disable iff (reset) | disable iff resolution | 后续补充 |

7. expect

| expect | expect | expect ( property_spec ) action_block |

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?