原文:https://blog.csdn.net/zhuzongpeng/article/details/76136110

一、故事前传

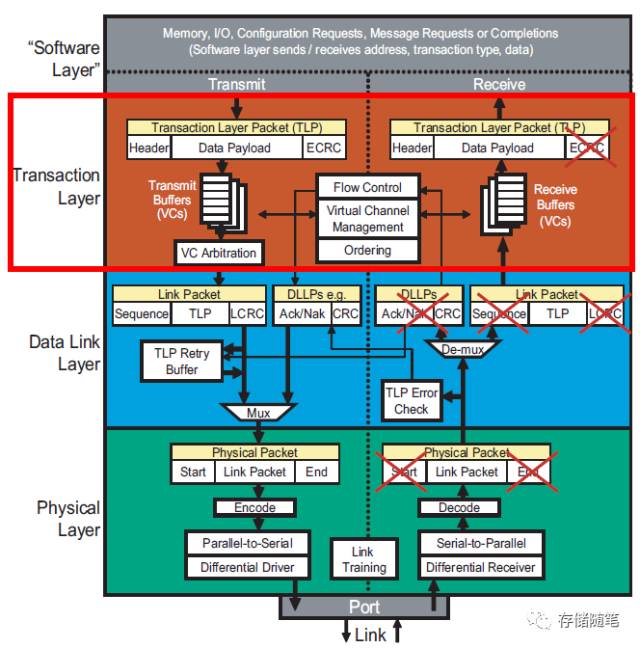

上回我们对PCIe的一些基础概念作了一个宏观的介绍,了解了PCIe是一种封装分层协议(packet-based layered protocol),主要包括事务层(Transaction layer), 数据链路层(Data link layer)和物理层(Physical layer)。

较为详细解释请见之前的文章:PCIe技术概述;

二、事务层概述

在PCIe体系结构中,数据报文首先在设备的核心层(Device Core)中产生,然后再经过该设备的事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer),最终发送出去。而接收端的数据也需要通过物理层、数据链路和事务层,并最终到达Device Core。

事务层是PCIe总线层次结构的最高层,该层次将接收PCIe设备核心层的数据请求,并将其转换为PCIe总线事务,PCIe总线使用的这些总线事务在TLP头中定义。

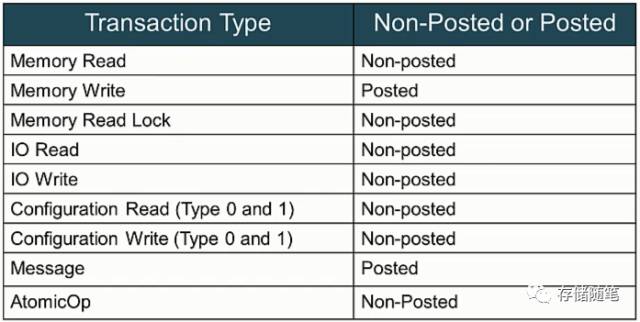

PCIe总线继承了PCI/PCI-X总线的大多数总线事务,如存储器读写(Memory Read/Write)、I/O读写、配置读写总线事务,并增加了Message总线事务和原子操作等总线事务。

扩展:PCIe中有两大类总线事务:Non-Posted和Posted:

Non-Posted: 需要completion返回响应包;

Posted: 不需要completion返回响应包.

在PCIe总线中,Non-Posted总线事务分两部分进行,首先是发送端向接收端提交总线读写请求,之后接收端再向发送端发送完成(Completion)报文。PCIe总线使用Split传送方式处理所有Non-Posted总线事务,存储器读、I/O读写和配置读写这些Non-Posted总线事务都使用Split传送方式。

PCIe的事务层还支持流量控制(Flow control)和虚通路管理(Virtual Channel Management)等一系列特性,而PCI总线并不支持这些新的特性。

在PCIe总线中,不同的总线事务采用的路由方式不相同。PCIe总线使用的数据报文首先在事务层中形成,这个数据报文也被称之为事务层数据报文,即TLP,TLP在经过数据链路层时被加上Sequence Number前缀和CRC后缀,然后发向物理层。

本篇文章主要是对PCIe的事务层作一个大致的表述,后续章节会针对事务层主要的功能TLP, Flow Control, Transaction Ordering等内容进行详细的介绍,敬请期待!

2843

2843

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?