本文只是做个记录,脑子不好容易忘记。

重点参考几个ARM手册:

| 手册 | 链接 |

|---|---|

| DDI0489F_cortex_m7_trm.pdf | https://developer.arm.com/documentation/ddi0489/f/?lang=en |

| DUI0646B_cortex_m7_dgug-20240202.pdf | https://developer.arm.com/documentation/dui0646/c/?lang=en |

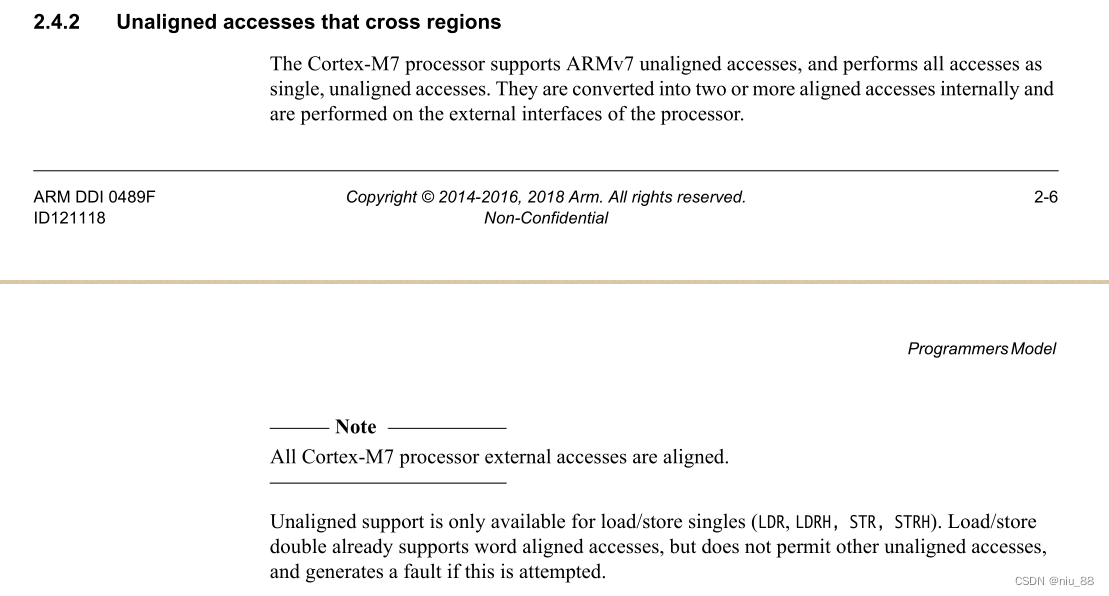

Cortex-M7是支持地址非对齐访问的,但是使用时还是需要多注意细节之处的。

几个重要指令:LDR、LDRH、STR、STRH。

非对齐访问中断

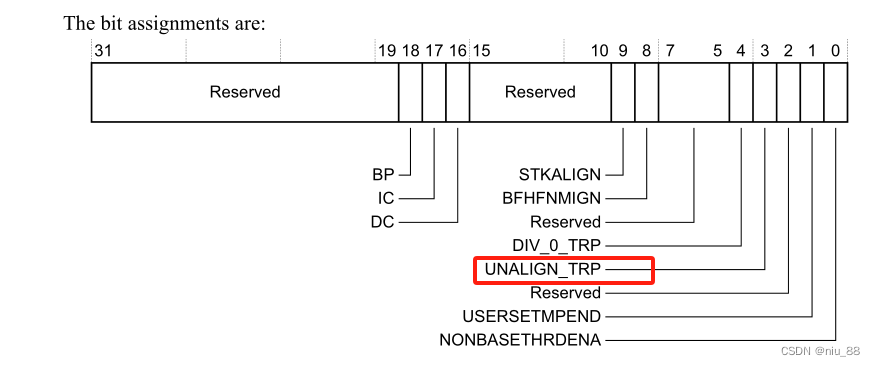

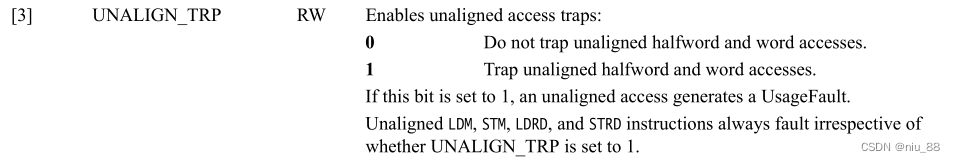

Configuration and Control Register:

当前寄存器的bit无论使能与否,都会产生中断错误,只是产生错误的中断是HradFault还是UsageFault。

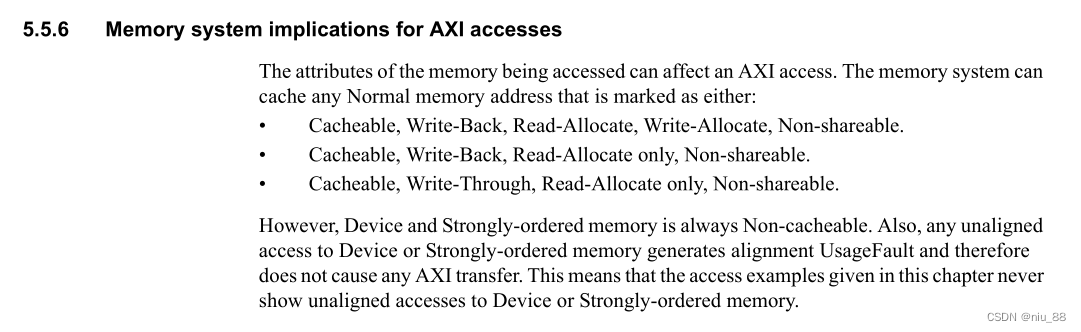

Memory类型

Memory分为三大类:

- Normal

- Device

- Strongly-ordered

类型可以由MPU来配置属性,如果属性为Normal则支持地址非对齐访问;如果属性为Device或Strongly-ordered,则禁止非对齐访问,一旦非对齐访问,则进入HardFault或UsageFault错误中断。

编译选项

- -mno-unaligned-access

这个选项告诉编译器不要生成任何非对齐的内存访问指令。这通常是一个安全的选项,但可能会导致性能下降,因为编译器会避免任何可能导致非对齐访问的代码。 - -munaligned-access

这个选项告诉编译器可以生成非对齐的内存访问指令。这可以提高性能,但也可能增加硬件异常的风险,特别是在不支持非对齐访问的硬件上。

没有设置上述两个参数情况下,由编译器的版本默认配置参数。

当使用“-mno-unaligned-access”,在编译时,会将地址非对齐情况下的代码进行优化,将“str”命令转为“strb”,以避免对齐问题。如:

test_a a;

a.a = 9;

800093a: 2309 movs r3, #9

800093c: 607b str r3, [r7, #4]

a.b = 2;

800093e: 2302 movs r3, #2

8000940: 723b strb r3, [r7, #8]

a.c = 3;

8000942: 2300 movs r3, #0

8000944: f043 0303 orr.w r3, r3, #3

8000948: 727b strb r3, [r7, #9]

800094a: 2300 movs r3, #0

800094c: 72bb strb r3, [r7, #10]

800094e: 2300 movs r3, #0

8000950: 72fb strb r3, [r7, #11]

8000952: 2300 movs r3, #0

8000954: 733b strb r3, [r7, #12]

861

861

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?