DDR3基础简介

DDR3 SDRAM(double-data-rate 3 synchronous dynamic RAM)即第三代双倍数据速率同步动态随机存储器。

关键技术

Prefetch 预取

DRAM内部存储单元的核心频率提高比较困难且成本较高,引入 prefetch 来保障数据传输速率的增长。本质上是并串转换,通过并行方式提前取得数据再串行输出,从而提升数据传输速率。

在DDR3中采用8-bit prefetch或8-n prefetch(n代表芯片位宽),从而使实际数据传输速率为核心频率的8倍。

芯片位宽的另一种说法是配置模式(Configuration),在DDR3时代,一般有x4,x8,x16

当DDR3 为x8 Configuration时,一个Cell的容量为8x8bits,即8个字节。换一句话说,在指定bank、row地址和col地址之后,可以往该地址内写入(或读取)8 Bytes。

http://blog.chinaaet.com/justlxy/p/5100052027blog.chinaaet.com/justlxy/p/5100052027

Burst 突发传输

Burst(突发)是指在同一行中相邻的存储单元连续进行数据传输的方式。

Burst Lengths(突发长度,简称BL)指连续传输所涉及到存储单元(列)的数量就是突发长度。

在DDR3 SDRAM时代,内部配置采用了8n prefetch(预取)来实现高速读写。这也导致了DDR3的Burst Length一般都是8。当然也有Bursth ength为4的设置(BC4),是指另外4笔数据是不被传输的或者被认为无效。

示例:MT41K256M16xx-125

以MT41K256M16 为例,其命名规则如下:

时钟频率与带宽

关于DDR的时钟频率相关参数主要有如下三种:

- core freq: 核心频率,用于DDR内部cell(存储单元)的时钟

- clock freq:时钟频率,用于DDR的IO buffer的时钟,同时也是IO接口时钟,是通过核心频率倍频4倍得到

- data bus/rate:数据速率,单根数据线的数据传送次数

他们之间的关系如下:

从 part number 中的 speed 选项可知,-125 所支持的最小时钟周期 tCK = 1.25ns,对应芯片支持的最大 IO 时钟频率为 800MHz。

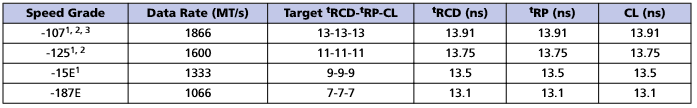

不同速度等级对应的时间参数如下:

表中 data rate 为单数据线的数据速率,DDR为双边沿传输,因此 -125 对应 1600 MT/s(Mega Transfers/s),有时也对应称此内存为 DDR3-1600

那么这片16位数据线内存的带宽为:

1600MT/s∗16bit=25600Mbit/s=3200MB/s

在实际应用确定DDR3工作频率时,除了DDR3本身时钟速率的限制,我们还需要考虑控制器所能支持的输出频率。例如,MT41K256M16是支持1.35V(DDR3L)和1.5V(DDR3)两个电平标准,当我们用 Xilinx K7的FF封装FPGA芯片作为控制器时,参考 DS182 手册查看支持的最高速率:

采用不同bank类型以及电压均对支持的最大速率有影响

地址及容量计算

所对应的功能框图如下:

MT41J256M16拥有18根地址线和16跟数据线:

| 端口 | 类型 | 描述 |

|---|---|---|

| BA[2:0] | I | 地址线:Bank地址选择,模式寄存器选择 |

| A[14:0] | I | 地址线:复用行列地址线 |

| DQ[15:0] | I/O | 数据线 |

在DDR4往后,开始有BANK GROUP概念,BANK被划分为两组BANK GROUP,由BG0进行控制,此时BA变为两位。并且地址线A中拥有1位专用于区分行地址和列地址。可参考: https://blog.csdn.net/u012489236/article/details/107730731

从DDR的命名中可以知道:MT41J256M16 是一片 256M*16 bit = 4 Gb 容量的内存。4Gb 这个系列根据颗粒大小的参数区别如下:

DDR3的内部是由8个逻辑 bank 组成,如下所示

每个bank类似于一个表格,通过指定行与列来确定具体的存储单元。DDR3通过分时复用的方式,将有限的地址线能够寻址更大的容量。

对于DDR3还有物理 bank 概念(即 rank),rank 针对于系统而非内存本身。内存为了保证CPU正常工作,必须一次传输完CPU在一个传输周期内所需总线位宽的数据。目前这个位宽通常为64 bit,如果DDR3有128 bit地址线,则为2个rank。

关于容量的计算

在1个bank中,有15位行地址与10位列地址,数据宽度为16位(每个存储单元为16bit)。

- 行地址容量为:2^15 = 32K

- 列地址容量为:2^10 = 1K

- 每个bank的地址总容量为:32K * 1K = 32 M,即 configuration 中对应的 32 Meg

- DDR总地址容量为:32M * 8 = 256 M,即名称中的 256 Meg

- 每行的存储容量为:1K * 16 bit = 16 Kbit = 2 KB,称为 page size

我们对应功能框图中的一个bank容量标识:

(行地址)(列地址)(数据宽度预取)32768(行地址)∗128(列地址/8)∗128(数据宽度∗8 bit预取)

列地址/8与突发传输有关,对于DDR3一般突发长度为8(对应8-bit prefetch),每次传输8列的数据,因此列地址只需要原来的八分之一。

从功能框图也可以看到,列地址寻址范围为 2^7,只有7bit用于了列地址译码:

列地址的低三位 A[2:0]以及 A[3] 被用作 burst 读写中地址顺序的规定:

比如一次Burst Read的时候如果CA[2:0]=3’b001表示低三位从地址1开始读取, - CA3=0的时候按顺序读取1,2,3,0,5,6,7,4,

- CA3=1的时候为交错读取1,0,3,2,5,4,7,6。

对于Prefetch而言,正好是8N Prefetch,对于Burst而言对应BL8。BC4其实也是一次BL8的操作,只是丢弃了后一半的数据。

引脚说明

为了更好的认识,可以将DDR3的数字引脚按照功能分类为:控制组,地址组和数据组三类

控制组

所有带#信号均为低电平有效

| 名称 | 功能 | 描述 |

|---|---|---|

| CK,CK# | 差分时钟输入 | 所有控制和地址输入信号在CK上升沿和CK#的下降沿交叉处被采样,输出数据选通(DQs,DQS#)参考与CK和CK#的交叉点。 |

| CKE | 时钟使能 | 内部时钟使能信号 |

| CS# | 片选 | CS#为低时DDR芯片使能,CS#的参考值是VREFCA |

| RAS# | 行地址 | 行地址标识信号,其参考值是VREFCA |

| CAS# | 列地址 | 列地址标识信号,其参考值是VREFCA |

| WE# | 读写 | 低电平表示写,高电平表示读操作,其参考值是VREFCA |

| RESET# | 复位 | 参考值是 VSS |

| ODT | 片上终端使能 | 在正常操作使能时,ODT仅对:DQ[7:0]、DQS、DQS#和DM引脚有效。如果通过LOADMODE命令禁止,ODT输入被忽略。ODT的参考值是VREFCA。 |

| ZQ# | 外部校准 | 输出驱动校准的外部参考,这个引脚应该连接240欧姆电阻到VSSQ。 |

CS#,RAS#,CAS#和WE#可以构成命令组,它们将在时钟的上升沿被采用,在DDR手册中可以查看对应的真值表。

地址组

| 名称 | 功能 | 描述 |

|---|---|---|

| A[14:0] | 地址总线 | 为 ACTIVATE命令提供行地址 为 READ/WRTE 命令提供列地址和自动预充电位(A10),以便从某个Bank的内存阵列里选出一个位置。 LOAD MODE命令期间,地址输入提供一个操作码。地址输入的参考值是 VREFCA |

| BA[2:0] | bank选通 | 确定要操作的Bank,参考值是VREFCA |

数据组

| 名称 | 功能 | 描述 |

|---|---|---|

| DQ | 数据总线 | 双向总线 |

| DQS,DQS# | 数据选通 | 用于数据同步: 读时是输出,边缘与读出的数据对齐。 写时是输入,中心与写数据对齐。 |

| TDQS,TDQS# | 数据选通 | 功能与DQS相同,只是当两种不同的DIMM混合应用在同一个系统时,DQS的负载就会不同,这样会造成信号完整性问题,TDQS就是为了解决这个问题的。 当TDQS使能时,DM必须禁止,TDQS和TDDS提供终端电阻。 |

| DM | 数据屏蔽 | DM是写数据的输入屏蔽信号,在写期间,当DM信号被采样为高时,输入数据被屏蔽。 虽然DM仅作为输入脚,但是DM负载被设计成与DQ和DQS脚负载相匹配。DM的参考值是 VREFCA。 注意: DQS与DM共用一个物理引脚,所以DM可选作为TDQS。 |

DDR操作

命令模式

其中V表示逻辑电平H或L。

DES & NOP

DES(取消选择)和NOP(无操作)命令比较类似:

- DES防止DRAM执行新命令

- NOP防止不需要的命令在空闲或等待期间执行

对于已经进行的操作两者都不会影响

ZQCL & ZQCS

ZQCL(ZQ校准长)和ZQCS(ZQ校准短)都用于校准,区别在于:

- ZQCL用于上电初始化和复位序列期间执行初始校准,校准完成后会更新RON和ODT值。

- ZQCS用于执行定期校准来解决电压和温度的小变化,在64个时钟周期内完成校准

ACT

ACT(启用)用于打开(或激活)特定bank中的行以便后续访问。在此期间该行将保持打开(或活动)直到该bank发出PRECHARGE命令。打开同一bank中不同行之前必须执行PRECHARGE命令。

PRE & PREA

PRECHARGE(预充电) 命令⽤于取消激活特定 bank 中的打开或全部 bank。bank 在发出预充电命令的 tRP 时间后可以继续访问后续行。

bank 在预充电后处于空闲状态,在任意读操作之前必须激活(ACT)bank或发出写命令(WR)。

RD

READ命令用于启动对话行的突发读取访问。

- 输⼊ A[2:0] 以及突发顺序表选择起始列地址。

- 输⼊ A[10] 上的值决定是否使⽤⾃动预充电。如果选择了⾃动预充电,则正在访问的行将在 READ 突发结束时进行预充电,否则该行将保持打开状态以供后续访问。

- 输入 A[12] 上的值(如果模式寄存器启用)决定使用BC4(0)或BL8(1)

WR

WRITE 命令⽤于启动对活动行的突发写⼊访问。

- 输入 BA[2:0] 值决定选择 bank,地址 A 的作用与 RD 相似

- 出现在 DQ 上的输⼊数据被写⼊受 DM 输⼊影响,如果给定的 DM 信号为低电平,数据将被写入内存,反之数据将被忽略。

REF

REFRESH(刷新) 命令在 DRAM 正常运行期间使⽤,与地址位无关,平均间隔为7.8us。最多可以将⼋个 REFRESH 命令发布到任何 给定的 DRAM。

SRE & SRX

SELF REFRESH(自刷新) 命令⽤于在 DRAM 中保留数据,DRAM ⽆需外部时钟即可保留数据。

write leveling

为了更好的信号完整性,DDR3 SDRAM 内存模块对命令、地址、控制信号和时钟采⽤了 fly-by 拓扑。Fly-by拓扑能有效减少stub的长度,但是较长的走线带来了CK-CK#与DQS-DQS#间的时延(由于CK-CK#的飞行时间,其到达每个DDR3颗粒的时间不同,而DQS-DQS#通常为点到点拓扑)。

write leveling(写均衡)通过 DRAM 提供的简单反馈功能调整或消除 DRAM 上的 DQS 选通脉冲(DQS、DQS#)与 CK 的关系。

Wrtie leveling 是一个完全自动的过程。CPU 不停的发送不同时延的DQS 信号,DDR3 SDRAM 颗粒在DQS-DQS#的上升沿采样CK 的状态,并通过DQ 线反馈给DDR3 控制器。控制器端反复的调整DQS-DQS#的延时,直到控制器端检测到DQ 线上0 到1 的跳变(说明tDQSS参数得到了满足)。控制器就lock 住此时的delay value。此时便完成了一个Wrtie leveling过程。

Leveling 过程中,DQS-DQS#从控制器端输出,所以在DDR3 SDRAM 侧必须进行端接;同理,DQ 线由DDR3 SDRAM 颗粒侧输出,在控制器端必须进行端接;

系统状态机

2755

2755

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?